## Outline - Tuesday 20th of January

- Practical issues

- Learning goals

- Design project, tools and methods

- Syllabus

- Very brief introduction to various circuit building blocks (sample-and-holds, bandgap references, switched capacitor circuits, Nyquist- and oversampling data converters, phase-locked loops)

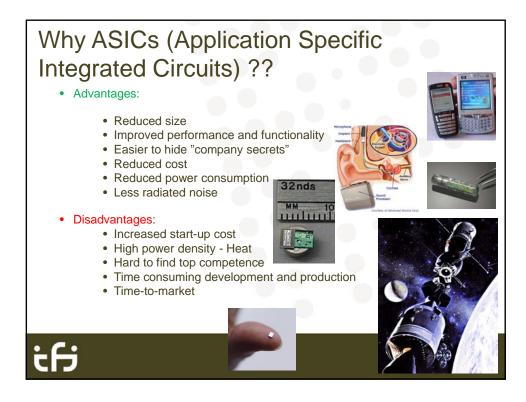

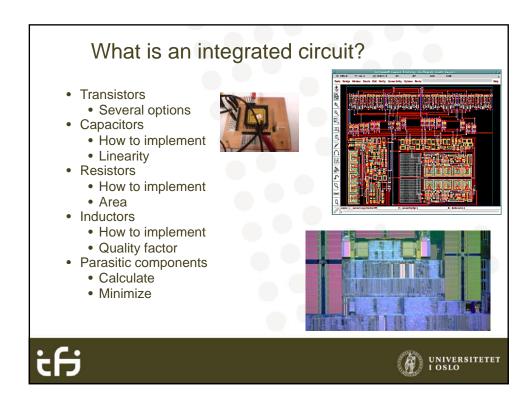

#### **CMOS Integrated Circuits?**

Digital circuits exploit mainly transistors and interconnect

- Mixed-Signal (Digital AND Analog) also use resistors, capacitors and inductors

- Work-horse of modern Information Technology

# Mandatory design project

- Design and implement mixed-mode circuit:

- Example: ADC, SC-filter, PLL, DAC (2008)

- System for automatic removal of mismatch (2009)

- Milestones during the process

- Teaching assistant, Amir Hasanbegovic, will follow up

- Write a project report

- LaTeX or similar

- Submission: Early/Mid May

- Counts 40 % in the final grading (exam 60%)

#### Challenge in 2008: Digital-to-Analog Converter ("DAC")

INF 4420 - Prosjektoppgave: Digital til Analog

#### 1 Introduksjor

Det skal lages en data-konverter av typen "Twe-stage balanced current DAC illustrert i figur lengre ned.

- DAC'en skal ha en oppløsning tilsvarende minimum 6 bi

- Anta i utgangspunktet at maksimalt et en spenningsreferanse og e strømkilde er tilgjengelig, og dermed ikke trenger konstrueres.

- Digitalt ord inn (unipolart) skal være på følgende form, forutsatt 6 bi oppløsning: 00...0. 00...1, ..., 11...1.

- Utgangssignalet skal være nedad begrenset til 0.3 V og oppad begrense til 0.7 V.

- Positiv forsyninsspenning ("Vdd") er 1.0 V. Negativ forsyningsspenning ("Vss") er 0 V.

- Maksimal DNL: +/- 1 LSB

- Kiretsen slik den er i kretsskjema mangler buffer, for eksempel i form av en sperningsfølger, som gjer den i stand til å drive en kupsaitst latat i for av i/O-celle ("pad"). Det er frivillig evt å lage et slikt buffer, ikke-påkrevi

#### Milepæler

For å sikre gjennomføring innenfor tidsrammen settes det delmål med oppgit finster. Studentene har ansvaret for å få disse delmålene godkjent av

11/3-08 Det skal leveres inn et dokument på inntil 2 sider som beskriver hvor dere har forstått oppgaven, og skisserer hvordan dere har tenkt å løse den. 25/3-08 Testbenk for systemet skal være ferdig.

6/5 08 Design og simuleringsarbeidet for hele kretsen skal være ferdig for både skjerna og utlegg, og LYS inkludert. Gruppeliarer skal eventuelt godkjenne at kretsen fungerer tilfredastillende på bakgrunn av demonstrasjel.

#### 3 Krav til prosjektgjennomførin

3. februar 2010

Målsetningen er å lage en digital-til-analog omformer ("DAC") med minimum 6 bit neyaktighet. Gruppens medlemmer må i fellesskap gå gjennom oppgaven og fordele arbeidsoppgaver, men surritige skal krune stå inne for, og redegjær for konstruksjonen. Arbeidsfordelingen mellom deltakere i prosjektet skal

#### rapporteres. Under f 3.1 Praktisk arbeid

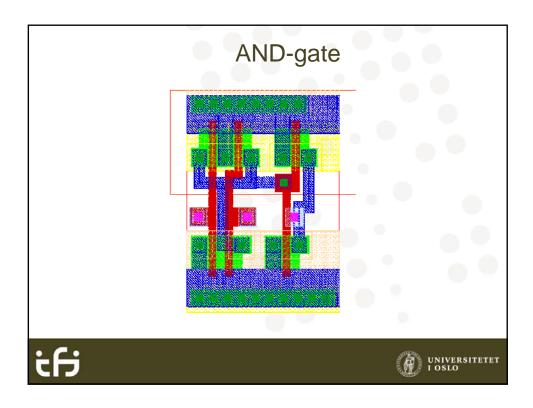

komplette sigema, ned til transistionniva, skall tegnes, luet skall tages symboler for de ulike

byggeblokkene som inngår i det komplette systemet som utgjer detaomformeren.

2. Berytt statistiske ("Monte-Carlo") simuleringer for  $\hat{a}$  verifisere funksjonalitet under prosessvariasjoner.

När simuleringsresutatene er tilfredistbliende skal det tegnes fysisk utlegg (layout") for hver av byggeblokkene, som til slutt settes sammen til den omplette kretsen.

inneholder mixed-signal (analoge og digitale) byggeblokker, identifiser slike utfordringer og foreta tiltak for å løse disse.

Benytt Layout Versus Schematic ("LVS") for delkretser og totalsystem, for å verifisere samsvar mellom kretsskjema og tilsvarende utlegg, og lette konstruksionen. Besultatene fra LVS skal vedlesoes presiektrasporten.

#### . Krav til rapport.

iertralt i bedemmingen av arbeidet veiktleggen rapportens kvallett. Skriv den tallett eller skrivette skal adtet eller tilsverende grogsjam. De ulike fastene av prosjektet skal dokumentenes. Dette inkluderer bla plet av skjemraltik samt simueringsresstatet en demonstrerer brukspenister hos de vilke byggeblökkene. US' rapporter fra som demonstrerer brukspenister hos de vilke bryggeblökkene. US' rapporter fra demonstrerer brukspenister ben de sinde brukspenister ben demonstrerer brukspenister. Begrunn og dokumenter de ulike valgene dere av gott. Dette ruksberre blatt anvet dimensjonering av aktive og passive av gott. Dette ruksberre blatt anvet dimensjonering av aktive og passive

Rapporten skal også inneholde informasjon om hvor Cadence-filer ligge

tilgjengelige for etterkontroll av resultater.

Sensor bedømmer rapporten. Derfor er det viktig at denne er mest muli

#### frister for innlevering.

Prosjektet skal være avsluttet og rapport innlevert senest 9/5-2008 kl. 12:00. Alle gruppene må presentere resultatene av prosjektet etter innlevering. Følg med på fagets hjemmeside for evt andre beskjeder, Vurdering baseres på en bedæmming v arbeidets kvalitet, og rapportens kvalitet, slik dette framgår av sistnevnte. En rosentuell score viktes inn i endelig karakter for faget.

Lykke til!!

12

### INF4420 Project 2009 (1/2)

INF4420 project description

#### Measuring the OTA performance

- If you like, you can also measure

- . Slew rate (how does this compare to the theory?)

- Settling behaviour

Or other relevant parameters

The workings of the calibration loop will be described later.

3. februar 2010

#### 2 Simulating the calibration loop

### INF4420 project 2009 (2/2)

- What is the off-site voltage now?

What is the of of the offset voltage now?

Make a testhetch and measure how the added trimming circuitry affect the formance of the OTA.

- Figure 3 depicts the schematics of a so-called M3M DAC. The mostless are all in trivials region.

- Make a testbench where you compare the transfer function of the ideal DAC with the MIM DAC.

Replace the ideal DAC in your calibration loop test bench with the M3M DAC.

How does this affect the performance of the calibration loop?

Draw layout for the M3M DAC and the current mirror, remember to verify its rectness using DRC and LVS. Finally, do a parasitic extraction of the layout.

· Simulate the calibration loop with the extracted netlists.

#### 4 Project requirements

The transistor sizing given in this document are reasonable guidelines to get you started. You are free to change this if necessary.

Document everything, including but not limited to, all relevant schematics, layout, and simulation results. Discuss the choices you have made in daygning and testing. Everything school be clear just from reading the documentation.

- 1. Do the first part of the project, described in Sect 1. Deadline March 19.

- 2. Do the second part of the project, described in Sect 2. Deadline April 2.

- Finalize the project by completing the third and final part of the project, described in Sect 3, and write your final report. Deadline May 11.

In the first two deliverables, write a short report observing the guidelines in Sect 4. The final report must be comprehensive and document the entire project (i.e. include all deliverables). Only this final report will contribute towards your final grade. Please make all schematics and layout available for inspection.

14

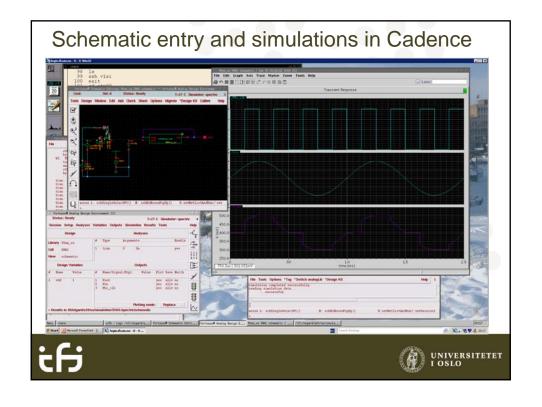

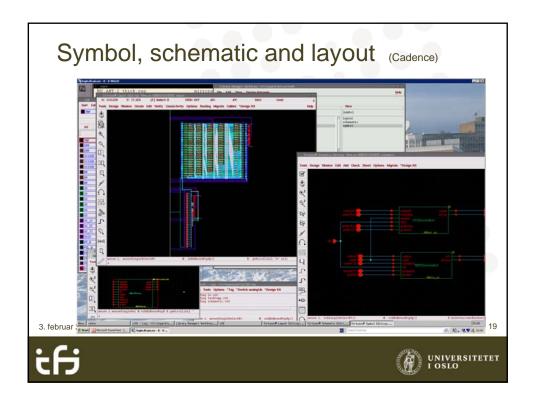

# Cadence (<a href="http://www.cadence.com/">http://www.cadence.com/</a>)

- Widely used IC design tool worldwide, both in companies and academia

- Very large system

- PCB-design

- IC-design

- Synthesis

- Schematic entry

- Simulator (Analog Environment / Spectre)

- Layout (Virtouso)

- DRC and LVS performed by Calibre (Mentor)

C-to-Silicon Named

Hot Product of 2008

### Full-custom ("handmade") design flow

- Design and calculation

- Design equations

- · Dimensioning for matching

- Schematic entry

- Simulations on cells and top level

- Several interactions

- Layout

- Module interface

- Symmetry/hierarchy

- Post Layout Simulations on critical modules

- Next module....

# Cadence forts. • Start-up: Web manual • Standard libraries: • tsmcN90rf • analogLib • Design views: Symbol Schematic Layout ťfi

UNIVERSITETET

#### **Process**

- TSMC 90 nm low power CMOS:

- Minimum gate length: 90nm

- •1 Poly-layer

- 9 Metal-layers

- True triple well

- Three different threshold voltages

- Supply voltage: 1.2 V typ.

- Very advanced process

# Challenges regarding the project

- Project administration

- Theoretical analysis and circuit design

- Design errors

- LVS

- Parasitic components

- Extraction and Post Layout Simulation (PLS)

- Process variations

- Simulations (Corner + Monte-Carlo)

- Noise

- Component and crosstalk

- Good layout practice / Symmetry

#### Practical information

- · Lectures:

- Tuesdays . 9.15 11.00 (should not collide with FYS3240).

- From. 26/2: Tuesday . 9.15 12.00 (Might be 9:15 11:00 in most cases)

- Syllabus:

- Johns and Martin: Analog Integrated Circuit design (Kap. 2, 8-14, 16. Not bipolar)

- Selected additional material and lecture notes

- LTH: Cadence 4.4

- IFI: Lokal guide til Cadence

- Exercises

- 2 hours per week Time will be set next week. Amir Hasanbegovic, amirh@ifi.uio.no

- Projectsupervision/design lab

- 2/4 hours each week Time may be adjusted. Amir H., amirh@ifi.uio.no

- Room 3217 (?)

- Software:

- Cadence 5.00 or 6.00 ((?))

- TSMC 90 nm design kit

- Where to run the software:

- Win PC running X-Win connected to Linux server /remote desktop and Linux

- Linux computer

- Student reference group

- 1-2 students

#### What do we expect from you?

- The course is demanding

- Theoretical background

- INF3410 analog microelectronics, or similar

- FYS3220 linear circuit theory, or similar

- INF3440 signal processing, or similar

- Prepare for the lectures

- Exercises

- Use the reference group and course evaluations to provide feedback

#### Final exam – a few words

- Thursday 3rd of June, starting 14:30 (3 hours)

- Problems usually related to every single of the relevant chapters in the book (2,8,9,...,14,16), and material from the lectures

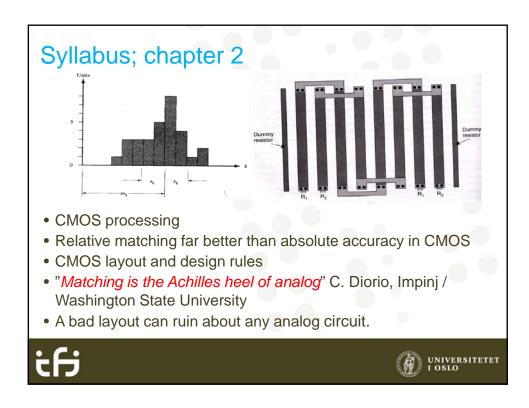

### Syllabus; chapters 2,8,9,10,11,12,13,14,16

- Chapter 2 Processing and layout

- Chapter 8 Sample and Holds, Voltage references, and translinear circuits

- Chapter 9 Discrete-Time Signals

- Chapter 10 Switched-capacitor circuits

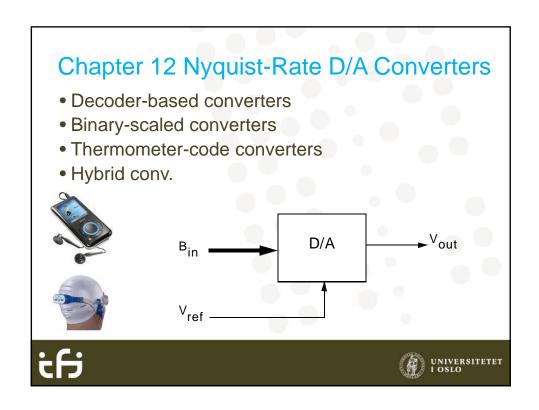

- Chapter 11 Data converter fundamentals

- Chapter 12 Nyquist-rate D/A converters

- Chapter 13 Nyquist-rate A/D converters

- Chapter 14 Oversampling converters

- Chapter 16 Phase-locked loops

# Chapter 8 Sample and Holds, Voltage References

- Performance of S/H

- S/H basics

- Bandgap voltage reference basics

- Circuits for bandgap references

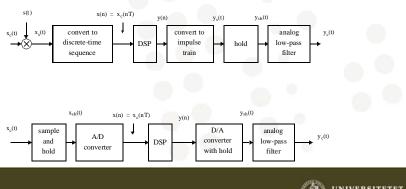

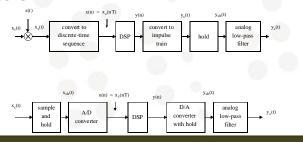

# Chapter 9 Discrete-Time Signals

- Signal spectra

- Laplace transform of discrete-time signals

- Z-transform

- Downsampling and upsampling

- Discrete-time filters

- S/H response

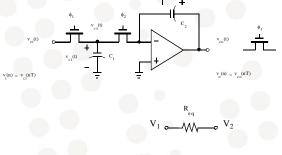

# **Chapter 10 Switched-Capacitor Circuits**

- Building blocks

- Operation and analysis

- First-order filters

- Biquad filters

# Chapter 13 Nyquist-Rate A/D Converters Integrating converters Successive approx. converters Algorithmic converters Flash (parallell) conv. Two-step, interpolating, Folding, pipelined conv.

## Two consequences of the Nyquisttheorem and anti-aliasing filters (Wikipedia):

- If the highest frequency *B* in the original signal is known, the theorem gives the lower bound on the sampling frequency for which perfect reconstruction can be assured. This lower bound to the sampling frequency, 2*B*, is called the Nyquist rate.

- If instead the sampling frequency is known, the theorem gives us an upper bound for frequency components, B<fs/2, of the signal to allow for perfect reconstruction. This upper bound is the Nyquist frequency, denoted fN.

- An anti-aliasing filter is a filter used before a signal sampler, to restrict the

bandwidth of a signal to approximately satisfy the <u>sampling theorem</u>. Since

the theorem states that unambiguous interpretation of the signal from its

samples is possible only when the power of frequencies outside the Nyquist

bandwidth is zero, the anti-aliasing filter would have to have perfect stopband rejection to completely satisfy the theorem. Every realizable antialiasing filter will permit some <u>aliasing</u> to occur; the amount of aliasing that

does occur depends on how good the filter is.

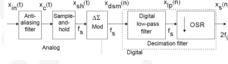

## **Chapter 14 Oversampling Converters**

- Oversampling (>> 2 Nyquist bandwidth) relaxes requirements for matching

- High resolution, low to medium speed

- Noise shaping & oversampling

- N+1 order modulator gives a certain SNR for lower OSR

than N-order mod.

24 bit Audio conv.

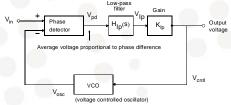

# Chapter 16 Phase-locked loops

- Application examples:

- clock multiplication,

- Freq. generation: The PLL output is a signal with frequency N times the input frequency where N may be a fractional number

- FM demodulation (The input is a FM signal (IF) The output is the demodulated baseband signal

- Products: TV and wireless