### Last time – and today, Tuesday 23rd of February:

- 9.2 Laplace Transform of Discrete Time Signals

- 9.3 z-transform

- 9.4 downsampling and Upsampling

- 9.5 Discrete Time Filters

- 9.6 Sample-and-Hold Response

- 10.1 Switched Capacitor Circuits

- 10.2 Basic Operation and Analysis

### Today:

- 10.3 First-order filters

- 10.4 Biquad filters (high-Q)

- 10.5 Charge injection

- 10.7 Correlated double sampling techn

- 11.1 Ideal D/A converter

- 11.2 Ideal A/D converter

- 11.3 quantization noise

- 11.4 signed codes

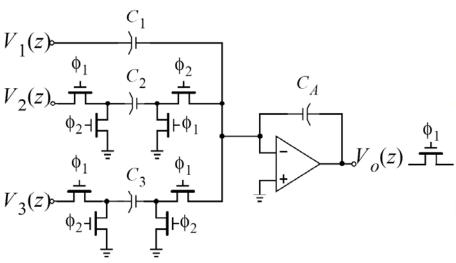

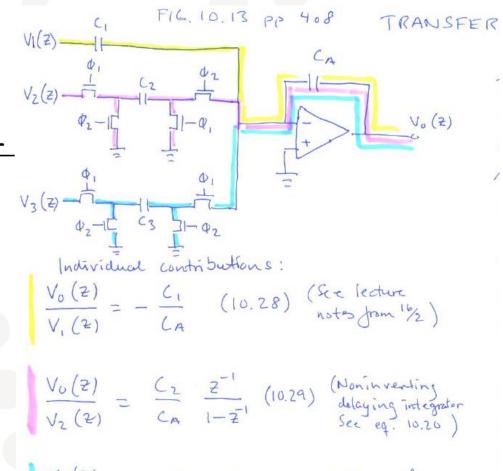

### Signal-flow-graph analysis (p. 407)

- Applying charge equations is tedious for larger circuits. Using some rules and signal-flow-graph analysis simplifies analysis and design of SC-circuits.

- Superposition (Wikipedia)In a linear system, the net response at a given place and time caused by two or more independent stimuli is the sum of the responses which would have been caused by each stimulus individually.

$$\frac{V_0(2)}{V_3(2)} = -\frac{C_3}{C_A} \frac{1}{1-2^{-1}} (10.30) (delay - free int., see eq. 10.25)$$

### Getting the transfer function...

Multiplying each of the equations (10.28), (10.28) (10.30) by their respective input voltages, on each side:

$$V_{o}(2) = -\frac{C_{1}}{C_{A}} \cdot V_{1}(2)$$

$$V_0(2) = \frac{C_2}{C_A} \frac{2^{-1}}{1-2^{-1}} \cdot V_2(2)$$

$$V_{0}(2) = -\frac{C_{3}}{C_{A}} \frac{1}{(1-2^{-1})} \cdot V_{3}(2)$$

Adding the contributions:

$$V_{\text{out}}(z) = -\frac{C_1}{C_A} \cdot V_1(z) + \frac{C_2}{C_A} \frac{z^{-1}}{1-z^{-1}} V_2(z) + -\frac{C_3}{C_A} \frac{1}{(1-z^{-1})} \cdot V_3(z)$$

Ve bonnere of 5;

$$V_{out}(2) = -\frac{C_1}{C_A} \cdot V_1(2) + \frac{C_2}{C_A} \frac{1}{z-1} V_2(2) - \frac{C_3}{C_A} \frac{Z}{Z-1} V_3(2)$$

(10.31)

TET

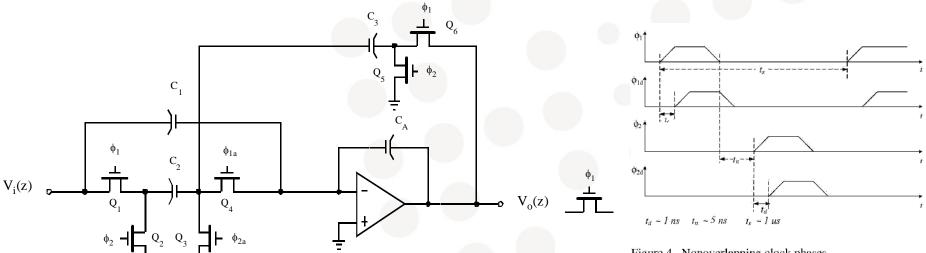

### Signal Flow Graph (Fig. 10.13 in "J & M")

SIGNAL FLOW GRAPH IN FIG 10, 13

$$V_{\text{out}}(2) = -\frac{C_1}{C_A} \cdot V_1(2) + \frac{C_2}{C_A} \frac{z^{-1}}{1-z^{-1}} V_2(2) - \frac{C_3}{C_A} \frac{1}{1-z^{-1}} V_3(2)$$

$$= -\frac{C_1}{C_A} \frac{(1-z^{-1})}{(1-z^{-1})} \cdot V_1(2) + \frac{C_2}{C_A} \frac{z^{-1}}{1-z^{-1}} V_2(2) - \frac{C_3}{C_A} \frac{1}{1-z^{-1}} V_3(2)$$

See that  $\frac{1}{C_A} \frac{1}{(1-z^{-1})}$  is a common factor

$$V_{1}(2) \xrightarrow{-C_{1}(1-2^{-1})} V_{2}(2)$$

$$V_{2}(2) \xrightarrow{-C_{3}} \xrightarrow{-C_{3}} V_{3}(2)$$

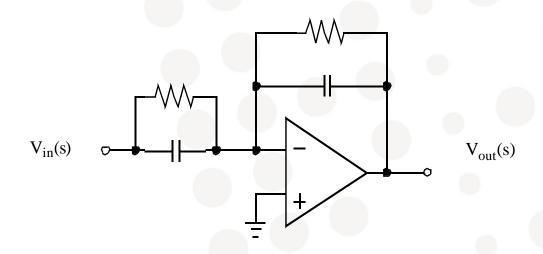

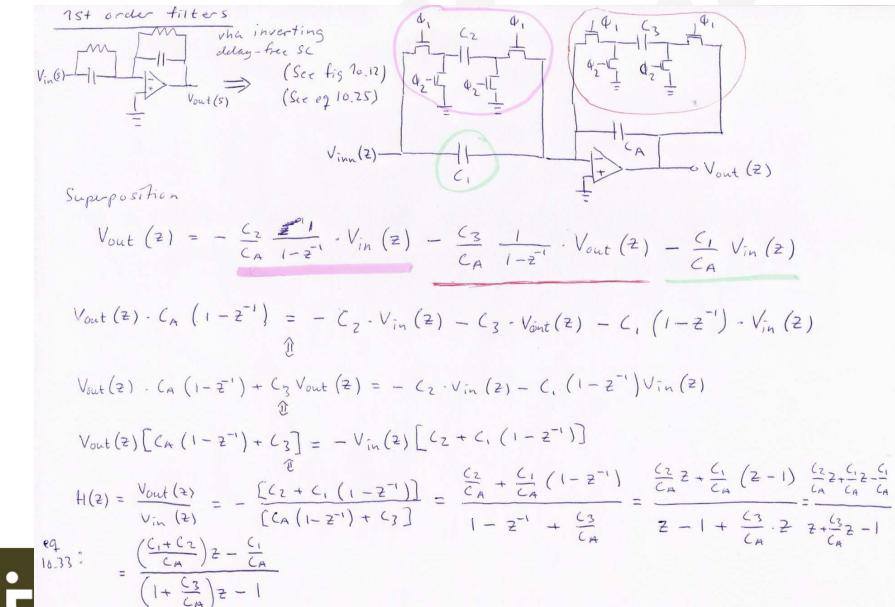

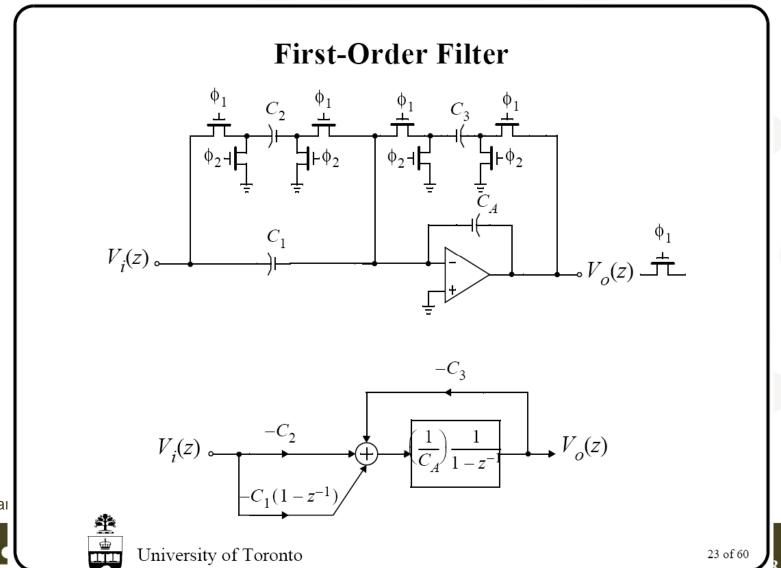

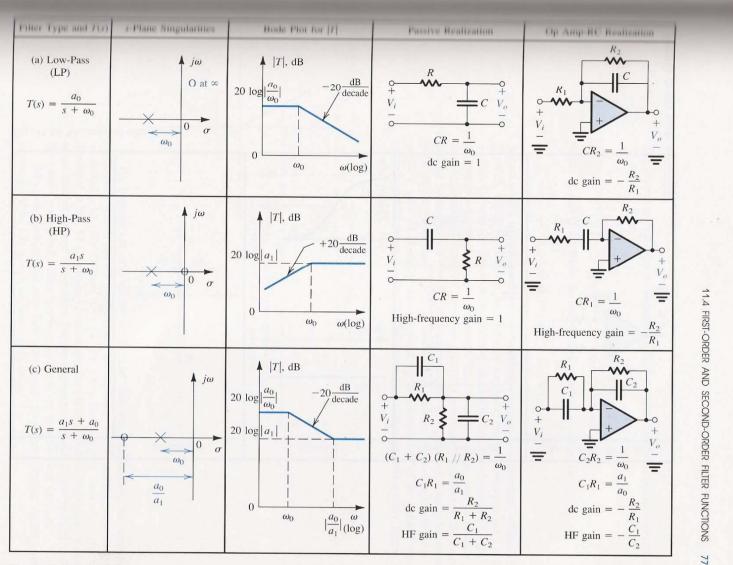

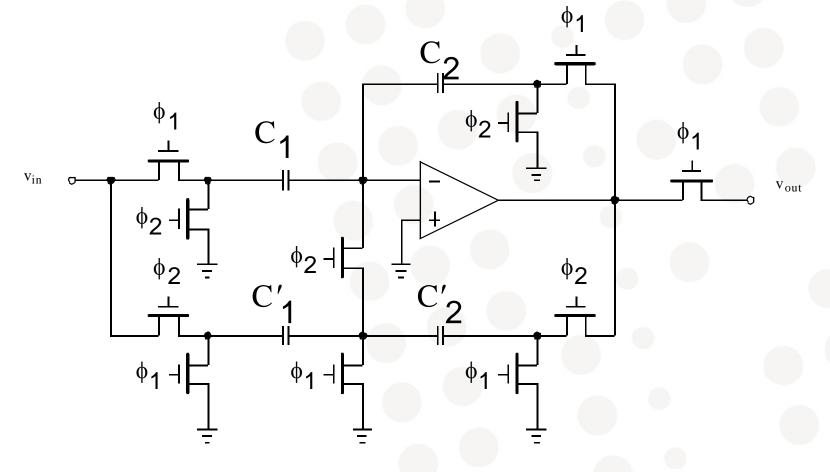

### First-Order Filters

- Select a known Active-RC circuit

- Replace resistors by SC-equivalents

- Analyze using discrete-time methods

### Making 1st order SC-filter from active RC equivalent

### SFG based on superposition, similar as in fig 10.13.

25. februai

th

RSITETET

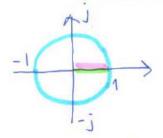

#### POLES ?

Equating the denominator to zero, in H(2):

$$\left(1 + \frac{C_3}{C_A}\right)^2 - 1 = 0$$

$$\frac{C_A}{C_A + C_3}$$

For positive capacitance values this pole is retricted to the real axis between zero and one

Z-plane

In this case the circuit is always stable.

The case of Cz = 0:

$$Z_p = \frac{C_A}{C_A + C_3} = \frac{C_A}{C_A} = 1$$

### ZERUS?

Numerator in H(2) = 0

$$\left(\frac{C_1 + C_2}{C_A}\right)^2 - \frac{C_1}{C_A} = 0$$

$$\left(\frac{C_1 + C_2}{C_A}\right)^2 = \frac{C_1}{C_A} = 0$$

For positive capacitances the Zero is located to the real axis between 0 and 1.

$$DC - gain (Z = 1):$$

$$H(1) = -\frac{\binom{C_1 + C_2}{C_A} Z - \frac{C_1}{C_2}}{\binom{1 + \frac{C_3}{C_A} Z - 1}{C_A}} = -\frac{\binom{C_1}{C_A} + \frac{C_2}{C_A} - \frac{C_1}{C_A}}{\binom{C_1}{C_A} - 1}$$

$$= -\frac{\binom{C_2}{C_A}}{\binom{C_3}{C_A}} = -\frac{\binom{C_2}{C_3}}{\binom{C_3}{C_A}}.$$

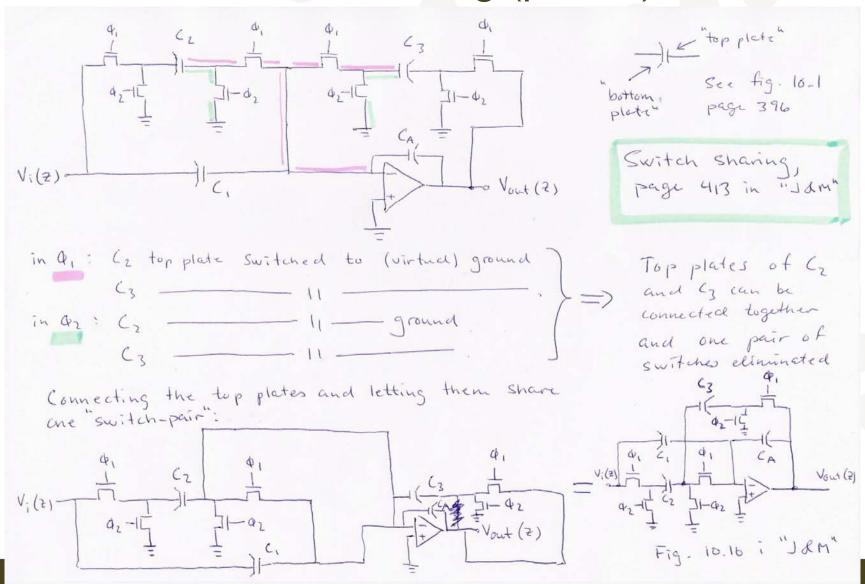

### Switch sharing (p. 413)

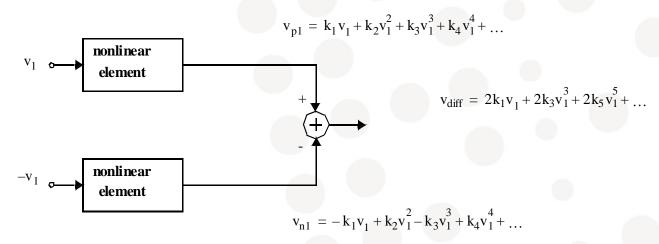

### Fully Differential Filters (p. 414 (1/3))

- The signal is represented by the difference of two voltages

- Most SC-designs are fully differential, typically operating around a dc common-mode voltage halfway between the supply voltages

- Reduced common-mode noise

- Cancellation of even-order harmonic distortion, if the nonlinearity is memoryless

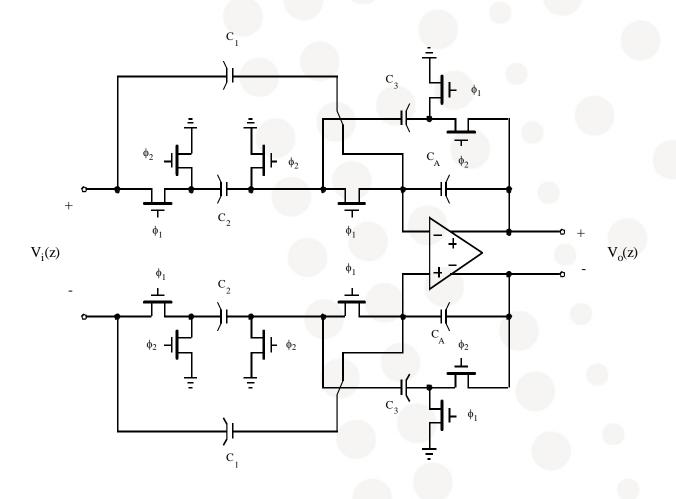

### Differential implementation (fig. 10.18 p. 415)

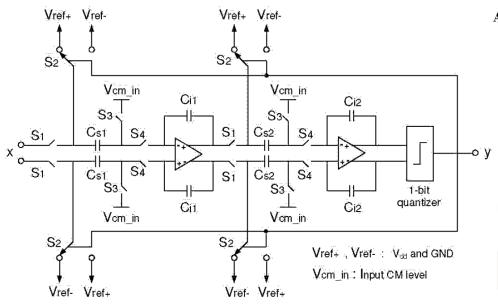

#### Example: Fully differential SC-sigma-delta ADC published May 2007

S1,S2,S3,S4; controlled by nonoverlapping clock phases

### A MICRO POWER SIGMA-DELTA A/D CONVERTER IN 0.35-μM CMOS FOR LOW FREQUENCY APPLICATIONS

Adnan Gundel<sup>1,2</sup>, William N. Carr<sup>1</sup>

<sup>(1)</sup>New Jersey Institute of Technology, Newark, NJ 07102 <sup>(2)</sup>Telephonics Corporation, 815 Broad Hollow Road, Farmingdale, NY 11735

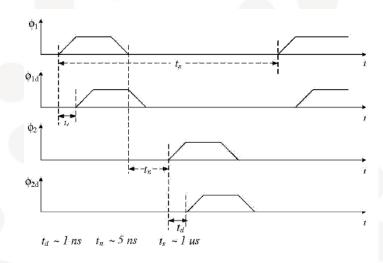

Figure 4. Nonoverlapping clock phases.

## Properties of Fully Differential Filters, compared to single-ended solutions

- Requires two copies of a single-ended filter except from the Opamp which is shared

- Common-mode feedback circuitry is required

- The input- and output signal amplitude are doubled. The same dynamic range can be achieved with half-sized capacitors:

- Area reduction and less power consumption

- Reduced size of switches (less charge)

- More wires are required

- Improved performance with respect to noise and distortion

### Some Active RC 1st order filters (Sedra & Smith p. 779). Filter in fig 10.14 in "Johns & Martin" lowermost.

Fig. 11.13 First-order filters.

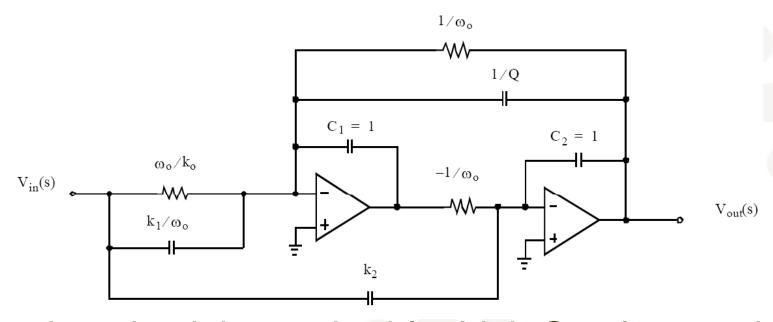

### High-Q Biquad active RC-filter

- Another circuit is required for high Q-values and small capacitor spread

- Q-damping is obtained by adding a capacitor around both integrators instead of a resistive feedback around the last integrator

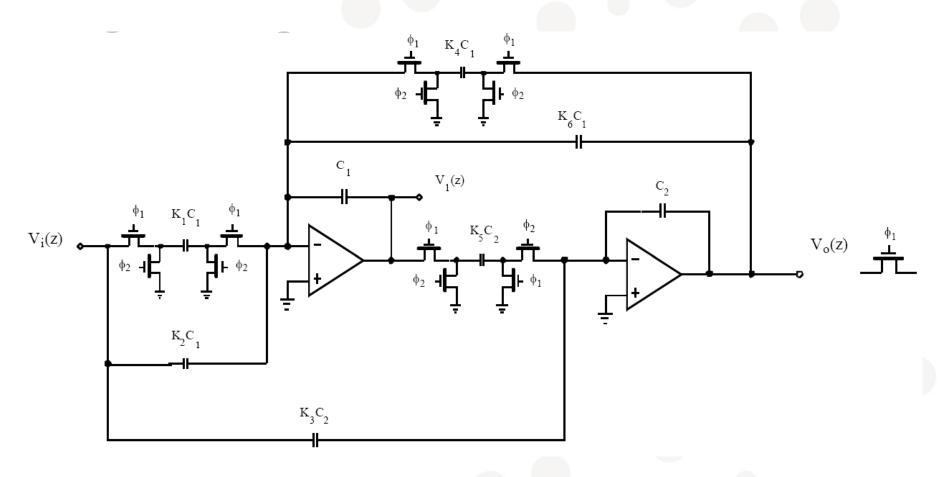

### High-Q Switched-capacitor biquad filter (Fig. 10.25, p. 421) by changing the resistors with SC-equivalents

### High-Q Biquad Filter

General transfer function:

$$H(z) = \frac{V_o(z)}{V_i(z)} = -\frac{K_3 z^2 + (K_1 K_5 + K_2 K_5 - 2K_3)z + (K_3 - K_2 K_5)}{z^2 + (K_4 K_5 + K_5 K_6 - 2)z + (1 - K_5 K_6)}$$

The function can be rewritten as:

$$H(z) = -\frac{a_2z^2 + a_1z + a_0}{z^2 + b_1z + b_0}$$

The coefficients are then:

$$K_1K_5 = a_0 + a_1 + a_2$$

$K_2K_5 = a_2 - a_0$

$K_3 = a_2$

$K_4K_5 = 1 + b_0 + b_1$

$K_5K_6 = 1 - b_0$

• A signal-flow-graph approach is used to find the transfer function. There is some freedom in chossing the coefficients as there is one less equation than the number of coefficients. K4 = K5 = SQR (1+b0 + b1) defines the other ratios.

### Ex 10.5 1) BP-filter, peak gain 5 near fs/10 amd Q of about 10

$$H(z) = -\frac{0.28f(z-1)}{z^2 - 1.572z + 0.7427}$$

Find the largest to smellest expectation ratio if this transfer function is realized using the higher Q signed circuit. Let  $C_1 = C_2$ .

$$(19.34): K_4 = K_5 = 1 + b_0 + b_1 = 1 + 0.9429_{+1.572}^{+1.572}$$

$$= \sqrt{0.3709} = 0.6090$$

$$K_5 \cdot K_6 = 1 - b_0 \Leftrightarrow K_6 = \frac{(1 - b_0)}{0.6090}$$

$$K_3 = a_2 = 0 \quad (Sec 10.8)$$

$$= \frac{1 - 0.4429}{0.6930} = \frac{0.6551}{0.6090} = \frac{0.6938}{0.6930}$$

$$K_1 \cdot C_1 = 0.6090 \cdot C_1$$

$$K_1 \cdot C_2 = 0.6090 \cdot C_1$$

$$K_2 \cdot C_3 = 0.6090 \cdot C_4$$

$$K_4 \cdot C_4 = 0.6090 \cdot C_1$$

$$K_5 \cdot C_5 = 0.6090 \cdot C_1$$

$$K_6 \cdot C_1 = 0.6090 \cdot C_1$$

$$K_7 \cdot C_1 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_2 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_3 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_4 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_5 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_1 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_2 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_3 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_4 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_4 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_4 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_5 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_6 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_7 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_8 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_8 = 0.6090 \cdot C_1$$

$$K_8 \cdot C_9 = 0.6090 \cdot C_1$$

$$K_9 \cdot C_9 = 0.6090 \cdot C_1$$

$$K_$$

Max. capa citana spread To 10,66

19

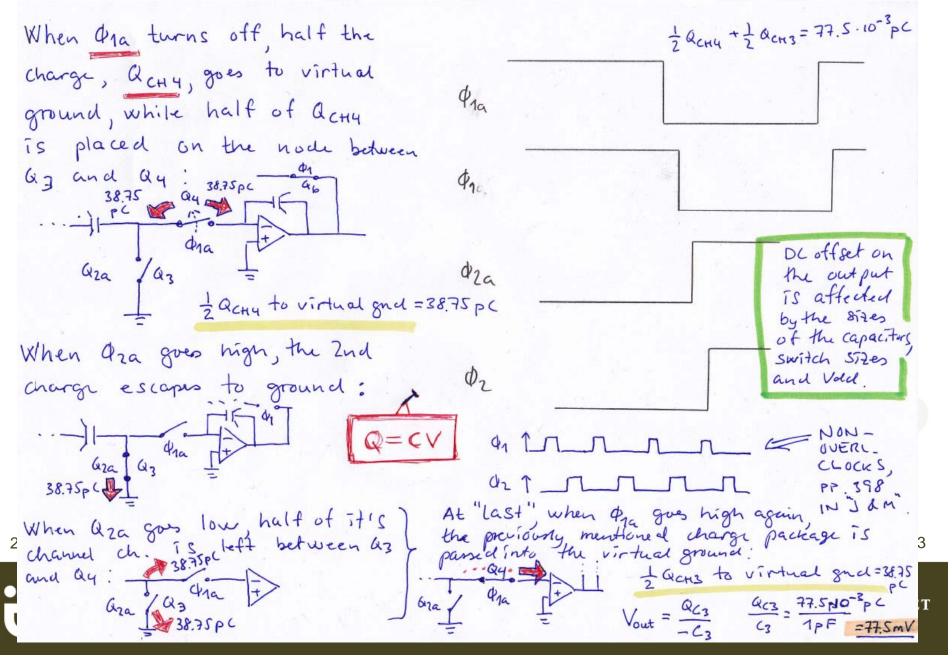

### Charge Injection (chapter 10.5)

Figure 4. Nonoverlapping clock phases.

- To reduce the effects of charge injection in SC circuits, realize all switches connected to ground or virtual ground as nchannel switches only, and turn off the switches connected to ground or virtual ground first. Such an approach will minimize distortion and gain error as well as keeping DC offset low.

- In this case  $\theta_{1a}$  and  $\theta_{2a}$  are turned off first to prevent other switches affecting the output voltage of the circuit.

\ Q3, Q4

as and ay connect to ground az, as or virtual ground, respectively, — meaning that when they are turned on (dza = Vad or ana = Vad) they need only pass a signal near the ground node (vss = ov).

VIRTUAL GROUND

These two switches can be realized using single n-channel transistors. A 2nd important reason for this is that the charge injections due to az and ay one not signal dependent (as will be seen)

Channel charge of an NMOS intriode, (chapter 7): QCH = -WL Cox Veff

When as and ay are on, Vos = VDIS, and since their Source remain at a volts, their Vt's remain constant (inequal)

2: THE CHARGE INJECTED BY UB, Q4 IS THE SAME FROM ONE CLOCK CYCLE TO THE NEXT AND CAN BE CONSIDERED AS A DC OFFSET.

Unfortunally this is not the case for Q1 and Q6. Ex Q1: Qcts = -W.L. (ox (VD-VI-V+))

In this can one portion of the channel charge is linearly related to Vi. The Vtn changes in a nonlinear relation-ship (bulk effect). Ochy has a line and ninin. relation ship to Vi and would cause a gain error and distortion if an were turned off early.

TO MINIMIZE DISTORTION, GAIN ERR. AND DE OFFS :

TO REDUCE THE EFFECTS OF CHARGEINJECTION IN SC-CIRCUITS REALIZE

ALL SWITCHES CONNECTED TO GROUND

OR VIRTUAL GROUND AS N-CHANNEL

SWITCHES, AND TURN OFF THE SWITCHES

NEAR THE VIRTUAL GROUND OF THE CPAMPS FIRST.

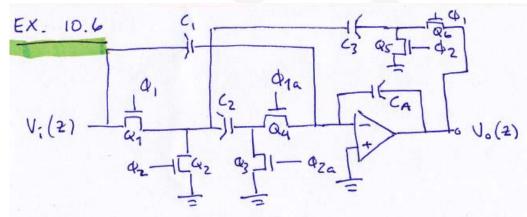

### Ex. 10.6 (1/2)

Assume an ideal opamp. Estimate the amount of de offset at the output due to channel-charge injection when  $C_1 = 0$  and  $C_2 = C_A$   $= 10 C_3 = 10 pF. V_{tn} = 0.8V, W = 30 pm, L = 0.8 pm. Vdu = ±2,5V$   $Cox = 39 \cdot 10^{3} pF. (pm)^{2}$   $R_{3} \text{ and } R_{4} \text{ are advanced, and contribute with channel charge.}$   $Q_{CH_{3}} = Q_{CH_{4}} = (-30 \cdot 10^{-6}) (0.8 \cdot 10^{-6}) 1.9 \cdot 10^{-3} \cdot \frac{10^{-12}}{(10^{-6})^{2}} (2.5 - 0.8) C$   $= -30 \cdot 0.8 \cdot 0.0019 \cdot 1.7 pC = 0.07752 pC$

25. februar 2

The dc freedback will keep the virtual input of the opamp at O volts. All freedback current is charge transferred through C3.

### Ex. 10.6 (2/2)

# Ron I

V = @

### CHARGE INJECTION AND HIGHER FREQUENCIES

The smaller the Ron and smaller the C, the higher the frequency of switching (possible)

$H(s) = \frac{1}{1+\tau s} \wedge \tau = RC$

To decream Ron the Size of the switch increases, and thus the charge injection.

Will derive a simple formula that gives the upper bound on the frequency of operation of an SC circ for a max. voltage change due to charge inj.:

(ignore overlap capacitance)

MOST SC CIRC. HAVE 2 SERIES SWITCHES PER CAPACITOR. AS A RULE OF THUMB, FOR 6000 SETTLING, THE SAMPLING CLOCK HALF PERIOD MUST BE GREATER THAN S TIME CONST.

$\frac{T}{2} > 5 \text{ Ron} \cdot C \iff f_{Clk} < \frac{1}{10 \text{ Ron} C} (10.69)$

folk = + PhCox . W. Veff Using (10.83) the charge change due to the channel charge cound by turning an n-channel switch off Ts approximated by IDV 1 = 1 QCH . 1 = WLCox Veff For a specified DV/max C = WL Cox Veff 2/AV/max Substituting in (10.89): folk < 10. I PALOR L Vett 2/AV/max folk < Pn / DV/max

D: UPPER FREQ. LIMIT

INVERSELY PROPORTIONAL

TO L2, IT IGNORES OVERLAP

CAP. AND IS SOMEWHAT OPTIMISTIC

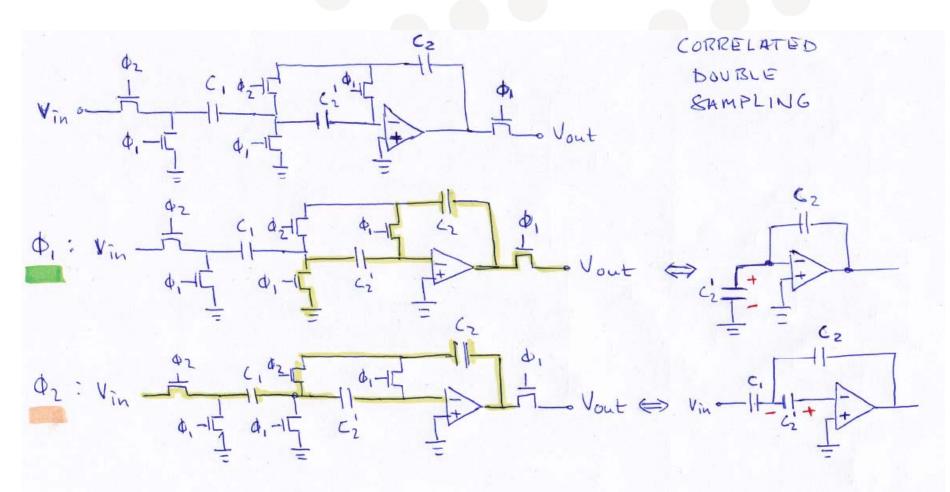

### Correlated Double Sampling ("CDS")

- Used to realize highly accurate gain amplifiers, sample-and-hold circuits and integrators to reduce errors due to offset voltages, 1/f noise and finite opamp gain.

- Method: During a calibration phase the input voltage of an opamp is sampled and stored (accross a C) and later subtracted from the signal in the operational phase (when the output is being sampled), by appropriate switching of the capacitors.

- A detailed description is beyond the scope of the text in "J & M". The interested reader may check: C. G. Themes, C. Enz: "Circuit techniques for reducing the effects of opamp imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization", Proceedings of the IEEE, Nov. 1996.

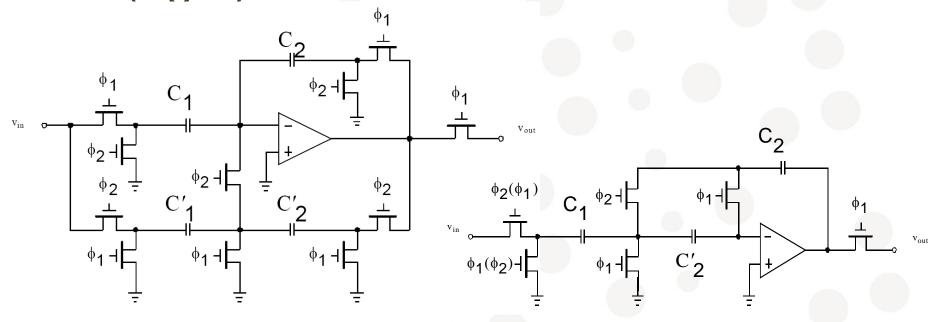

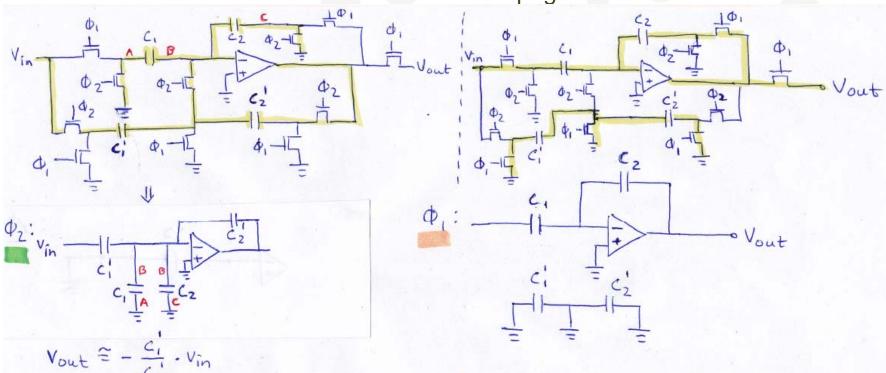

# SC amplifier (left) and SC integrator with CDS (right)

- For the amplifier: During  $\theta 2$  the error is sampled and stored across C1 and C2

- The stored error is then subtracted during  $\theta$ 1

- For the integrator: During  $\theta$ 1 the error is sampled and stored across C'2

- The stored error is then subtracted during  $\theta 2$

The opamp input error voltage is sampled during of.

Next, during d', ('z is connected in series with the opamp's inverting input and greatly minimizes the effects of these errors (by a factor of the inverse of the opamp's gain over what would otherwise occur at frequencies substantially less than the sampling frequency).

Integrator fig. 10.35

An additional capacitor, Li samples

the opamp input error voltage during

4.

During dz, Cz is connected in series with the opamp's inverting input and greatly minimizes the effects of these errors

- Reducing errors by a factor of the inverse of the opamp's gain over what would other-wise occur at frequencies substantially less than the sampling frequency

- opemps should be designed to minimize thermal noise rather than 1/4 noise.

- only a couple among the stages typically need CDS

- · Very unful in oversampling A/D converters.

25. februar ∠∪ r∪

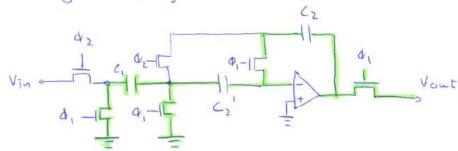

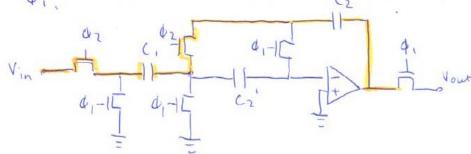

### SC-integrator with CDS ("J & M" page 434)

During Phi2 the error is sampled and stored accross C2

Errors due to finite-offset voltage, I noise and gain are included. At the same time the finite opamp input voltage caused by these errors is sampled and stored accross (, and (z.

Next, during a, this input error voltage is subtracted from the signal (applied to the opamp input) at that time.

Assuming that the input voltage

Assuming that the input voltage and the opamp input error voltages did not change appreciably from d, to \$2 errors due to them will be significantly reduced.

30

TET

25. februar 2010 31

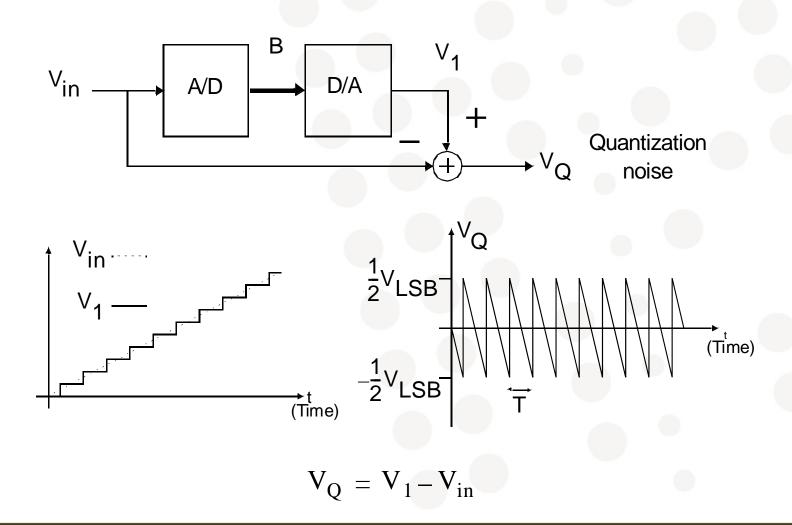

### Data Converter Fundamentals (chapter 11)

### Main data converter types:

- Nyquist-rate converters:

- Each value has a one-to-one correspondence with a single input

- The sample-rate must be at least equal to twice the signal frequency (Typically somewhat higher)

- Oversampled converters:

- The sample-rate is much higher than the signal frequency, typically 20 – 512 times.

- The extra samples are used to increase the SNR

- Often combined with noise shaping

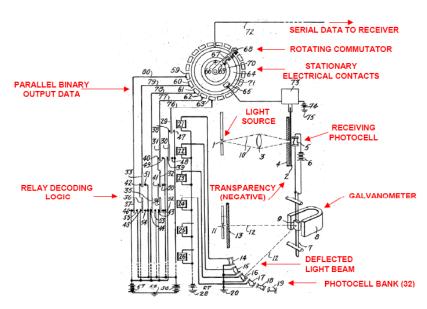

# Flash ADC from 1926 (Analog Digital Conversion handbook, Analog Devices)

The first documented flash converter was part of Paul M. Rainey's electro-mechanical PCM facsimile system described in a relatively ignored patent filed in 1921 (Reference 5—see further discussions in Chapter 1 of this book). In the ADC, a current proportional to the intensity of light drives a galvanometer which in turn moves another beam of light which activates one of 32 individual photocells, depending upon the amount of galvanometer deflection (see Figure 3.49). Each individual photocell output activates part of a relay network which generates the 5-bit binary code.

Figure 3.49: A 5-Bit Flash ADC Proposed by Paul Rainey

Adapted from Paul M. Rainey, "Facsimile Telegraph System," U.S. Patent

1,608,527, Filed July 20, 1921, Issued November 30, 1926

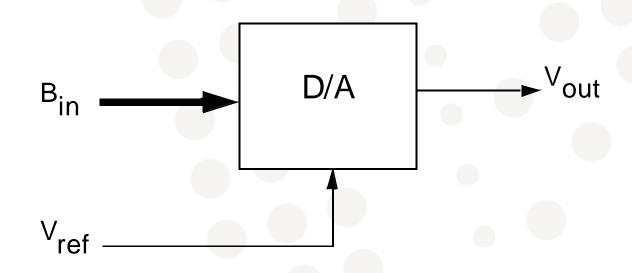

### 11.1 Ideal D/A converter

$$B_{in} = b_1 2^{-1} + b_2 2^{-2} + \dots + b_N 2^{-N}$$

$$V_{out} = V_{ref}(b_1 2^{-1} + b_2 2^{-2} + ... + b_N 2^{-N})$$

### Example 11.1: 8-bit D/A converter

An ideal D/A converter has

$$V_{ref} = 5 V$$

Find Vout when

$$B_{in} = 10110100$$

$$B_{in} = 2^{-1} + 2^{-3} + 2^{-4} + 2^{-6} = 0,703125$$

$$V_{out} = V_{ref}B_{in} = 3,516 V$$

Find

$$V_{\mathsf{LSB}}$$

$$V_{LSB} = 5/256 = 19,5 \text{ mV}$$

$$V_{LSB} \equiv \frac{V_{ref}}{2^N}$$

$$1 LSB = \frac{1}{2^{N}}$$

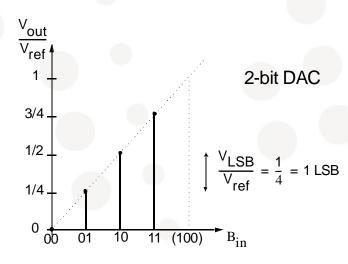

## 11.2 Ideal A/D converter (Fig. 11.3)

$$V_{ref}(b_1 2^{-1} + b_2 2^{-2} + \dots + b_N 2^{-N}) = V_{in} \pm V_x$$

where

$$-\frac{1}{2}V_{LSB} \leq V_x \ < \frac{1}{2}V_{LSB}$$

#### Ideal transfer curve for a 2-bit A/D converter (Fig. 11.4)

$$B_{out}$$

$V_{ref}$  = 1/4 = 1 LSB  $V_{ref}$   $V_{ref}$

- •A range of input values produce the same output value (QA range of input values produce the same output value (Quantization error)

- •Different from the D/A case

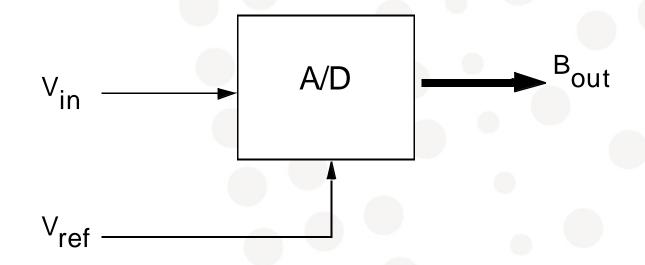

## 11.3 Quantization noise

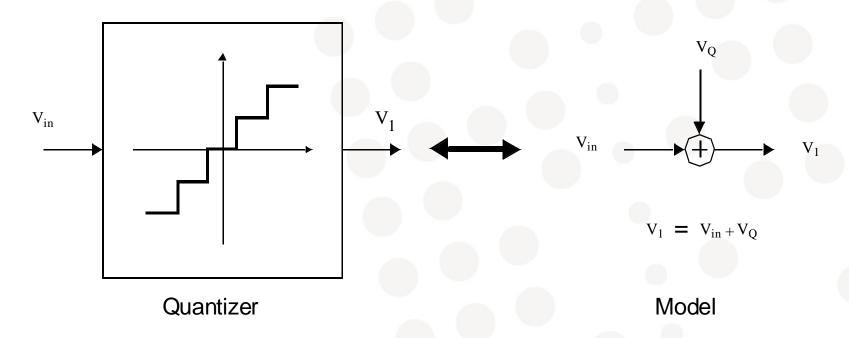

## Quantization noise model

- $\bullet The \ model \ is \ exact \ as \ long \ as \ V_Q$  is properly defined

- •V<sub>Q</sub> is most often assumed to be white and uniformely distributed between +/- V<sub>Isb</sub>/2

## Quantization noise

•The rms-value of the quantization noise can be shown to be:

$$V_{Q(rms)} = \frac{V_{LSB}}{\sqrt{12}}$$

- Total noise power is independent of sampling frequency

- •In the case of a sinusoidal input signal with p-p amplitude of  $V_{\rm ref}/2$

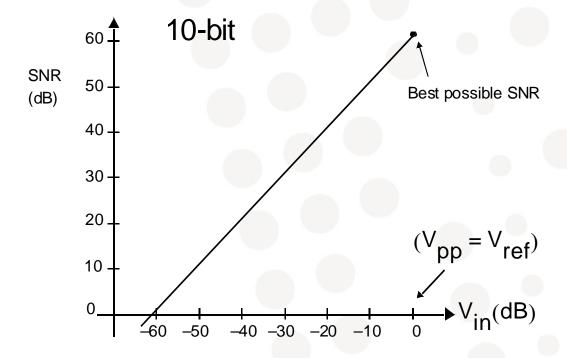

$$\begin{split} \text{SNR} &= 20 \log \left( \frac{V_{in\text{(rms)}}}{V_{Q\text{(rms)}}} \right) = 20 \log \left( \frac{V_{ref}/(2\sqrt{2})}{V_{LSB}/(\sqrt{12})} \right) \\ \text{SNR} &= 6{,}02N + 1{,}76 \text{ dB} \end{split}$$

#### Quantization noise (SNR as a function of Vin)

•Signal-to Noise ratio is highest for maximum input signal amplitude

## 11.4 Signed codes

| Number            | Normalized number | Sign<br>magnitude | 1's complement | Offset<br>binary | 2's<br>complement |

|-------------------|-------------------|-------------------|----------------|------------------|-------------------|

| +7                | +7/8              | 0111              | 0111           | 1111             | 0111              |

| +6                | +6/8              | 0110              | 0110           | 1110             | 0110              |

| +5                | +5/8              | 0101              | 0101           | 1101             | 0101              |

| +4                | +4/8              | 0100              | 0100           | 1100             | 0100              |

| +3                | +3/8              | 0011              | 0011           | 1011             | 0011              |

| +2                | +2/8              | 0010              | 0010           | 1010             | 0010              |

| +1                | +1/8              | 0001              | 0001           | 1001             | 0001              |

| +0                | +0                | 0000              | 0000           | 1000             | 0000              |

| (-0)              | (-0)              | (1000)            | (1111)         |                  |                   |

| ( <del>-0</del> ) | -1/8              | 1001              | 1110           | 0111             | 1111              |

| -1<br>-2          | -2/8              | 1010              | 1101           | 0110             | 1110              |

| -3                | -3/8              | 1011              | 1100           | 0101             | 1101              |

| -4                | -4/8              | 1100              | 1011           | 0100             | 1100              |

| -5                | -5/8              | 1101              | 1010           | 0011             | 1011              |

| -6                | -6/8              | 1110              | 1001           | 0010             | 1010              |

| _0<br>_7          | -7/8              | 1111              | 1000           | 0001             | 1001              |

| -7<br>-8          | -8/8              |                   |                | 0000             | 1000              |

- Unipolar / bipolar

- Common signed digital repr.: sign magnitude, 1's

complement, 2's compl.

- Sign. M.: 5:0101, -5:1101, two repr. Of 0, 2<sup>N</sup>-1 numb.

- 1's compl.: Neg. Numbers are complement of all bits for equiv. Pos. Number: 5:0101, -5:1010

- Offset bin: 0000 to the most neg., and then counting up..

- +: closely related to unipolar through simple offset

## 2's complement

| A3a2a1a0 | Sign<br>magnitude | 2s complement |

|----------|-------------------|---------------|

| 0111     | +7                | +7            |

| 0110     | +6                | +6            |

| 0101     | +5                | +5            |

| 0100     | +4                | +4            |

| 0011     | +3                | +3            |

| 0010     | +2                | +2            |

| 0001     | +1                | +1            |

| 0000     | +0                | +0            |

| 1000     | -0                | -8            |

| 1001     | -1                | -7            |

| 1010     | -2                | -6            |

| 1011     | -3                | -5            |

| 1100     | -4                | -4            |

| 1101     | -5                | -3            |

| 1110     | -6                | -2            |

| 1111     | -7<br>2007,ea     | -1            |

•

$$5_{10}$$

:  $0101 = 2^2 + 2^0$

• -

$$5_{10}$$

: (0101)' +1 = 1010 + 1 = 1011

- Addition of positive and negative numbers is straightforward, using addition, and requires little hardware

- 2's complement is most popular representation for signed numbers when arithmetic operations have to be performed

7<sub>10</sub>-6<sub>10</sub> via addition using two's complement of -6

- Subtraction uses addition: The appropriate operand is negated before being added

- Negating a two's complement number: Simply invert every 0 and 1 and add one to the result. Example:

- 0000 0000 0000 0000 0000 0000 0000 0110<sub>2</sub> becomes

- 1111 1111 1111 1111 1111 1111 1111 1001<sub>2</sub>

+ 1;

\_\_\_\_\_

## 11.5 performance limitations

- Resolution

- Offset and gain error

- Accuracy

- Integral nonlinearity (INL) error

- Differential nonlinearity (DNL) error

- Monotonicity

- Missing codes

- A/D conversion time and sampling rate

- D/A settling time and sampling rate

- Sampling time uncertainty

- Dynamic range

- NB!! Different meanings and definitions of performance parameters sometimes exist. → Be sure what's meant in a particular specification or scientific paper.. There are also more than those mentioned here.

#### Resolution

- Resolution usually refers to the number of bits in the input (D/A) or output (ADC) word, and is often different from the accuracy.

- Analog-Digital Conversion Handbook, Analog Devices, 3rd Edition, 1986: An n-bit binary converter should be able to provide 2n distinct and different analog output values corresponding to the set of n binary words. A converter that satisfies this criterion is said to have a resolution of n bits.

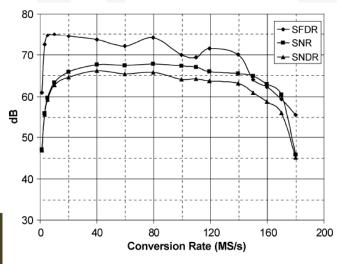

#### A Cost-Efficient High-Speed 12-bit Pipeline ADC in 0.18- $\mu$ m Digital CMOS

Terje Nortvedt Andersen, Bjørnar Hernes, Member, IEEE, Atle Briskemyr, Frode Telstø, Johnny Bjørnsen, Member, IEEE, Thomas E. Bonnerud, and Øystein Moldsvor

TABLE I KEY DATA FOR THE ADC

| Nominal sampling rate         | 110MS/s             |

|-------------------------------|---------------------|

| Technology                    | 0.18µm digital CMOS |

| Nominal supply voltage        | 1.8V                |

| Resolution                    | 12bit               |

| Full scale analog input       | $2V_{P-P}$          |

| Area                          | 0.86mm <sup>2</sup> |

| Power consumption             | 97mW                |

| DNL                           | ±1.2 LSB            |

| INL                           | -1.5/+1 LSB         |

| SNR $(f_{in}=10\text{MHz})$   | 67.1 dB             |

| SNDR ( $f_{in}$ =10MHz)       | 64.2 dB             |

| SFDR (fin=10MHz)              | 69.4 dB             |

| ENOB (f <sub>in</sub> =10MHz) | 10.4 bit            |

Fig. 8. SFDR, SNR, and SNDR versus conversion rate. The input frequency and signal swing is 10 MHz and  $2V_{P-P}$ , respectively.

# Next Tuesday (2/3-10):

#### Chapter 12 Nyquist DACs

Du er her: UiQ > Studier > Emner > Matematikk og naturvitenskap > Informatikk > INF4420 > <math>V10 >

#### Undervisningsplan (INF4420 - Vår 2010)

| Dato       | Undervises<br>av                   | Sted                         | Tema                                                                | Kommentarer / ressurser                                       |

|------------|------------------------------------|------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------|

| 26.01.2010 | Snorre Aunet<br>("SA")             | Lille<br>Auditorium,<br>Ifi  | introduksjon<br>til INF4420                                         | Slides, Slides,<br>two per page.                              |

| 02.02.2010 | SA, Amir<br>Hasanbegovic<br>("AH") | Lille<br>Auditorium,<br>Ifi. | From chapter<br>8 i "Johns &<br>Martin". + SW<br>intro<br>(Cadence) | Slides. Slides.<br>two per page<br>Other relevant<br>material |

| 09.02.2010 | SA                                 | Lille Aud.                   | from chapters<br>8 and 9 in<br>"Johns &<br>Martin".                 | Slides. Slides.<br>two per page.                              |

| 16.02.2010 | SA                                 | Lille Aud.                   | 9.2-9.6, 10.1-<br>10.2                                              | Slides Slides<br>two per page                                 |

| 23.02.2010 | SA                                 | Lille Aud.                   | Chapter 10.3,<br>> , beg. of<br>chapter 11.                         |                                                               |

| 02.03.2010 | SA                                 | Lille Aud.                   | chapter 12;<br>Nyquist-rate<br>DACs                                 |                                                               |

| 09.03.2010 | SA                                 | Lille Aud.                   | cnapter 13;<br>Nyquist-rate<br>ADCs I                               |                                                               |

| 16.03.2010 | SA                                 | Lille Aud.                   | chapter 13;<br>Nyquist-rate<br>ADCs II                              |                                                               |

| 23.03.2010 | SA                                 | Lille Aud.                   | Chapter 14;<br>Oversampling<br>Converters                           |                                                               |

| 30.03.2010 |        |             |                                          | No teaching in week 13.                                  |

|------------|--------|-------------|------------------------------------------|----------------------------------------------------------|

| 06.04.2010 |        |             |                                          | No teaching in<br>week 14, due<br>to Easter<br>holidays. |

| 13.04.2010 | SA     | Lille Aud.  | chapter 16;<br>PLLs                      |                                                          |

| 20.04.2010 | SA, AH | Lille Aud.  | "project<br>meeting"                     |                                                          |

| 27.04.2010 | SA     | Lille. Aud. | To be defined.                           | In case                                                  |

| 10.05.2010 | AH     | Lille Aud.  | Selected problems relevant for the exam. |                                                          |

| 11.05.2010 | SA, AH | Lille Aud.  | presentation<br>of the project<br>work.  |                                                          |

Redaksjon: Redaksjon for informasion om studietilbudet ved UiO

Dokument opprettet: 26.12.2009, endret: 17.02.2010

#### Additional litterature

- Adnan Gundel, William N. Carr: A micropower sigma-delta A/D converter in 0.35 um CMOS for low-frequency applications, Proceedings of IEEE Long Island Systems, Applications and Technology Conference, IEEE 2007

- [GrTe86]: Roubik Gregorian, Gabor C. Temes: Analog MOS Integrated Circuits for signal processing, Wiley, 1986.

- [Haah94]: Nils Haaheim: Analog CMOS, Universitetet i Trondheim, Norges Tekniske Høgskole, 1994.

- Adel S. Sedra, Kenneth C. Smith: Microelectronic Circuits, Saunders College Publ., 1989.

- Kenneth R. Laker, Willy M. C. Sansen: Design of analog integrated circuits and systems, McGraw-Hill, 1994.

## Additional litterature:

1506

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 7, JULY 200

# A Cost-Efficient High-Speed 12-bit Pipeline ADC in 0.18-μm Digital CMOS

Terje Nortvedt Andersen, Bjørnar Hernes, *Member, IEEE*, Atle Briskemyr, Frode Telstø, Johnny Bjørnsen, *Member, IEEE*, Thomas E. Bonnerud, and Øystein Moldsvor

#### ANALOG-DIGITAL CONVERSION

Walt Kester

Editor

High speed data converters fully integrated in CMOS

by

Leif Hanssen