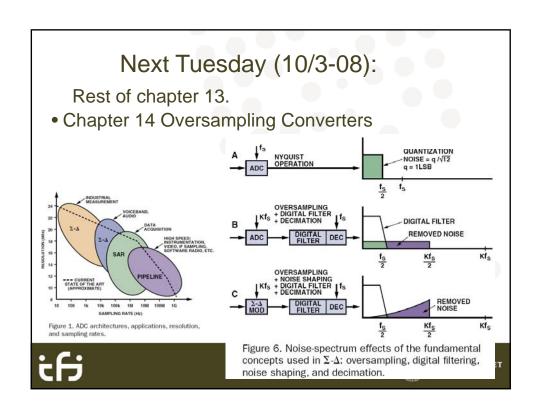

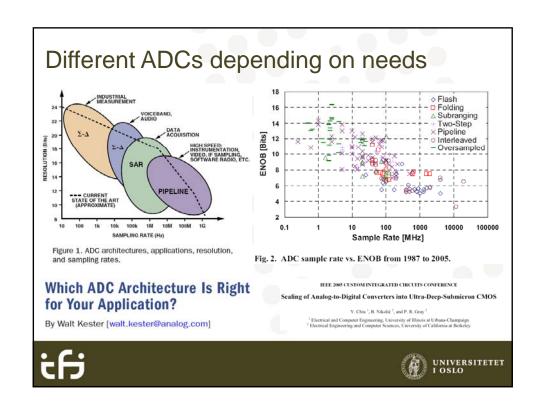

### Different A/D Converter Architectures

| Low-to-Medium<br>Speed<br>High Accuracy | Medium Speed<br>Medium Accuracy | High Speed<br>Low-to-Medium<br>Accuracy |

|-----------------------------------------|---------------------------------|-----------------------------------------|

| Integrating                             | Successive approximation        | Flash                                   |

| Oversampling                            | Algorithmic                     | Two-Step                                |

|                                         | 000                             | Interpolating                           |

|                                         |                                 | Folding                                 |

|                                         | 60                              | Pipelined                               |

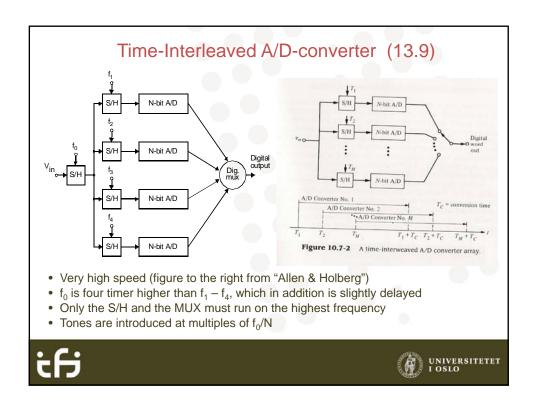

|                                         | 0                               | Time-interleaved                        |

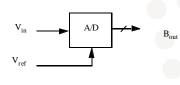

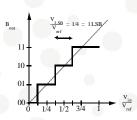

## A/D-conversion – Basic Principle

$$V_{ref}(b_1 2^{-1} + b_2 2^{-2} + ... + b_N 2^{-N}) = V_{in} \pm x$$

where

$$\left(-\frac{1}{2}V_{LSB} < x < \frac{1}{2}V_{LSB}\right)$$

- The analog input value is mapped to discrete digital output value

- · Quantization error is introduced

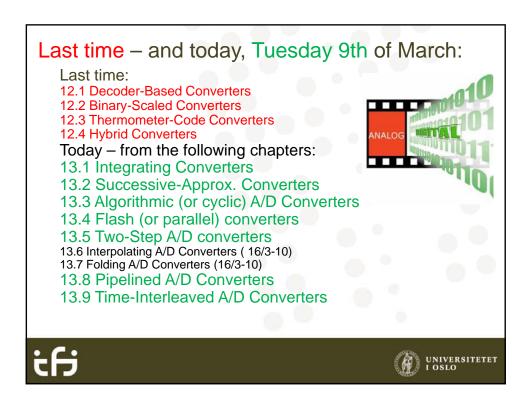

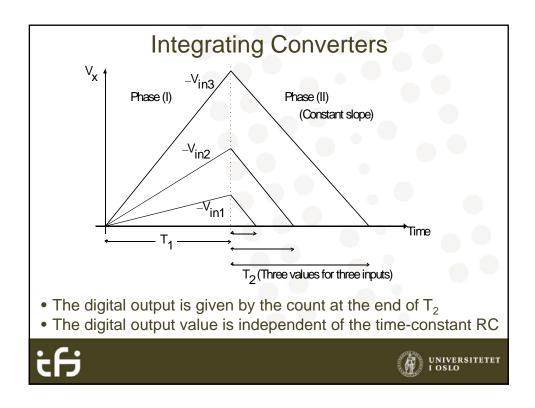

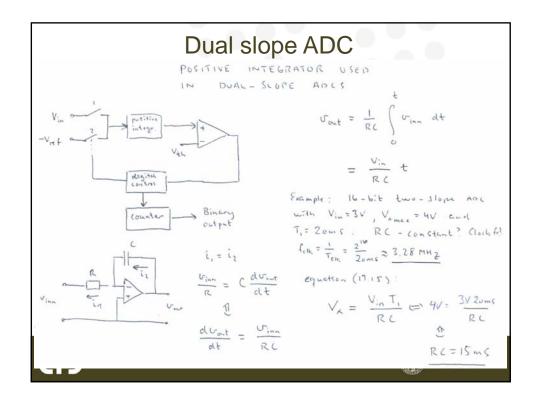

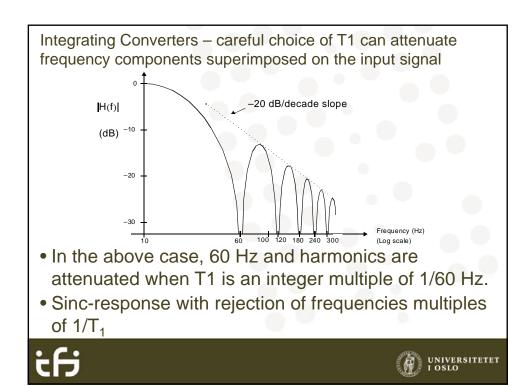

## **Integrating Converters (13.1)**

- $V_x(t) = V_{in} t / RC (V_x ramp derivative depending on V_{in})$

- High linearity and low offset/gain error

- Small amount of circuitry

- Low conversion speed

- 2<sup>N+1</sup> \* 1/T<sub>clk</sub> (Worst case)

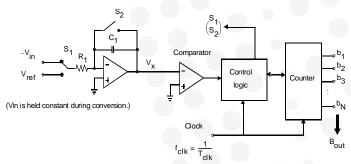

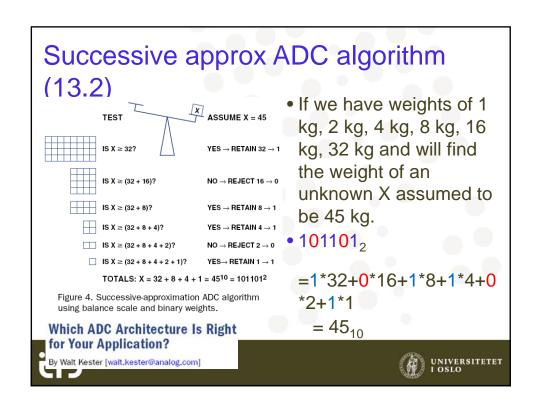

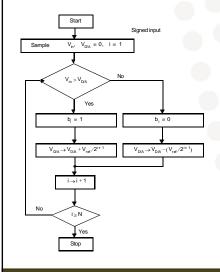

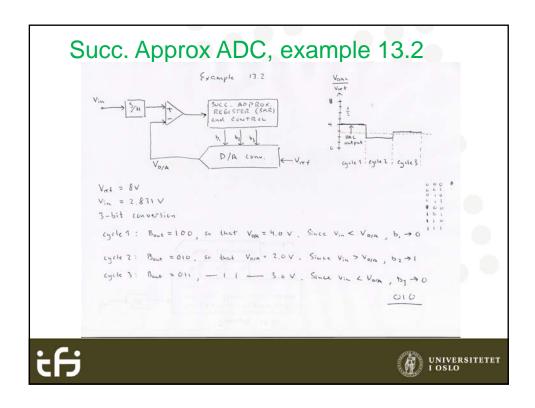

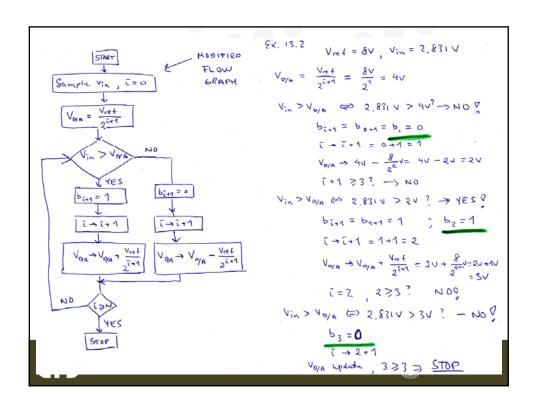

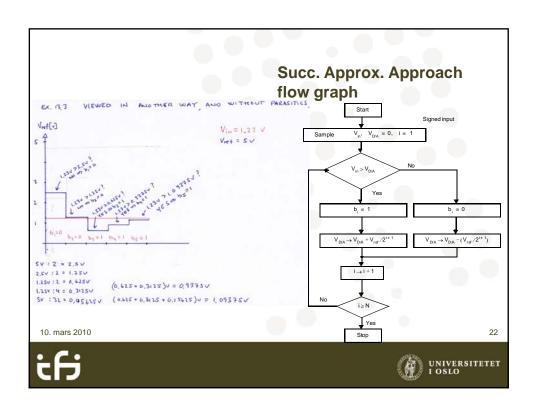

### Successive-Approximation Converters

- Uses binary-search algorithm

- Accuracy of 2<sup>N</sup> requires N steps

- The digital signal accuracy is within +/- 0.5

V<sub>ref</sub>

- Medium speed

- Medium resolution

- Relatively moderate complexity

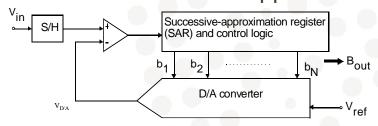

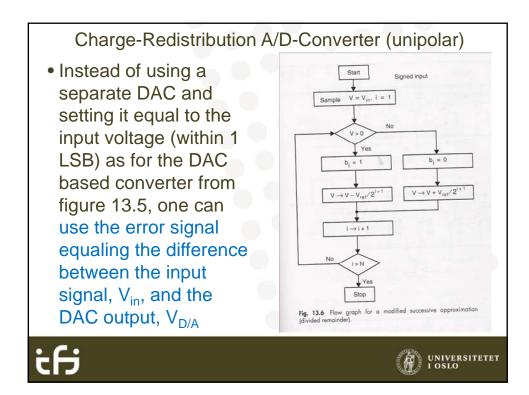

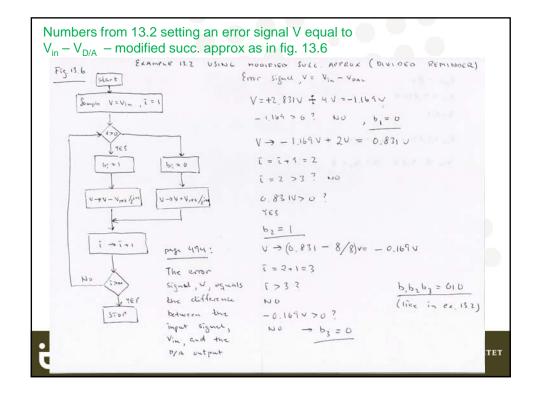

### **DAC-Based Successive Approximation**

- ullet  $V_{D/A}$  is adjusted until the value is within 1LSB of  $V_{in}$

- Starts with MSB and continues until LSB is found

- Requires DAC, S/H, Comparator and digital logic

- The DAC is typically limiting the resolution

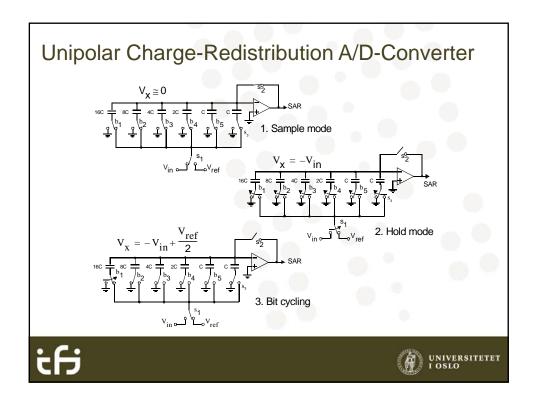

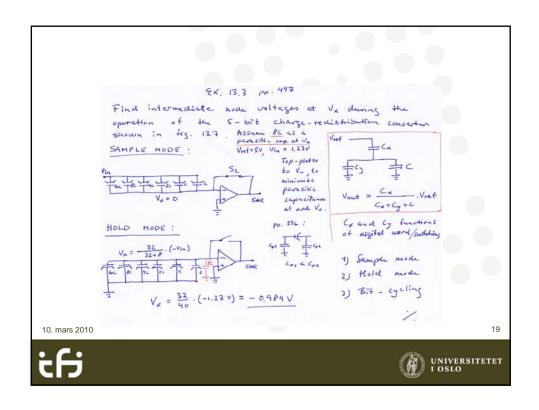

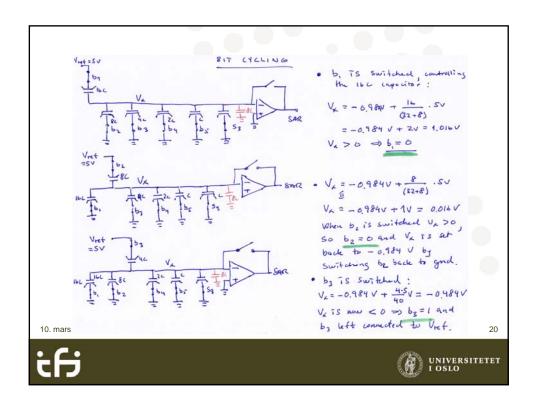

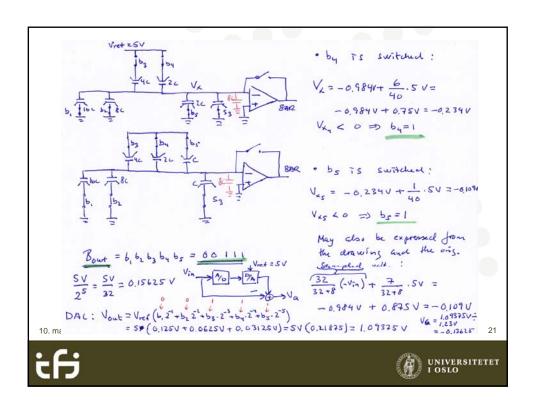

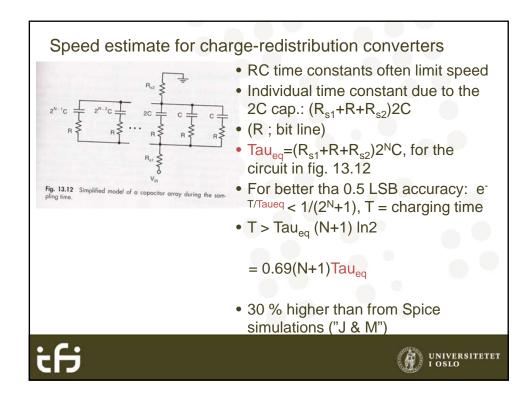

#### Charge-Redistribution A/D-Converter • Sample mode: All capacitors charged to Vin while the comparator is reset to its threshold voltage through S2. The capacitor array is performing S/H operation. · Hold mode: The comparator is taken out of reset by opening S2, then all capacitors are switched to ground. $V_x$ is now equal to $-V_{in}$ . Finally $S_1$ is switched so that $V_{ref}$ can be applied to the capacitors during bit-cycling. • Bit-cycling: The largest capacitor is switched to $V_{ref}$ . $V_x$ goes to $-V_{in} + V_{ref}/2$ . If $V_x$ is negative, then $V_{in}$ is greater than $V_{ref}/2$ and the MSB capacitor is left connected to $V_{\text{ref}}$ . Otherwise the MSB capacitor is disconnected and the same procedure is repeated N times

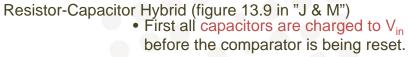

## Signed Charge redistribution A/D

(Fig. 13.8)

- Resembling the unipolar version (Fig. 13.7)

- Assming V<sub>in</sub> is between +/- V<sub>ref</sub>/2

- Disadvantage: V<sub>in</sub> attenuated by a factor 2, making noise more of a problem for high resolution **ADCs**

- Any error in the MSB capacitor causes both offset and a signdependent gain error, leading to **INL** errors

- Next a succ. approx. conversion is performed to find the two adjacent resistor nodes having voltages larger and smaller than V<sub>in</sub>

- One bus will be connected to one node while the other is connected to the other node. All of the capacitors are connected to the bus having the lower voltage.

- Then a successive approximation using the capacitor-array network is done, starting with the largest capacitor...

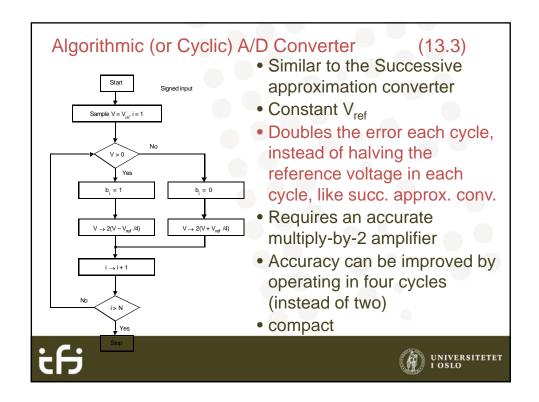

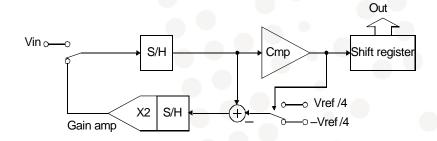

## Ratio-Independent Algorithmic Converter

- Simple circuitry

- Due to the cyclic operation the circuitry are reused in time

- Fully differential circuits normally used

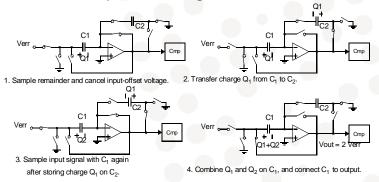

#### Ratio-Independent Algorithmic Converter

- The basic idea is to sample the input signal twice using the same capacitor.

During the 2<sup>nd</sup> sampling the charge from the 1<sup>st</sup> capacitor is stored on a 2<sup>nd</sup>

capacitor whose size is unimportant. After the 2<sup>nd</sup> sampling both charges are

recombined into the 1<sup>st</sup> capacitor which is then connected between the

opamp input and output.

- Does not rely on capacitor matching, is insensitive to amplifier offset.

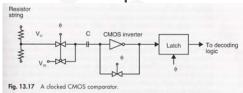

### Clocked CMOS comparator

- When the clock ("phi") is high, the inverter is set to its bistable point, Vin = Vout (= Vdd/2). The other (left) side of C is charged to V<sub>ri</sub>.

- When the clock ("phi") goes low, the inverter switches, depending on the voltage difference between V<sub>ri</sub> and V<sub>in</sub>. (V<sub>ri</sub> > V<sub>in</sub>; 1 output, V<sub>ri</sub> < V<sub>in</sub>; 0 output from inv.)

- Differential inverters helps poor PSRR with this simple comparator solution.

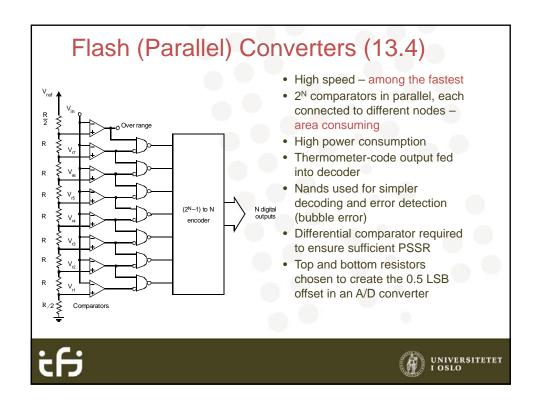

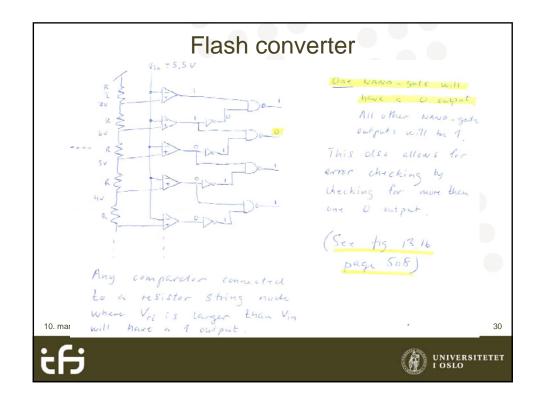

### Issues in Designing Flash A/D Converters

- Input Capacitive Loading: The large number of comparators connected to Vin results in a large capacitive load on at the input node which increases power and reduces speed

- Comparator Latch-to-Track Delay: The internal delay in the comparator when going from latch to track mode

- **Signal and/or Clock Delay:** Differences in signal/clock delay between the comparators may cause errors. Example: A250-MHz, 1-V peak input-sinusoid converted with 8-bit resolution requires a precision of 5ps. Can be reduced by matching the delays and capacitive loads on the signal/clock.

- Substrate and Power-Supply Noise: For a 8-bit converter with Vref=2V only 7.8mV of noise injection is required to introduce an error of 1LSB. The problem can be reduced by proper layout (Shielding, Differential clocks, Separate power supplies, and symmetrical layout)

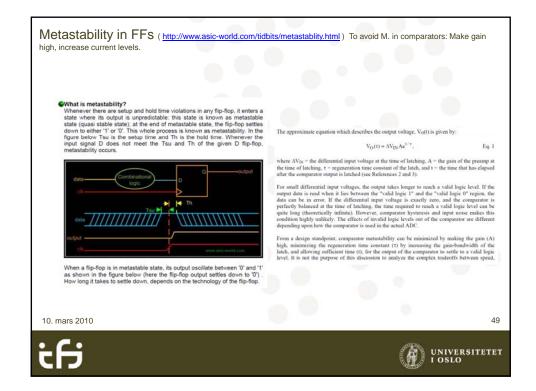

- Bubble Error Removal: Comparator metastability may introduce wrong thermometer code ( a single 1 or 0 in between opposite values)

- Flashback: Caused by latched comparators. When the comparator is switched from track to latch mode a charge glitch is introduced at the input. The problem is reduced by using a preamplifier and input impedance matching

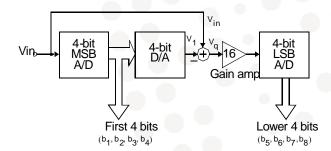

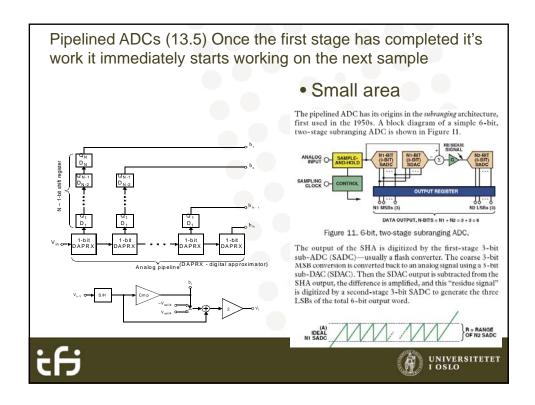

### Two-Step (Subranging) A/D Converters (13.5)

- Popular choice for high-speed medium accuracy converters (8-10 b)

- Less area and power consumption than a Flash ADC

- The MSB's are converted during the first step. In the next step the remaining error is converted into the LSB's

- Speed is limited by the Gain Amplifier

- Requires N-bit accuracy for all components (May be relaxed by using Digital Error Correction)

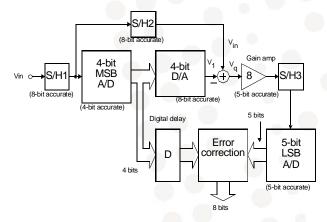

### Digital Error Correction for two-step A/D

The accuracy requirements on the input ADC is relaxed due to the error corr.. 4-bit for MSb converter

## Dynamic range

- Dynamic range is defined as the power of the maximum input signal range divided by the total power of the quantization noise and distortion

- Often referred to as Signal-to-Noise-and-Distortion range

- S/(N+D)

- SINAD

# Sampling-time uncertainty

•Variation in output voltage caused by variations in the time of sampling

Consider the following input signal:  $V_{in} = \frac{V_{ref}}{2} \sin(2\pi f_{in}t)$

If the variation in sampling time is  $\Delta t$  , following equation must be satisfied to keep  $\Delta V$  less than 1LSB

$$\Delta t < \frac{V_{LSB}}{\pi f_{in} V_{ref}} = \frac{1}{2^N \pi f_{in}}$$

### Additional litterature

- Phillip E. Allen, Douglas Holberg: CMOS Analog Circuit Design, Holt Rinehart Winston, 1987.

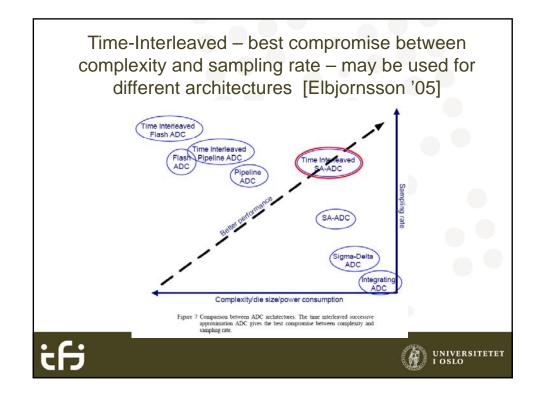

- Jonas Elbornsson: White paper on parallel successive approximation ADC, Mathcore Engineering AB, 2005.

- · R. Gregorian, G. Temes: Analog MOS Integrated Circuits for Signal Processing, Wiley, 1986

- D. M.Gingrich Lecture Notes, University of Alberta, Canada <a href="http://www.piclist.com/images/ca/ualberta/phys/www/http/~gingrich/phys395/notes/phys395.html">http://www.piclist.com/images/ca/ualberta/phys/www/http/~gingrich/phys395/notes/phys395.html</a>

- Walt Kester: Which ADC is right for your application?

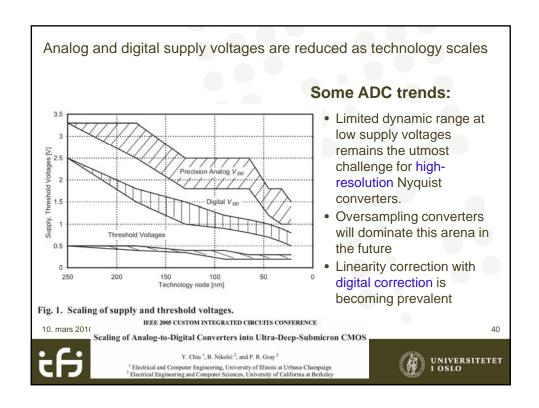

- Y. Chiu, B. Nicolic, P. R. Gray: Scaling of Analog-to-Digital Converters into Ultra-Deep-Submicron CMOS, Proceedings of Custom Integrated Circuits Conference, 2005.

- Lecture Notes, University of California, Berkeley,

- EE247 Analog Digital Interface Integrated Circuits, Fall 07;http://inst.eecs.berkeley.edu/~ee247/fa07/

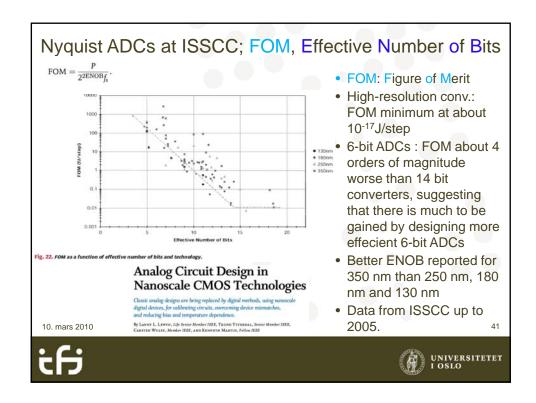

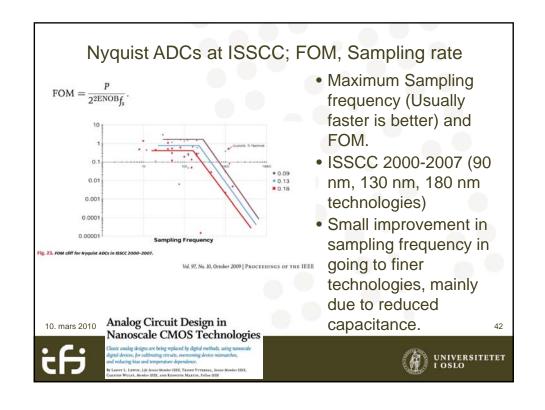

- Lanny L. Lewyn, Trond Ytterdal, Carsten Wulff, Kenneth Martin: "Analog Circuit Design in Nanoscale CMOS Technologies", Proceedings of the IEEE, October 2009.

- James L. McCreary, Paul R. Gray: "All-MOS Charge Redistribution Analog-to-Digital Conversion Techniques – part 1", IEEE Journal of Solid-State circuits, December 1975.

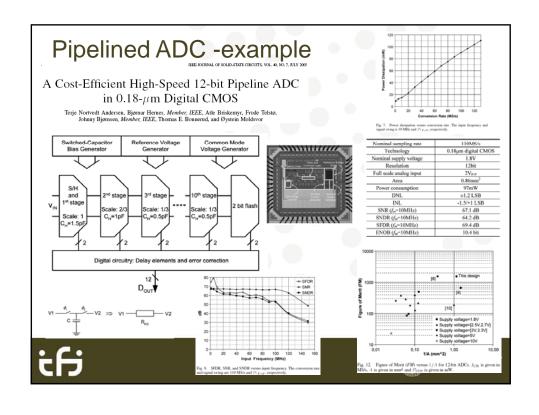

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 7, JULY 2005

## A Cost-Efficient High-Speed 12-bit Pipeline ADC in 0.18-µm Digital CMOS

Terje Nortvedt Andersen, Bjørnar Hernes, *Member, IEEE*, Atle Briskemyr, Frode Telstø, Johnny Bjørnsen, *Member, IEEE*, Thomas E. Bonnerud, and Øystein Moldsvor