University of Oslo

IN3160 IN4160 Datapath state machines Yngve Hafting

University of Oslo

In this course you will learn about the **design** of advanced digital systems. This includes programmable logic circuits, a hardware design language and system-on-chip design (processor, memory and logic on a chip). Lab assignments provide practical experience in how real design can be made.

After completion of the course you will:

- understand important principles for design and testing of digital systems

- understand the relationship between behaviour and different construction criteria

- be able to describe advanced digital systems at different levels of detail

- be able to perform simulation and synthesis of digital systems.

### **Course Goals and Learning Outcome**

https://www.uio.no/studier/emner/matnat/ifi/IN3160/index-eng.html

Goals for this lesson:

- Know what is

- Datapath state machines (FSMD)

- Know how to divide larger designs and state machines

- Principles

- Design strategies

- Divide and conquer-

Next lesson:

- Diagrams and schematics?

- Microcoded state machines

- Microcoded processors

### Overview

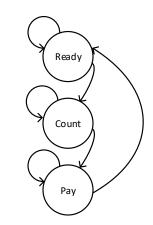

- What is data path finite state machines (FSMD)?

- Example with code and diagrams

- Factoring state machines

- When and how do we split

- Next lesson:

- Examples with diagrams and code

UiO **Contemportation** University of Oslo

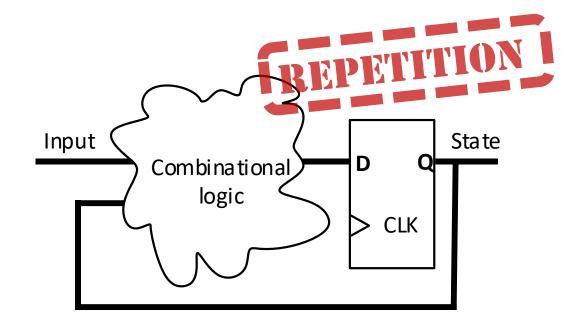

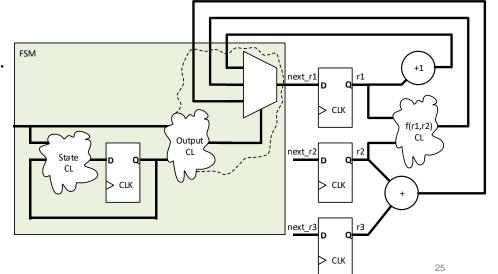

## **General FSM**

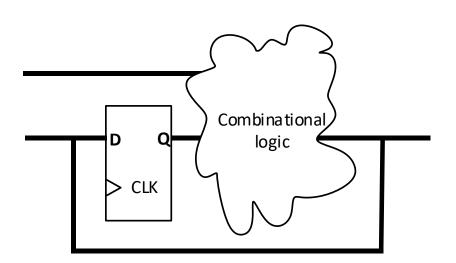

- General FSM

- Combinational logic connected to registers with feedback

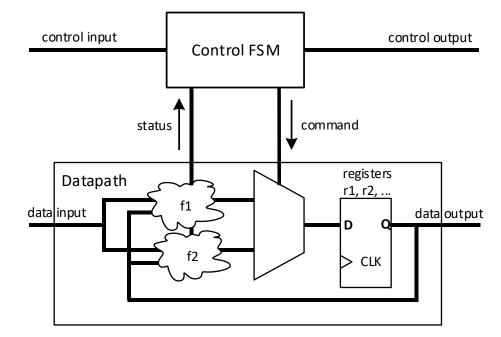

# «Datapath» FSM

- Datapath is described by a function rather than a table

- Counters

- Mathematical operations

- Shift registers

- Etc.

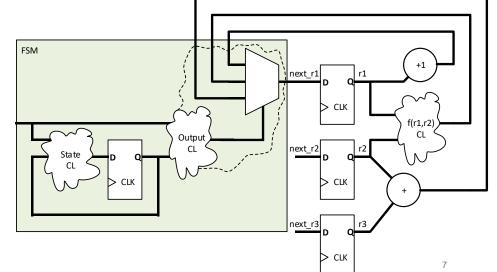

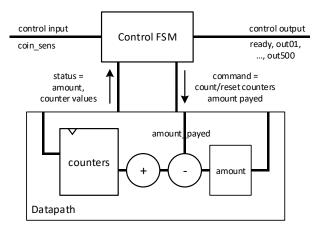

- We usually divide into control FSM and Datapath

# «Register operations» in data-path FSM (FSMD) -and how to deal with it

- Common notations for register operations:

- on clock edge we increment r1 -

- on clock edge we update r1 based on a function of register outputs  $\rightarrow r1 \leftarrow f(r1,r2)$

- on clock edge, set r1 to r2+r3

Solution:

Use ' $\leftarrow$ ' for datapath only (not for FSM) Know that ' $\leftarrow$ ' implies the use of registers that are not a part of the FSM states

\_\_\_\_\_ r1 ← r1 + 1

$r1 \leftarrow r2 + r3$

#### UiO **Content of Informatics**

University of Oslo

# Use of register in decision box

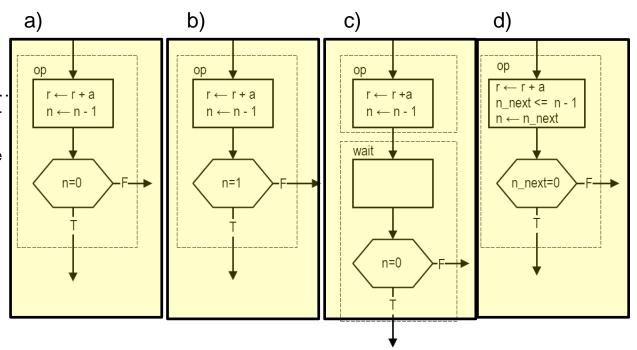

a) n will be updated after n=0 checkb) n will be updated after n=1 check..

- Even if we want this behavior, it is poor design...

- it seems we do not know what we are doing, as with a).

c) Do we need to introduce single cycle wait states?..

d) is clear about

- what we want and

- how we will do it

- => no doubt on our intention

- Register is updated when the FSM exits current state

NOTE: We "exit" current state each cycle- even if we re-enter...

- => Use solution d)!

RTL Hardware Design by P.Chu, Chapter 11

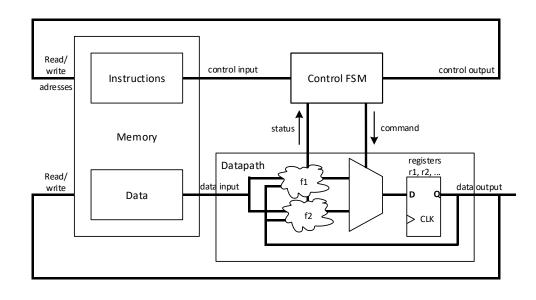

### **Processor system is a datapath FSM**

- Control output is memory instructions

- FSM decodes instructions and decides which part of the datapath is used

- Pipeline flushes, stalls etc.

- Datapath contains ALU, pipeline registers etc.

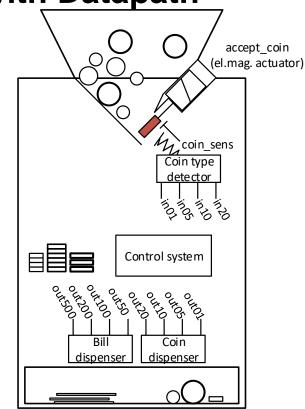

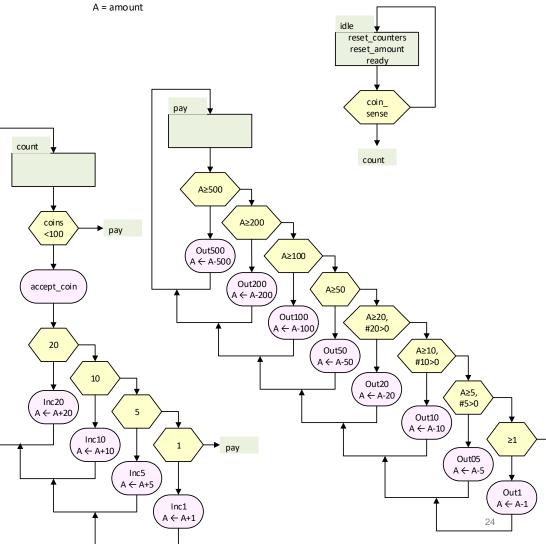

# Example Factoring state machine with Datapath

- Exhange machine

- Green LED 'ready'/ can accept coins

- Can take a number of up to 100 coins

- Count each coin type

- 1, 5, 10, 20 NOK

- Close intake at maximum (! Green)

- Close intake when counting

- Close intake when no more coins (assume new coin each clock edge)

- Give out the highest possible bills (assuming infinite supply)

- 50, 100, 200 NOK

- Return the least amount of coins

- Use only coin from machine

### When state count is nuts...

- Millions of states possible => Cannot make «one» FSM

- => several smaller state\_machines or state machine + data path with registers

### Divide into models that can be conquered

- Partition by ..?

- State (FSMs vs datapath),

- Task (counters, FSMs,...)

- Interface (entities)

- Entity:

• FSM(s)

• Datapath

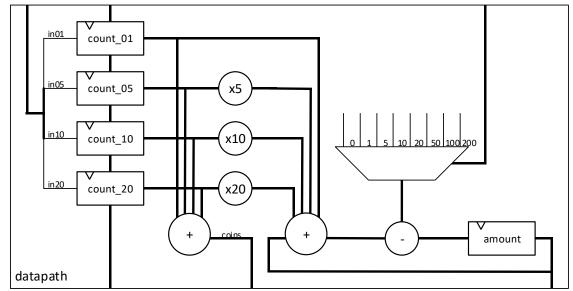

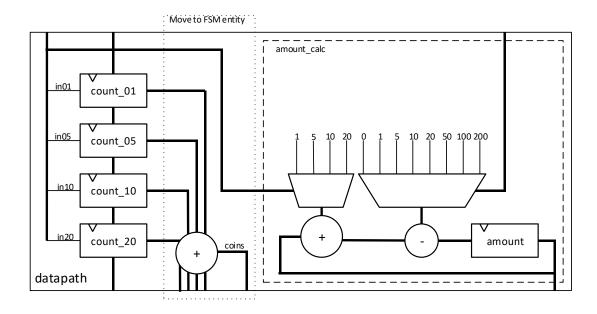

# **Detailed datapath**

- 4 counters

- Can they be of the same type?

- Up/ down / reset

- «Coins» and «amount»

- Why/ why not registers?

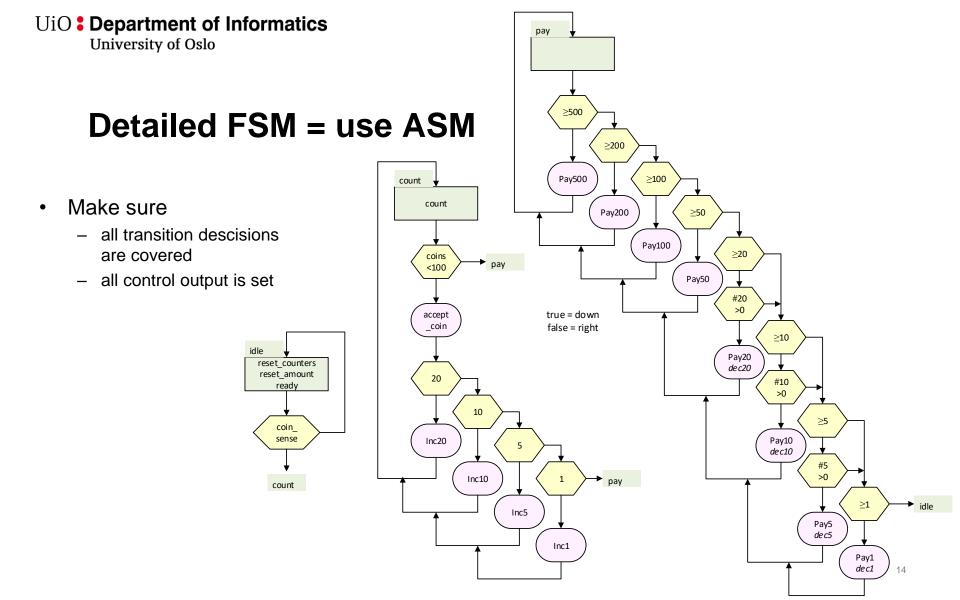

### **Reiterate and refine**

- You will likely need a couple of rounds refining before deciding on VHDL modules

- Entity

- FSM(s)

- Detailed datapath

- ASM diagrams

### **Example reiteration**

- Simpler by using

- Only increments or decrements for amount calculation

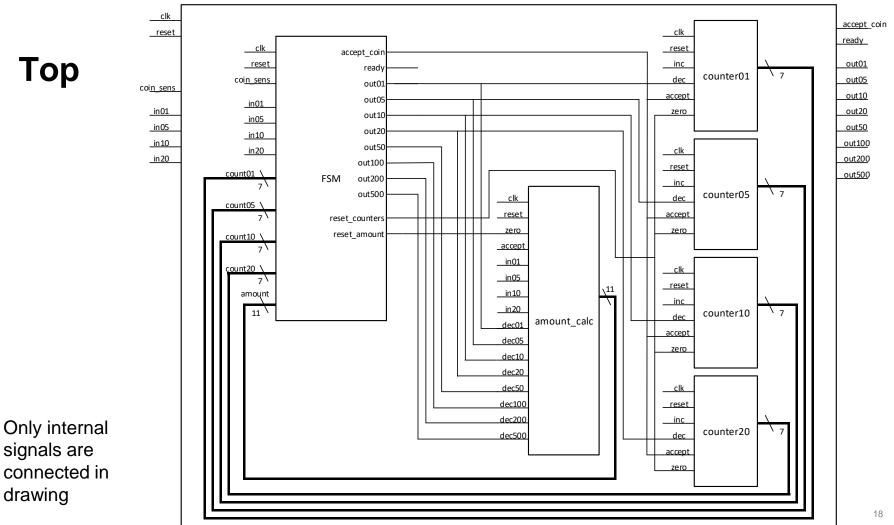

## VHDL modules and hierarchy

- What makes a good hierarchy?

- 1. Structural top

- 2. RTL

- 3. data flow modules

- Complex designs may have several structural layers

- Do not overdo this

- What makes good modules ..?

- One type of code within module

- (Structural vs RTL vs Data Flow)

- One purpose for each module

- Loosely coupled / few dependencies

- Minimum communication between modules

- Changes can be made within one module without changing an other

- Little or no duplicate code...

- Use functions, loops, constants etc.

- Scalable

- Example modules:

- Toplevel (structural)

- Control FSM

- Counter(s)

- One VHDL module, four instances

- Depath..?

- (course within toplevel...)

- Datapath .?

- Amount calculation

University of Oslo

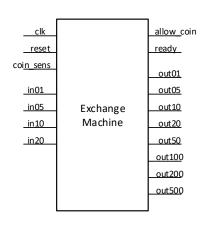

Exchange Machine

drawing

University of Oslo

### **Toplevel shell**

- Filling in the rest should be easy once the modules are ready

- We need names for signals that go between modules.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity exchange_machine is

port(

```

```

clk, reset : in std_logic;

coin_sens, in01, in05, in10, in20 : in std_logic;

ready, accept_coin : out std_logic;

out01, out05, out10, out20 : out std_logic;

out50, out100, out200, out500 : out std_logic

);

```

```

end entity exchange_machine;

```

```

architecture toplevel of exchange_machine is

component control_FSM is

port(

clk, reset : in std_logic);

```

```

component counter is

port(

clk, reset : in std_logic);

```

```

component amount_calc is

port(

clk, reset : in std logic);

```

-- signal decl. for communication between modules

begin

FSM: control FSM

port map(

clk => clk,

reset => reset);

```

count01: counter

port map(

clk => clk,

reset => reset);

```

```

count05: counter

port map(

clk => clk,

reset => reset);

```

```

count10: counter

port map(

clk => clk,

reset => reset);

```

```

count20: counter

port map(

clk => clk,

reset => reset);

```

```

amount: amount_calc

port map(

clk => clk,

reset => reset);

```

end architecture toplevel;

#### UiO **Content of Informatics**

University of Oslo

# Counter

- Processes can be used to sort priority by order

- OK when conditions are mutually exclusive?

- When-else can do the same sorting explicitly

- Less need for process..

```

library IEEE;

use IEEE.STD LOGIC 1164.all;

use IEEE.numeric std.all;

entity counter is

generic(

COUNT WIDTH : natural := 7);

port(

clk, reset : in std logic;

inc, accept : in std logic;

dec, zero

: in std logic;

: out unsigned(COUNT WIDTH-1 downto 0));

count

end entity counter;

architecture RTL of counter is

signal next count : unsigned(count'range);

begin

-- registry update

count <= (others => '0') when reset else next_count when rising_edge(clk);

--next count CL

next count <=</pre>

count + 1 when inc and accept else

count - 1 when dec else

(others => '0') when zero else

count;

```

end architecture RTL;

UiO **Content of Informatics**

University of Oslo

### amount\_calc

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.numeric std.all;

entity amount_calc is

generic(

--100*20 = 2000 < 2048 = 2^{11}.

AMOUNT WIDTH : natural := 11);

port(

: in std logic;

clk, reset

in01, in05, in10, in20

: in std_logic;

zero, accept coin

: in std logic;

dec50, dec100, dec200, dec500 : in std_logic;

dec20, dec10, dec05, dec01 : in std logic;

amount: out unsigned(AMOUNT WIDTH-1 downto 0));

end entity amount calc;

```

- Process + if because..

- Use of priority

- Several levels

- Single output can be resolved using when-else only

- Readability/Maintainability would suffer (...and accept\_coin x 4 )

```

architecture RTL of amount calc is

signal next amount : unsigned (amount'range);

begin

-- registry update

amount <=

(others => '0') when reset else

next amount when rising edge(clk);

-- CL next amount

process(all) is

begin

-- default statement:

next amount <= amount;</pre>

-- conditional statements (priority doesn't matter)

if zero then

next_amount <= (others => '0');

elsif accept_coin then

next amount <= amount + 1 when in01;</pre>

next amount <= amount + 5 when in05;</pre>

next amount <= amount + 10 when in10;</pre>

next amount <= amount + 20 when in20;</pre>

else

next amount <= amount - 500 when dec500;</pre>

next amount <= amount - 200 when dec200;</pre>

next amount <= amount - 100 when dec100;</pre>

next amount <= amount - 50 when dec50;</pre>

next amount <= amount - 20 when dec20;</pre>

next amount <= amount - 10 when dec10;</pre>

next amount <= amount - 5 when dec05;</pre>

next amount <= amount - 1 when dec01;</pre>

end if;

end process;

```

```

end architecture RTL;

```

University of Oslo

### FSM

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.numeric std.all;

entity control FSM is

generic(

COUNT WIDTH : natural := 7;

AMOUNT WIDTH : natural := COUNT WIDTH+4;

COIN LIMIT : natural := 100);

port(

clk, rese : in std logic;

coin sens, in01, in05, in10, in20 : in std logic;

count01 : in unsigned(COUNT WIDTH-1 downto 0);

count05 : in unsigned(COUNT WIDTH-1 downto 0);

count10 : in unsigned(COUNT WIDTH-1 downto 0);

count20 : in unsigned(COUNT WIDTH-1 downto 0);

amount : in unsigned(AMOUNT WIDTH-1 downto 0);

ready, accept coin : out std logic;

out01, out05, out10, out20 : out std logic;

out50, out100, out200, out500 : out std logic;

reset counters, reset amount : out std logic);

end entity control FSM;

```

```

architecture RTL of control_FSM is

type state_type is (idle, count, pay);

signal current_state, next_state : state_type;

signal coins : unsigned(COUNT_WIDTH-1 downto 0);

begin

```

```

-- clocked logic

current_state <=

idle when reset else

next_state when rising_edge(clk);</pre>

```

```

-- CL (moved from datapath)

coins <= count01 + count05 + count10 + count20;</pre>

```

```

next_state_cl: process(all) is

begin

-- default value prevents latches

next_state <= current_state;

case current_state is

when idle =>

next_state <= count when coin_sens;

when count =>

next_state <= pay when coins > COIN_LIMIT-1;

next_state <= pay when not (in01 or in05 or in10 or in20);

when pay =>

-- this should be equivalent to all tests listed

next_state <= idle when or(amount) = '0';

end case;

end process;</pre>

```

-- more next slide...

University of Oslo

### **FSM 2/2**

| <pre>output_cl: process</pre> | ( <mark>al</mark> : | l) is               |            |

|-------------------------------|---------------------|---------------------|------------|

| begin                         |                     |                     |            |

| default valu                  | ues                 | to prevent          | latching   |

| reset_counters                | <=                  | ' <mark>0</mark> '; |            |

| reset_amount                  | <=                  | ' <mark>0</mark> '; | NOTE: wi   |

| ready                         |                     | ' <mark>0</mark> '; | order, the |

| accept_coin                   | <=                  | ' <mark>0</mark> '; | becomes    |

| out01                         | <=                  | ' <mark>0</mark> '; |            |

| out05                         |                     | ' <mark>0</mark> '; | than nece  |

| out10                         | <=                  | ' <mark>0</mark> '; |            |

| out20                         | <=                  | ' <mark>0</mark> '; |            |

| out50                         | <=                  | ' <mark>0</mark> '; |            |

| out100                        | <=                  | ' <mark>0</mark> '; |            |

| out200                        |                     | ' <mark>0</mark> '; |            |

| out500                        | <=                  | ' <mark>0</mark> '; |            |

|                               |                     |                     |            |

- Readability? ٠

- What would happen if we mixed next\_state CL into the output CL?

NOTE: with this prioritation

becomes more complex

order, the sequence

than necessary.

- Default values for all signals ٠

- => no latches

- No need for else after when or if since default clause will apply.

- Use **«if**» to sort priorities, ٠ when having multiple conditions and multiple outputs - That are depending on each other..

```

case current state is

when idle =>

reset_counters <= '1';</pre>

reset amount <= '1';</pre>

ready <= '1';</pre>

when count =>

accept_coin <= '1' when coins < COIN LIMIT;</pre>

when pay =>

if amount >= 500 then out500 <= '1';</pre>

elsif amount >= 200 then out200 <= '1';</pre>

elsif amount >= 100 then out100 <= '1';</pre>

elsif amount >= 50 then out50 <= '1';</pre>

elsif amount < 50 and amount >= 20 then

if count20 > 0 then out20 <= '1';</pre>

elsif count10 > 0 then out10 <= '1';</pre>

elsif count05 > 0 then out05 <= '1';</pre>

else out01 <= '1';</pre>

end if:

elsif amount < 20 and amount >= 10 then

if count10 > 0 then out10 <= '1';</pre>

elsif count05 > 0 then out05 <= '1';</pre>

else out01 <= '1';</pre>

end if:

elsif amount < 10 and amount >= 5 then

if count05 > 0 then out05 <= '1';</pre>

else out01 <= '1';</pre>

end if:

elsif amount < 5 and amount >= 1 then

out01 <= '1';

end if;

end case;

end process;

```

```

end architecture RTL;

```

#### true = down false = right A = amount

# Recap ASMD

- D for datapath ASM

- '←' in a Mealy box?

- OK because the register is a part of the data path (and not the FSM itself)

- Can we go without ' $\leftarrow$ ' ?

- Should we?

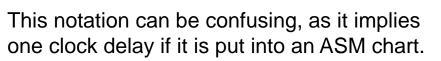

# «Register operations» in data-path FSM (FSMD) -and how to deal with it

- Common notations for register operations:

- on clock edge we update r1 based on a function of register outputs

- on clock edge we increment r1,

- on clock edge, set r1 to r1+r2

- This notation can be confusing, as it implies one clock delay if it is put into an ASM chart.

- Solution:

- Use '←' for datapath only (not for FSM)

- Know that '←' implies the use of additional registers

r1 ← r1 + 1

$r1 \leftarrow f(r1,r2)$

$r1 \leftarrow r2 + r3$

REPETITION

# **Suggested reading**

- D&H:

- 17 p 375 393

- 21 p 467 477

• Hva nå? <=

next\_page when time\_left > 15 min else questions ..?

# Pushbutton register storage (not in Oblig 6 2021)

- All storage elements should be clocked!

- should reset have top priority?

- Use asynchronous reset for the time being (topic for later)

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity my_reader is

port(

clk, reset : in std_logic;

enable : in std_logic;

input : in std_logic_vector(7 downto 0);

output : out std_logic_vector(7 downto 0);

);

end entity my_reader;

```

```

process(all) is

begin

if to be an opport of the second seco

```

```

architecture single_process of my_reader is

begin

process(clk, reset) is

begin

if reset then

ouput <= (others => '0');

elsif rising_edge(clk) then

ouput <= input when enable;

end if;

end process;

end architecture;

architecture two statement of my reader is</pre>

```

```

signal next out: std logic vector(7 downto 0);

begin

process(clk, reset) is

begin

if reset then

ouput <= (others => '0');

elsif rising edge(clk) then

ouput <= next out;</pre>

end if;

end process;

-- CL alternative

with enable select next out <=

input when '1',

output when others;

end architecture FSM style;

27

```

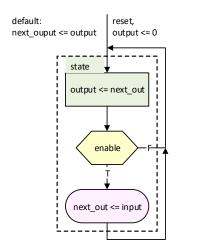

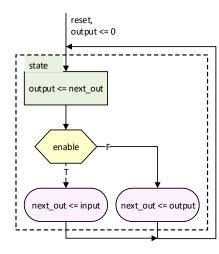

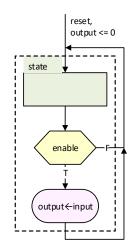

### Pushbutton register storage

Can be seen as a single state storage operation

With default value

• Without default

• As a register operation