## UiO: Institutt for informatikk Det matematisk-naturvitenskapelige fakultet

IN3160, IN4160 Digital system design

Introduction + HDL, PL and Design flow

Yngve Hafting

Det matematisk-naturvitenskapelige fakultet

#### **Overview**

- General information

- Course management

- Schedule

- Course Goals

- Curriculum

- Lab assignments

- Who are we

- Motivation

- Why Digital Design?

- Why HDL?

- Intro to programmable Logic

- What is programmable logic?

- Why choose programmable logic?

- Design Flow for digital designs

- Intro to our hardware…:

- Our hardware: Zedboard

- Architecture

- Documentation

- «Our» HDL: VHDL

- Assignments and suggested reading for this week

UiO: Institutt for informatikk

Det matematisk-naturvitenskapelige fakultet

## **Course Management**

- Lecturers:

- Roar Skogstrøm (II'er IFI, Kongsberg Defence Communications)

- Alexander Wold (II'er IFI, FFI)

- Yngve Hafting (Universitetslektor IFI/ROBIN)

- Lab supervisors / teachers:

- Arne Martin Dybendal Foldvik (Student)

- Georg Magneshaugen (Student)

- Karl Jørgen Giercksky Russnes (Student)

- Sander Elias Magnussen Helgesen (Student)

- Seyed Mojtaba Karbasi (PhD)

Det matematisk-naturvitenskapelige fakultet

#### Lectures

Tuesday 14:15 -16:00, Zoom (and OJD, C «3437»)

Thursday 12:15-14:00, Zoom (and OJD, C «3437»)

#### Lab

LISP (2428): No group education, lab supervision poll next slide <a href="https://www.mn.uio.no/ifi/om/finn-fram/apningstider/">https://www.mn.uio.no/ifi/om/finn-fram/apningstider/</a>

| Monday | Tuesday       | Wednesday | Thursday      | Friday |

|--------|---------------|-----------|---------------|--------|

|        |               |           |               |        |

|        |               |           | Lecture 12-14 |        |

|        | Lecture 14-16 |           |               |        |

|        |               |           |               |        |

#### Web

http://www.uio.no/studier/emner/matnat/ifi/IN3160/ (covers also INF4160)

UiO: Institutt for informatikk

Det matematisk-naturvitenskapelige fakultet

## Where do we stand + lab supervision poll?

- www.menti.com

- Code 8115 6823

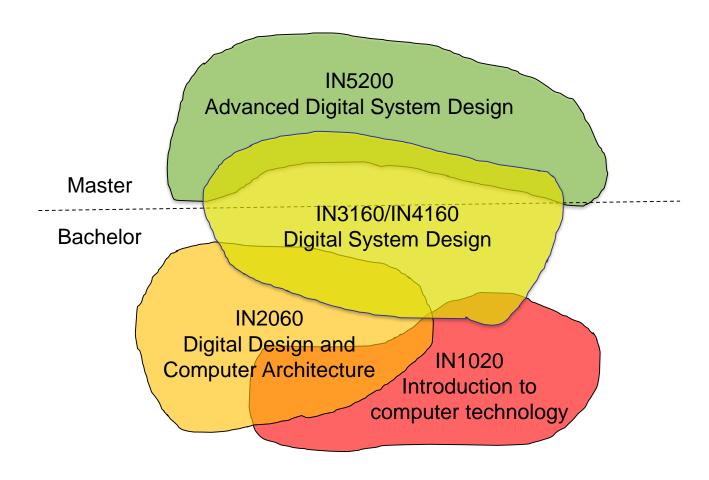

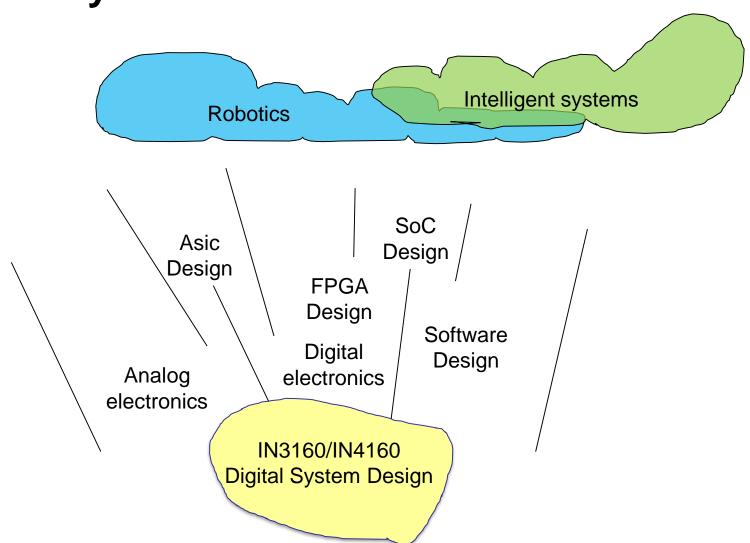

## **Study program connections**

Det matematisk-naturvitenskapelige fakultet

## Relevancy

UiO: Institutt for informatikk

Det matematisk-naturvitenskapelige fakultet

## **Course Goals and Learning Outcome**

https://www.uio.no/studier/emner/matnat/ifi/IN3160/index-eng.html

- In this course you will learn about the design of advanced digital systems.

- This includes programmable logic circuits, a hardware design language and system-onchip design (processor, memory and logic on a chip).

- Lab assignments provide practical experience in how real design can be made.

- After completion of the course you'll:...

#### ... IN3160 vs IN4160 ...

#### IN3160

- After completion of the course you'll:

- understand important principles for design and testing of digital systems

- understand the relationship between behavior and different construction criteria

- be able to describe advanced digital systems at different levels of detail

- be able to perform simulation and synthesis of digital systems.

#### IN4160

- After completion of the course you'll:

- understand important principles for design and testing of digital systems

- understand the relationship between behavior and different construction criteria

- be able to describe advanced digital systems at different levels of detail

- be able to perform advanced simulation and synthesis of digital systems

- be able to perform advanced implementation and analysis techniques

**NOTE**: these are MINIMUM requirements for passing an exam.

- You will be given the same opportunities to learn, and the curriculum is the same.

- Grading will be stricter for IN4160 due to added minimum requirements

- Otherwise, this course will be held as one.

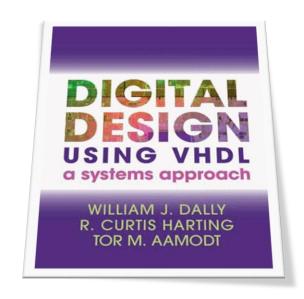

## **Syllabus**

Dally, William J. - Harting, R. Curtis - Aamodt, Tor M.

Digital Design Using VHDL A Systems Approach

Cambridge University Press 2016

ISBN9781107098862

- Lectures and lecture slides

- Mandatory assignments

- Handouts

- Cookbook (will be available digitally)

- Articles

Det matematisk-naturvitenskapelige fakultet

## Compulsory lab assignments

- There are 10 compulsory lab assignments.

- All assignments must be completed to take the exam.

- Lab workload increases through the semester

- Lectures are prerequisite for some assignments

- Lectures most intensive in the beginning

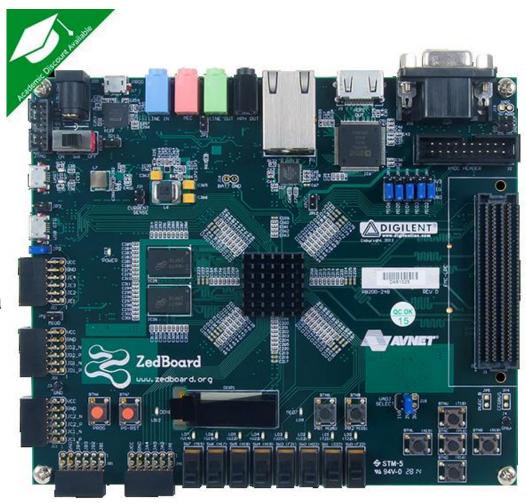

- The lab assignments utilises the digilent Zedboard, featuring a Xilinx Zynq 7020 device that includes both a hardcoded ARM processor and FPGA fabric.

- By the end of this course you will design a system, using both processor and FPGA fabric, that will both regulate, read and display the speed of an electric motor connected to the board.

https://store.digilentinc.com/zedboard-zynq-7000-arm-fpga-soc-development-board/

Det matematisk-naturvitenskapelige fakultet

### **General information**

| Vortex (Course web)                                                                                                                                                                                        | Canvas                                                                                                        | Discourse                                                                 | https://astro-discourse.uio.no/ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|

| <ul> <li>Mostly open for all</li> <li>General course information<br/>(Exam dates, etc)</li> <li>Lecture schedule with lecture<br/>notes and screencast</li> <li>Announcements</li> <li>Syllabus</li> </ul> | <ul> <li>Enrolled students</li> <li>Mandatory     assignments</li> <li>Feedback on     assignments</li> </ul> | <ul><li>Enrolled students</li><li>Discussions</li><li>Questions</li></ul> |                                 |

- Lab starts now! (Expect to use much time on the last few assignments)

- Assignments are available in Canvas!

- Assignments are individual.

- There will be one assignment using peer review only.

- Some assignments may require that you show your setup to the lab supervisor.

- Last year showed us labs can be done entirely remote, but on-site is strongly adviced.

- LISP (2428) is the LAB.

- Both hardware and software will be available in LISP.

- 4 boards with camera will be available online for those in quarantine/ isolation / specieal needs.

Questions..?

Det matematisk-naturvitenskapelige fakultet

IN3160 Introduksjon, HDL og PL

Hardware Description Language & Programmable Logic

Yngve Hafting

Det matematisk-naturvitenskapelige fakultet

Wikipedia: U.S. Navy photo by Photographer's Mate Airman

Marvin E. Thompson Jr.

https://www.komplett.no/product/11257/pc-nettbrett/komplett-pc/komplett-gamxtreme/komplett-gamer-xtreme-i250?offerId=KOMPLETT-310-11257#

Det matematisk-naturvi

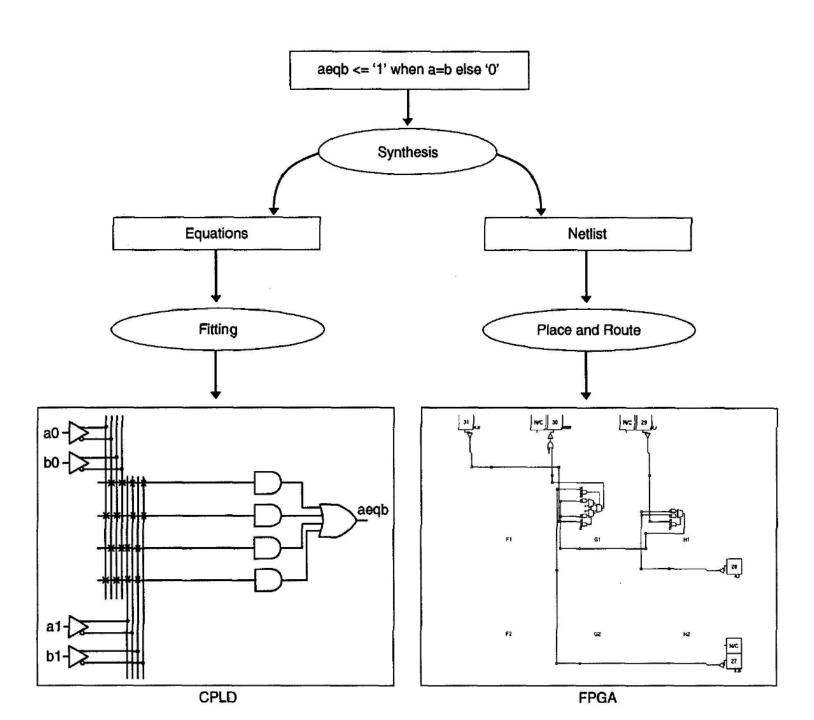

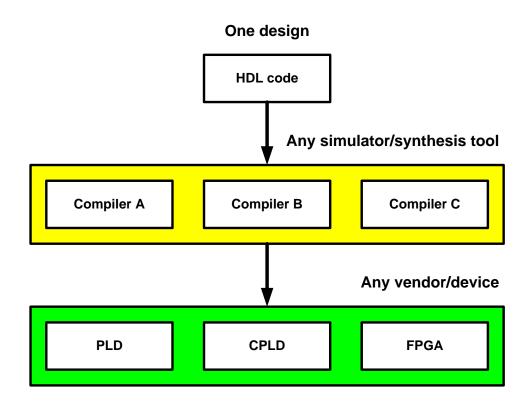

## Why HDL?

Syntesis to design

Det matematisk-naturvitenskapelige fakultet

## Why HDL?

- Technology independent code

- Different abstraction layers

| Netlist:                                                                                                       | Boolean equations:                                                          |  |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| U1: xor2 port map(a(0), b(0), x(0)); U2: xor2 port map(a(1), b(1), x(1)); U3: nor2 port map(x(0), x(1), aeqb); | <pre>aeqb &lt;= (a(0) xor b(0)) nor (a(1) xor b(1));</pre>                  |  |

| Concurrent statements:                                                                                         | Sequential statements:                                                      |  |

| aeqb <= '1' when a=b else '0';                                                                                 | <pre>if a=b then     aeqb &lt;= '1'; else     aeqb &lt;= '0'; end if;</pre> |  |

INF3430 / INF4431

16

Det matematisk-naturvitenskapelige fakultet

## Why HDL?

- Portability

- IEEE Standards

- VHDL/System Verilog are both IEEE (Institute of Electrical and Electronics Engineers) standards

- VHDL IEEE 1076

- System Verilog IEEE 1364

Det matematisk-naturvitenskapelige fakultet

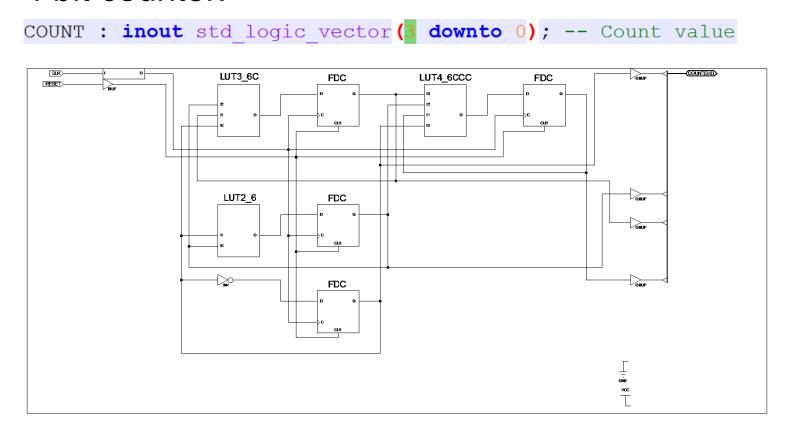

## Why HDL?

Simple mainteenance/expansion of a design

```

COUNT : inout std logic vector (7 downto 0); -- Count value

COUNTER:

process (RESET, CLK)

begin

if(RESET = '1') then

COUNT <= (others => '0');

elsif rising edge (CLK) then

COUNT <= COUNT + 1;

end if;

end process COUNTER;

```

Det matematisk-naturvitenskapelige fakultet

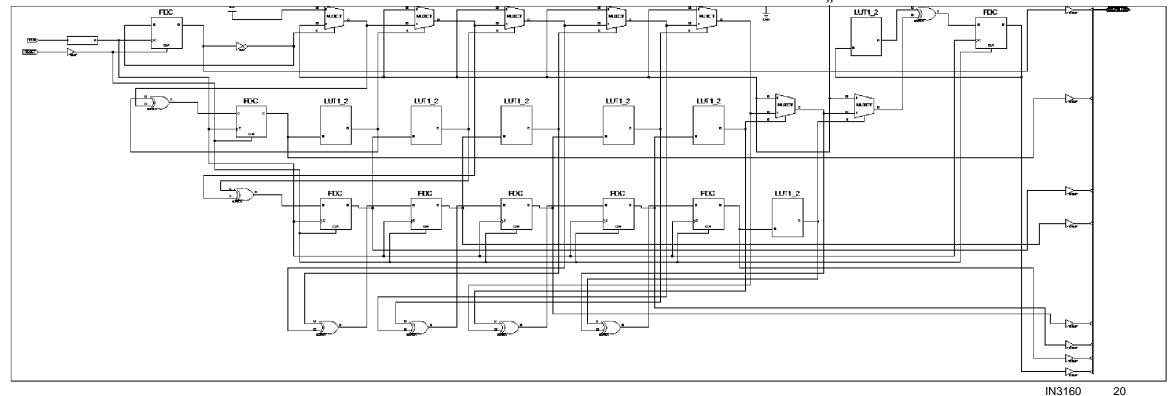

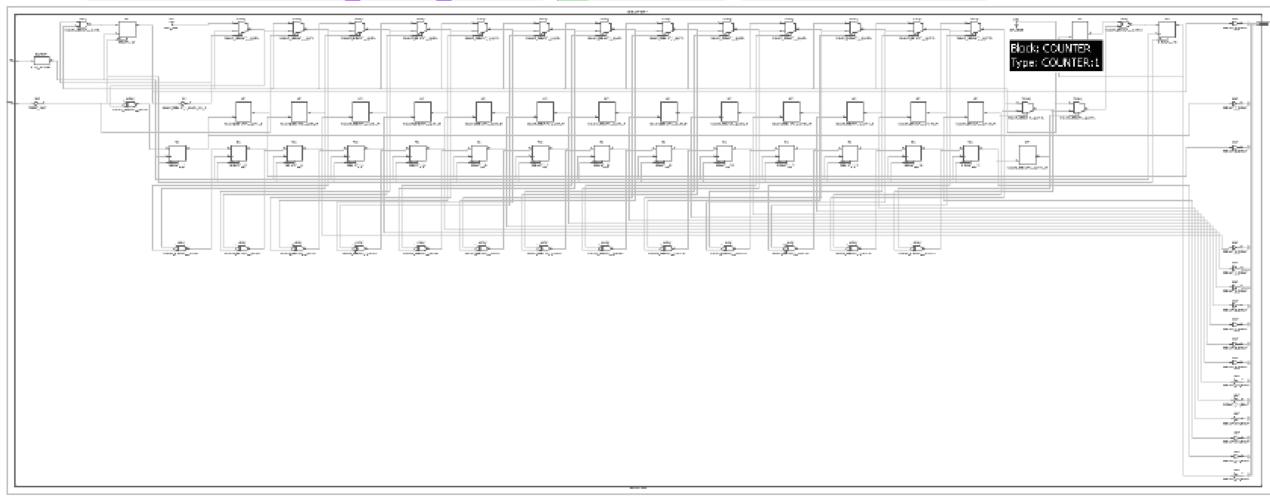

## Why HDL?

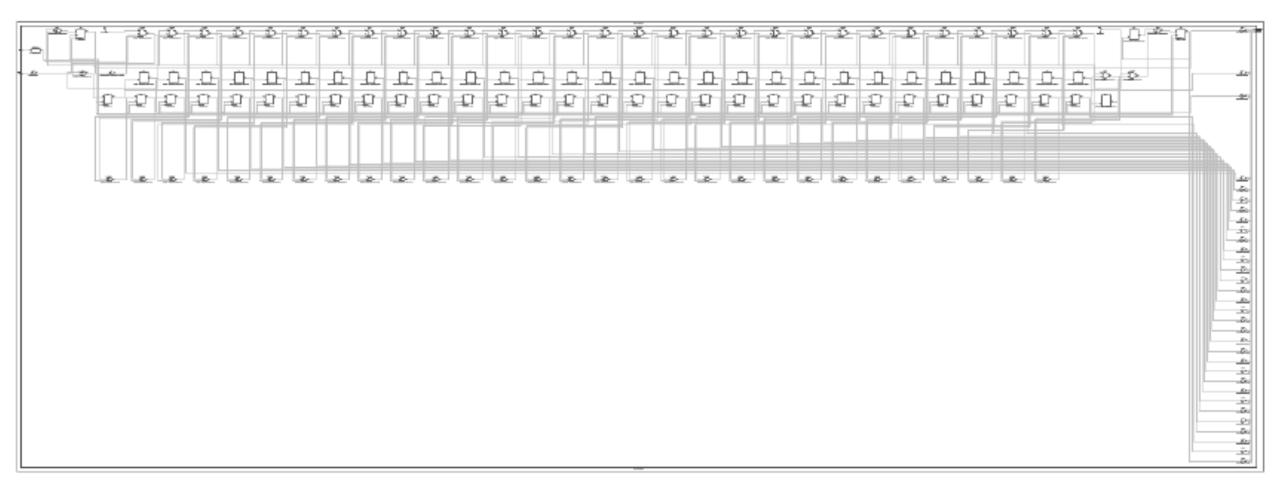

## 4 bit counter:

Det matematisk-naturvitenskapelige fakultet

8 bit ...

COUNT : inout std logic vector (7 downto 0); -- Count value

Det matematisk-naturvitenskapelige fakultet

16 bit ...

COUNT : inout std logic vector (15 downto 0); -- Count value

Det matematisk-naturvitenskapelige fakultet

32 bit...

COUNT : inout std logic vector (31 downto 0); -- Count value

Det matematisk-naturvitenskapelige fakultet

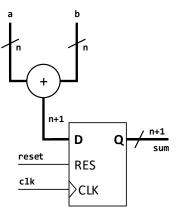

#### **HDL** vs software

| <pre>process(reset, clk)</pre>    |      |

|-----------------------------------|------|

| begin                             |      |

| if (reset = '1') then             |      |

| sum <= '0';                       |      |

| <pre>elsif rising_edge(clk)</pre> | then |

| sum <= a + b;                     |      |

| end if;                           |      |

| end process;                      |      |

|                                   |      |

```

Software programs

HDL «Hardware description

language»

Defines the sequence of instructions

Defines the logic function of a circuit

and which data shall be used for one or

more processors or processor cores

CAD tools syntetizises designs to

A compiler translates program code to

enable realization using physical gates.

machine code instructions that the

processor can read sequentially from

memory

Implemented using programmable

Is stored in computer memory

logic (PL, FPGA, CPLD, PLD, PAL, PLA, ...)

or AS/Cs (application specific circuits)

("ASICs", processors, ..-chips,.. etc.)

Verilog (SystemVerilog)

C, C++, C#, Python, Java, assemblere

(VHDL 2008)

(ARM, MIPS, x86, ...) Fortran, LISP,

Simula, Pascal, osv...

(System C m. fl.)

```

Det matematisk-naturvitenskapelige fakultet

#### HDL

- VHDL = VHSIC HDL:

- Very High Speed Integrated Circuit

Hardware Description Language

- The purpose is to generate hardware, and verify it through simulation.

- Synthesizable (realizable) code work concurrently (in parallel).

- Code for simulation include things such as file I/O which cannot be synthesized.

- Testbenches can and will use some synthesizable elements, but will in general look more like other sequential languages, and use sequential statements.

This may be confusing at times...

- VHDL does come with several libraries.

**HDL**

Code for generating and parsing simulation data (Test benches)

Det matematisk-naturvitenskapelige fakultet

# What is PL? (Programmable Logic)

- PL = FPGA, CPLD, PLA...

(Field Programmable Gate Array,

Complex Programmable logic Device)

- PL vs processor (FPGA vs CPU, MCU) ?

- PL vs ASIC (Application Specific Integrated circuit)?

UiO: Institutt for informatikk

Det matematisk-naturvitenskapelige fakultet

# When or why choose programmable logic?

- (Verify behavior of ASIC)

- Prototyping flexibility

- Lots of multi purpose IO

- Reprogrammable

- Small batch production

- Parallellism

- Custom / fast

- Runtime reconfigurability

•

# When to avoid programmable logic?

- When low component cost is extremely important.

- When dedicated HW is well suited.

- When extreme speed is required => ASIC

•

Det matematisk-naturvitenskapelige fakultet

**IN3160**

Digital Design Flow

Yngve Hafting

Det matematisk-naturvitenskapelige fakultet

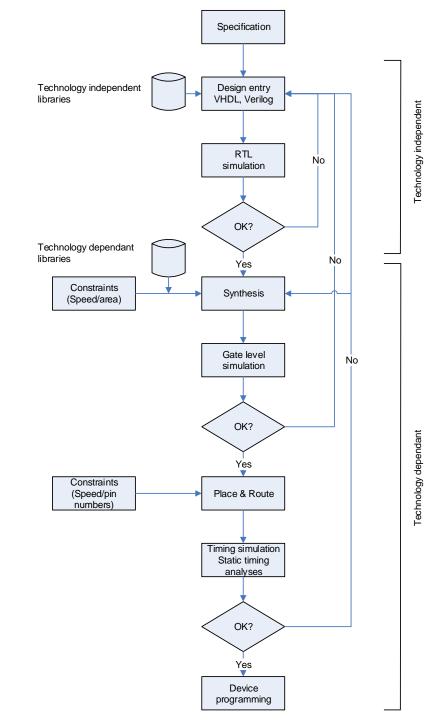

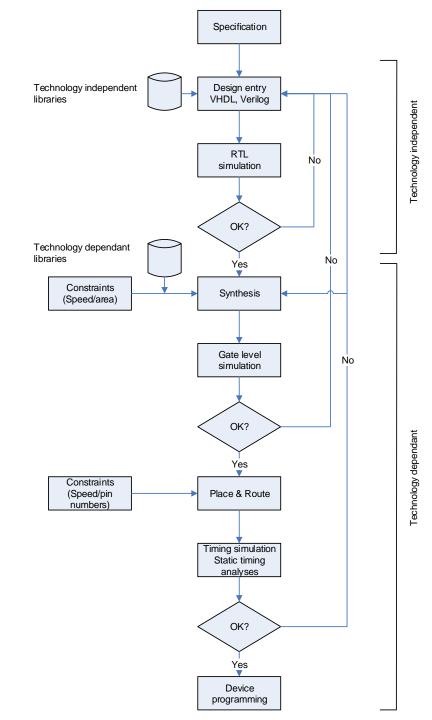

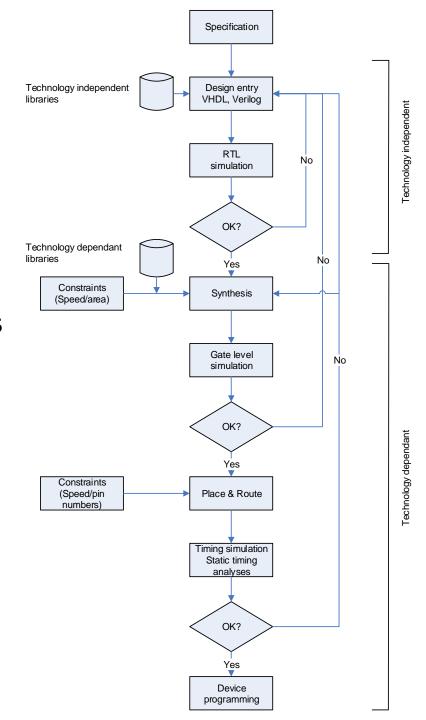

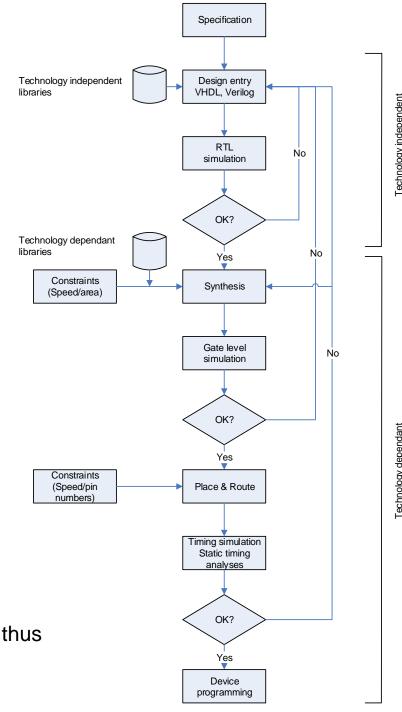

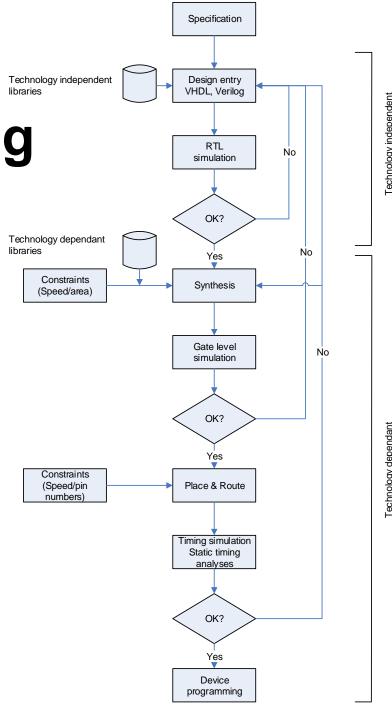

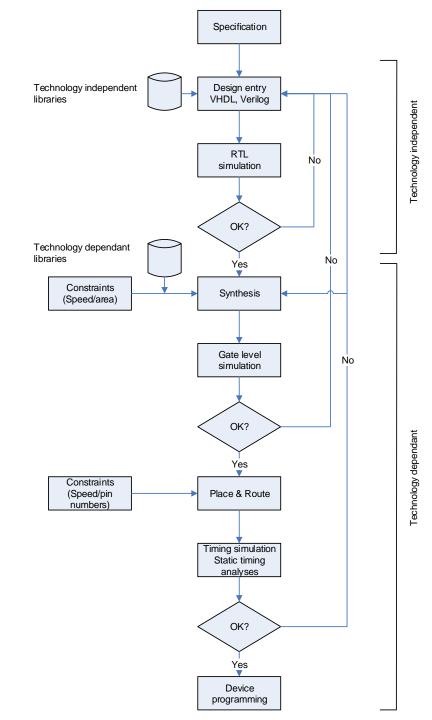

## **Overview**

- Digital design tools.

- Specification

- Design entry, synthesis and PAR

- Timing analysis

- Timing simulation

- Testing

Det matematisk-naturvitenskapelige fakultet

## Digital Design tools...

- Design entry:

- Use your favourite HDL text editor

(Notepad++, Emacs, Vivado or Questa).

- Simulation (RTL, Gate Level, Timing)

- Here: Typically using Questa (=Modelsim)

- Synthesis, Implementation, Programming

- Vendor specific tools,

- Here: Vivado by Xilinx

- Also possible: Digilent tools for programming.

Det matematisk-naturvitenskapelige fakultet

## **Digital Design Flow: Specification**

- 1. Define the problem

- 2. Draw a functional diagram

- block diagram with major components and connections

- 3. Identify IO requirements

- 4. Identify necessary interface circuits

- 5. Decide on HDL (VHDL, Verilog, System C,...)

- 6. Draw a program flowchart (ASM diagram)

- Defines how the design shall work logically.

- By hand or using tools such as:

- Visio, Draw.io, Lucid chart, etc.

Det matematisk-naturvitenskapelige fakultet

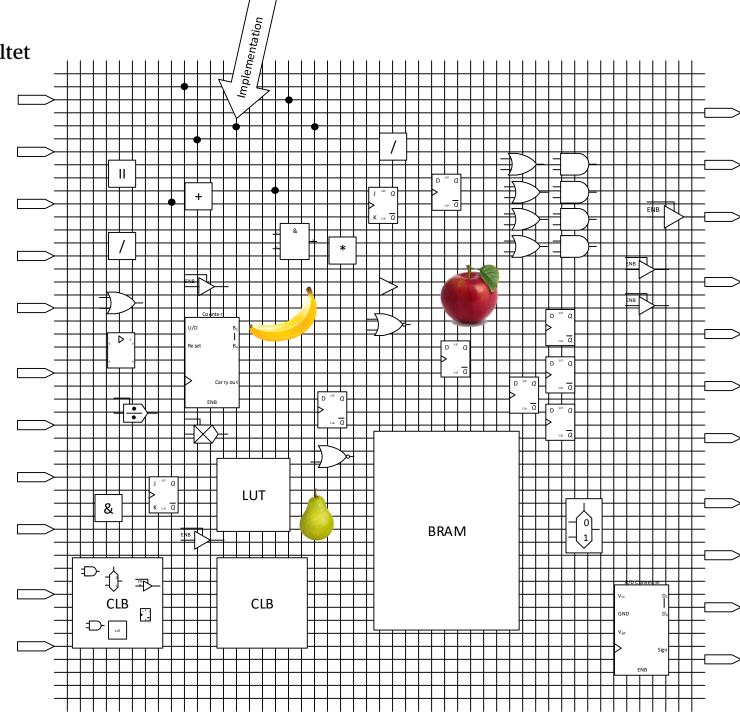

## Design entry, synthesis and PAR

- RTL = Register Transfer Level

- RTL does not use specific gates or technology

- Designs are mostly done in RTL

- RTL simulation can be used to verify logic function.

- Gate level synthesis

- Technology specific gates are selected for all components in the design.

- Typically a synthesizer will pick gates specific for the (FPGA) chip family we use.

- Once we have a gate level design we can

- · calculate gate-, but not propagation delays

- Simulate using gate delays.

- Place and route

- After synthesis gates can be placed within a specific (FPGA) chip.

- When place and route is performed propagation delays may also be simulated thus

- We can do all timing simulation, including propagation delays.

## Static timing analysis

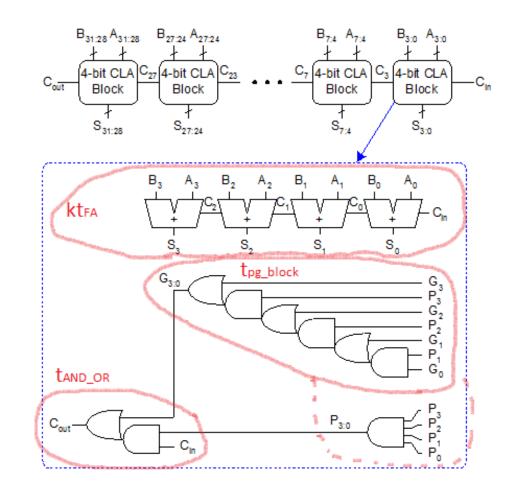

## **IN2060:** Carry-Lookahead Adder Delay

For *N*-bit CLA with *k*-bit blocks:

$$t_{CLA} = t_{pg} + t_{pg\_block} + (N/k - 1)t_{AND\_OR} + kt_{FA}$$

$-t_{pg}$ : delay to generate all  $P_i$ ,  $G_i$

-  $t_{pg\_block}$ : delay to generate all  $P_{i:j}$ ,  $G_{i:j}$

$-t_{

m AND\_OR}$ : delay from  $C_{

m in}$  to  $C_{

m out}$  of final AND/OR gate in  $\emph{k}$ -bit CLA block

An N-bit carry-lookahead adder is generally much faster than a ripple-carry adder for N > 16

- Performed by EDA tools on synthesized or routed designs

- Will attempt to

- find critical path(s) and

- check if timing requirements (constraints) can be met.

## Timing simulation, programming

- Simulating synthesized or routed designs

- Can use the same testbench as for RTL designs

- Verification and test benches will be discussed further later...

- Uses timing information for every component in use.

- Requires much more resources than RTL simulation.

- Can be slow for complex designs

- · Hence the option to simulate at gate level, before performing PAR.

- Device programming...

- (Usually done from vivado, but third part tools *may* be used).

Det matematisk-naturvitenskapelige fakultet

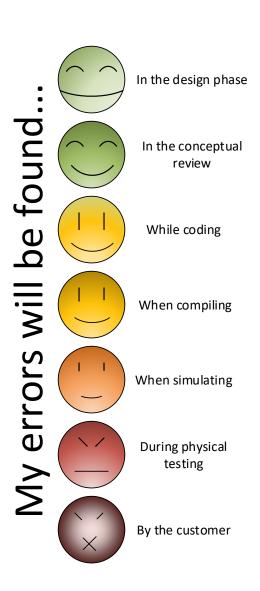

## **Testing**

- "Testing" is to find physical errors in a device.

- «Verification» is to check the design

- although we use *«test benches»* for simulation

- Design for testability

- Means that we design for physical testing.

- We may touch this later in the course.

- Spend more time in early phases!

- Avoid spending much more time fixing bugs later

### Introduction to course hardware and software tools

- Zedboard

- Questa

- Vivado

ROBIN wiki:

https://robin.wiki.ifi.uio.no/Hovedside

- Software

- FPGA tools

https://robin.wiki.ifi.uio.no/FPGA\_tools

- Cook book and ZedBoard documentation

- Canvas IN3160

- Cookbook\_v3\_5.pdf

- ZedBoard HW UG vX\_X.pdf

- Zynq intro video:

https://www.xilinx.com/video/soc/zedboard-overview-featuring-zynq.html

Det matematisk-naturvitenskapelige fakultet

## Digital Design tools...

- Design entry:

- Use your favourite HDL text editor

(Notepad++, Emacs, Vivado or Questa).

- Simulation (RTL, Gate Level, Timing)

- Here: Typically using Questa (=Modelsim)

- Synthesis, Implementation, Programming

- Vendor specific tools...

- Here: Vivado by Xilinx

Det matematisk-naturvitenskapelige fakultet

#### Simulation and test benches

- Simulation can be run using three different approaches:

- 1. Manually setting inputs and specifying time intervals in the GUI or console

- This way is tedious if much testing is to be done.

- Normally this is only done initially.

- 2. To make scripts (tcl for Questa) in a separate (.do) file.

- The script commands will be added to the console during manual use, and can be copied as text into a .do file.

- setting up the simulation windows can be done reusing script commands.

- 3. Create a test bench in VHDL

- This is the preferred method

- possible in combination with running scripts

- VHDL can be used to generate code for applying test vectors sequentially to the inputs of an entity for simulating.

- Test bench code is not synthesizable

- easy to read and use test data for each particular design,

- Can be used both prior and post synthesis or implementation

## Suggested reading, Mandatory assignments

- D&H:

- 1.4 p 11-13

- 1.5 p 13-16

- 1.6 p 16-17

- 2.1 p 22-28

- 2.2 p 28-30

- 2.3 p 30-34

- -3.1-3.5 p 43-51 = repetition (known from previous courses)

- Oblig 1: «Design Flow»

- See canvas for further instruction.

Note: Some of this content will be covered in depth in later lectures.

- Read this to familiarize yourself with content, form and language.