IN 3160, IN4160

**Verification part 2 File IO**

Yngve Hafting

### Messages

Watch videos posted by Alexander Wold before session monday (see <u>timeplan</u>). (=Flipped classroom)

Roar will run ordinary lectures this year.

In this course you will learn about the design of advanced digital systems. This includes programmable logic circuits, a hardware design language and system-on-chip design (processor, memory and logic on a chip). Lab assignments provide practical experience in how real design can be made.

#### After completion of the course you will:

- understand important principles for design and testing of digital systems

- understand the relationship between behaviour and different construction criteria

- be able to describe advanced digital systems at different levels of detail

- be able to perform simulation and synthesis of digital systems.

### **Course Goals and Learning Outcome**

https://www.uio.no/studier/emner/matnat/ifi/IN3160/index-eng.html

#### Goals for this lesson:

- To write self-testing testbenches

- What is self-testing test benches

- File IO in VHDL

- VHDL attributes used in test benches

- Assertions

- To understand set-up and hold-time

- Be able to check for violations

- To generate test-bench clocks that emulate real world clocks

#### Next lesson

Finite state machines (FSM's)

### **Outline**

- Testbench

- General layout (repetition)

- Self checking testbenches concept

- What should a good TB do

- TB output

- Assertions

- File IO

- Example synthesizable File IO

- Example- self checking test bench

- Set-up / hold time for FFs

- Fiming checks

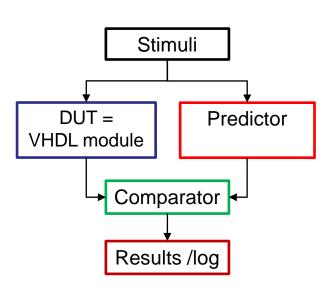

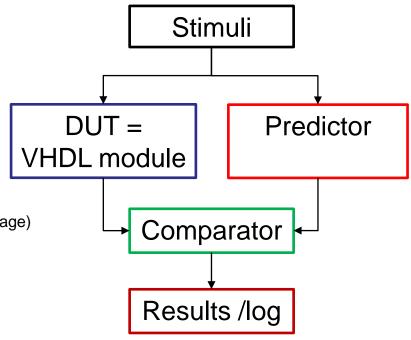

### General testbench layout (R)

#### Stimuli

- Generate or read stimuli from a file

- Use procedures rather than repeating lines

#### DUT

- Device under test (Device, Module, ...)

- Connect DUT input to stimuli to create simulation results

#### Predictor

- Predicts what the output should be

- Calculates from input or reads from file

### Comparator

Compares simulation result with predicted result and reports to screen or file.

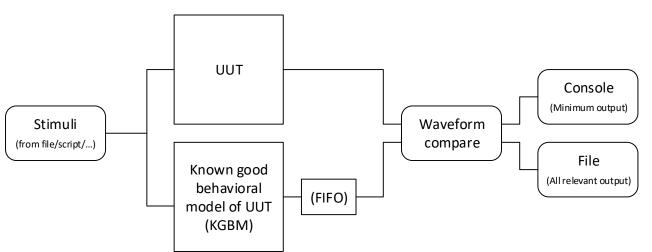

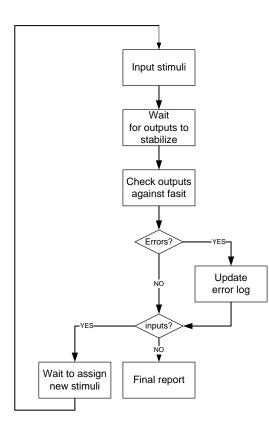

# Self checking test benches

- -performs tests and reports to screen or file (timing diagram is only used when debugging)

- Two perspectives

- As a system of modules

- As a finite state machine

- Does not reflect stimuli independent testing

### A good testbench:

- Tests should

- run independently of stimuli

- run throughout simulation

- cover all (100%) specified behaviour

- Catch all deviations from known good behavior

- Stimuli

- Should cover all types of behavior

- All design (VHDL) code should be run (100% code coverage)

- · All corner cases or

- Formal verification : All possible input

- » = not possible in most cases

- » (eg 32 bit adder =  $(2^{32})^2$  combinations)

- Normally sets DUT-inputs only

- never overwrite signals inside DUT

- => create and test submodules separately if this seems needed...

- Fault injection

- Proves that the each test will catch errors

- · Fault injection can use "Force" to overwrite signals from or in DUT

# **Test bench output**

### Report

- which test are performed

- what stimuli are applied

- successful completion of

- Stimuli series

- Tests

- Errors

- Expected vs simulation result

- Timing

- Create relevant waveforms (we do not automate this)

- Before errors or deviations occur

- Relevant input, output

- Internal states (preferably with names)

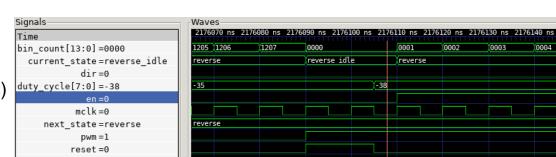

#### Example (not perfect):

```

1.00ns INFO

Starting monitoring events

cctb.pwm

1.00ns INFO

cctb.pwm

Starting duty cycle tests

15.00ns INFO

cctb.pwm

Passed: Reset test

163850.00ns INFO

cctb.pwm

Duty cycles: Set dc: 50.0%, Measured dc: 49.0%, period = 163.8us, f = 6.11kHz

327690.00ns INFO

cctb.pwm

Duty cycles: Set dc: -50.0%, Measured dc: -49.0%, period = 163.8us, f = 6.10kHz

327690.00ns INFO

cctb.pwm

Sequential duty tests complete

491530.00ns INFO

cctb.pwm

Duty cycles: Set dc: 27.3%, Measured dc: 27.0%, period = 163.8us, f = 6.10kHz

819210.00ns INFO

cctb.pwm

Duty cycles: Set dc: 50.0\%, Measured dc: 49.0\%, period = 163.8us, f = 6.10kHz

983050.00ns INFO

cctb.pwm

Duty cycles: Set dc: -84.4%, Measured dc: -84.0%, period = 163.8us, f = 6.10kHz

1310730.00ns INFO

cctb.pwm

Duty cycles: Set dc: -33.6%, Measured dc: -33.0%, period = 163.8us, f = 6.10kHz

1474570.00ns INFO

cctb.pwm

Duty cycles: Set dc: 41.4%, Measured dc: 41.0%, period = 163.8us, f = 6.10kHz

1638410.00ns INFO

cctb.pwm

Duty cycles: Set dc: -23.4%, Measured dc: -23.0%, period = 163.8us, f = 6.10kHz

1966090.00ns INFO

cctb.pwm

Duty cycles: Set dc: -27.3%, Measured dc: -27.0%, period = 163.8us, f = 6.10kHz

Duty cycles: Set dc: -27.3%, Measured dc: -27.0%, period = 163.8us, f = 6.10kHz

2129930.00ns INFO

2176090.00ns INFO

Random duty tests 1/2 complete

cctb.pwm

2176090.00ns INFO

cctb.pwm

Resetting module...

2176105.00ns INFO

Reset between duties complete

cctb.pwm

cctb.pwm

2176105.00ns INFO

Passed: Reset test

Duty cycles: Set dc: -29.7%, Measured dc: -29.0%, period = 163.8us, f = 6.10kHz

2339940.00ns INFO

2667620.00ns INFO cctb.pwm

Duty cycles: Set dc: -69.5%, Measured dc: -69.0%, period = 163.8us, f = 6.10kHz

2831460.00ns INFO cctb.pwm

Duty cycles: Set dc: 27.3%, Measured dc: 27.0%, period = 163.8us, f = 6.10kHz

2943460.00ns INFO cctb.pwm

Random duty tests 2/2 complete

2943460.00ns INFO cctb.regr

main test passed

** tb pwm.main test

** TESTS=1 PASS=1 FAIL=0 SKIP=0

```

## How to organize a medium sized testbench

- Create separate classes for

- Generic signal monitoring

- replaces use of 'attributes in VHDL

- can be much more extensive than attributes

- DUT Monitoring

- Contains all tests, their trigger and reports

- Stimuli generation

- Creates all input sequentially

- Either timed or based on response

- Uses DUT-inputs

- Fault injection

- · can be run with DUT being an empty entity.

- · Forces/overrides signals used in tests

- Separate location for classes will ensure better readability

- Allow the simulator to run as much as possible...

- Test only on appropriate triggers

- everything on every clock => slow test.

- Do not store values that can be easily calculated

### VHDL libraries for test benches/ file IO

- std.textio from IEEE contains procedures for reading from and writing to file

- (see next page for package declaration)

- Standard VHDL package declarations can be found by searching the web (if you do know their name)

### **UiO** • Department of Informatics

**University of Oslo**

```

package TEXTIO is

type LINE is access string;

type TEXT is file of string;

type SIDE is (right, left);

subtype WIDTH is natural;

```

L (line) is the access (pointer) to the «current» position in a text Note: L is **inout** since it is both read and set by the procedure

```

file input : TEXT open READ MODE is "STD INPUT";

file output : TEXT open WRITE MODE is "STD OUTPUT";

procedure READLINE (file F: TEXT; L: inout LINE);

procedure READ L:inout LINE; VALUE: out bit; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out bit);

procedure READ L:inout LINE; VALUE: out bit vector; GOOD: out BOOLEAN); procedure WRITE L:inout LINE; VALUE: in character;

procedure READ L:inout LINE; VALUE: out bit vector);

procedure READ L:inout LINE; VALUE: out BOOLEAN; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out BOOLEAN);

procedure READ L:inout LINE; VALUE: out character; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out character);

procedure READ L:inout LINE; VALUE: out integer; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out integer);

procedure READ L:inout LINE; VALUE: out real; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out real);

procedure READ L:inout LINE; VALUE: out string; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out string);

procedure READ L:inout LINE; VALUE: out time; GOOD : out BOOLEAN);

procedure READ L:inout LINE; VALUE: out time);

```

```

procedure WRITELINE (file F : TEXT; L : inout LINE);

procedure WRITE L :inout LINE; VALUE : in bit;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure WRITE L : inout LINE; VALUE : in bit vector;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure WRITE L : inout LINE; VALUE : in BOOLEAN;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure WRITE L : inout LINE; VALUE : in integer;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure WRITE L : inout LINE; VALUE : in real;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0;

DIGITS: in NATURAL := 0);

procedure WRITE L : inout LINE; VALUE : in string;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure WRITE L : inout LINE; VALUE : in time;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0;

UNIT: in TIME := ns);

20

```

end TEXTIO;

### File IO

- Synthesis

- Mostly used for reading ROM content

- Strictly not supported by VHDL-> vendor specific solutions

- Vivado synthesis (2020) can only use std\_logic or bit, no integers

- Simulation

- Stimuli (input)

- Response (logging)

- Data output

- Errors and other messages

### File IO

- Binary files

- Can output whole types (custom types, records / anything)

- Only one type per file

- Tool specific (non portable code)

- Text files

- Can contain anything

- Human readable

- A bit trickier to use (text to type conversions...)

- We will use text files

16.02.2023

22

# **Example: File IO for synthesis of ROM 1/2**

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.numeric std.all;

use STD.textio.all;

entity ROM is

generic(

data_width: natural := 8;

addr width: natural := 2;

filename: string := "ROM_data_bits.txt"

);

port(

address: in std_logic_vector(addr_width-1 downto 0);

data: out std_logic_vector(data_width-1 downto 0));

end entity;

```

- 4 byte ROM example

- 8 bit data

- 2 bit address

- Libraries

- Remember std.textio

- File name

- Assuming project (work) directory

### **Example: File IO for synthesis of ROM 1/2**

```

type memory array is array(2**addr width-1 downto 0) of

std logic vector(data width-1 downto 0);

impure function initialize ROM(file name: string)

return memory array is

file init file: text open read mode is file name;

variable current line: line;

variable result: memory array;

begin

for i in result'range loop

readline(init file, current line);

read(current line, result(i));

end loop;

return result;

end function;

--initialize rom:

constant ROM DATA: memory array := initialize ROM(filename);

begin

data <= ROM DATA(to integer(unsigned(address)));</pre>

end;

```

### Combinational implementation

- Tool specific: Vivado won't allow for integers being read from file or strings

- Integer data will have to be converted to '1' and '0' (without '').

#### Impure:

- Does not always return the same result using same input parameters (due to file usage)

- File is a text we open in read mode

- Line is "access" type which means

- A pointer to a position in the file

#### Readline

Sets the line pointer to the beginning of the (first or) next line

#### Read

- Sets the data parameter

- Sets the line pointer to the next data (or end of line)

- · Whitespace is delimiter

- What do we get if we set ROM\_DATA to a signal?

- By initializing as default value this memory can be synthesized with file usage

Yngve Hafting: 16.02.2023

### **Assertions** - «To ensure a model is working with valid inputs»\*

- Compilation

- Can be used to check for size mismatches at compile time.

- RTL Simulation

- Compare simulated and expected outcome values (behavior)

- Post Synthesis simulation

- Cheks on signal timing attributes in addition to behavior

- Severity levels

- failure means «simulation should be stopped»

- Usually when a module cant be initiated correctly, something doesn't compile...

- error when the model provides wrong output or goes into wrong state

- warning «unexpected conditions that do not affect the state of the model»

- note to report when everything went well (default for report)

### UiO • Department of Informatics

University of Oslo

# Example Self-checking test bench 1/3

```

library IEEE;

use IEEE.STD LOGIC 1164.all;

use IEEE.numeric std.all;

use STD.textio.all;

entity tb ROM is

end entity;

architecture behavioral of tb ROM is

constant

data width: natural := 8;

addr width: natural := 2;

constant

component ROM is

generic(

data width: natural := 8;

addr width: natural := 2;

filename: string := "ROM data bits.txt");

port(

address: in std logic vector(addr width-1 downto 0);

out std logic vector(data width-1 downto 0));

end component;

signal tb data : std logic vector(data width-1 downto 0);

```

signal tb address: std logic vector(addr width-1 downto 0) := "00";

```

Libraries

```

std.textio ++

- Generics for RTL simulation only

- For post synthesis simulation:

- Synthesis will already have used any generic for creating sizes, unless you are working with a behavioral model of a component.

- Default values for stimuli generated by testbench

Do not set default values for component outputs!

May hide initialization errors

```

begin

DUT: ROM

port map(

address => tb_address,

data => tb_data);

```

# Example Self-checking test bench 2/3

```

STIMULI: process is

file stimuli file: text open read mode is "ROM stimuli.txt";

variable stimuli line: line;

variable stimuli address: integer;

variable stimuli data: integer;

procedure set stimuli is

begin

readline(stimuli file, stimuli line);

read(stimuli line, stimuli address);

read(stimuli line, stimuli data);

tb address <= std logic vector(to unsigned(stimuli address, addr width));

end procedure;

file log file: text open write mode is "ROM results and log.txt";

variable log line: line;

procedure check output is

constant ADR DIGITS : integer := 2; -- size adress as base 10 number

constant DAT DIGITS : integer := 4; -- size data as base 10 number

constant SPACER: integer := 1;

begin

--report errors to console

assert (tb data = std logic vector(to signed(stimuli data, data width)))

report ("DATA MISMATCH for address: ", integer'image(stimuli address))

severity error;

-- report to file

write(log line, stimuli address, field => ADR DIGITS);

write(log_line, stimuli data, field => DAT DIGITS + SPACER);

write(log line, tb data, field => tb data'length + SPACER);

writeline(log file, log line);

end procedure;

```

```

begin

while not endfile(stimuli_file) loop

set_stimuli;

wait for 1 ns;

check_output;

end loop;

file_close(stimuli_file);

file_close(log_file);

report ("Testing finished!");

std.env.stop;

end process;

end architecture;

```

Why do we put our procedures in process, not architecture declaration?

# **Example Self-checking test bench 3/3**

### ROM\_DATA\_bits.txt

00000011 00001100 00010111 10000010

### Synthesizable

- '1' and '0' stored as text

- Only partial VHDL implementation

- · No integers or other types

- No underscores

- Different tool = different issues

### ROM\_stimuli.txt

### Simulation only

- Any type stored as text

- Full VHDL implementation

- Whitespace >1 = OK

- Good practice:

- Use human readable values

- integers or hex values > binary

### ROM\_results\_and\_log.txt

- Our output data

- We decide format

- Try to make output that

- · is readable and

- understandable

- can be used to check data

### We used std\_logic\_vector similar to bit\_vector

```

package TEXTIO is

procedure WRITELINE(file F : TEXT; L : inout LINE);

type LINE is access string;

type TEXT is file of string;

procedure WRITE(L :inout LINE; VALUE : in bit;

type SIDE is (right, left);

JUSTIFIED: in SIDE := right;

subtype WIDTH is natural;

FIELD: in WIDTH := 0);

file input : TEXT open READ MODE is "STD INPUT";

procedure WRITE(L : inout LINE; VALUE : in bit vector;

file output : TEXT open WRITE MODE is "STD OUTPUT";

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure READLINE(file F: TEXT; L: inout LINE);

procedure WRITE(L : inout LINE; VALUE : in BOOLEAN;

procedure READ(L:inout LINE; VALUE: out bit; GOOD : out BOOLEAN);

JUSTIFIED: in SIDE := right;

procedure READ(L:inout LINE; VALUE: out bit);

FIELD: in WIDTH := 0);

procedure READ(L:inout LINE; VALUE: out bit vector; GOOD: out BOOLEAN); procedure WRITE(L:inout LINE; VALUE: in character;

procedure READ(L:inout LINE; VALUE: out bit vector);

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0);

procedure READ(L:inout LINE; VALUE: out BOOLEAN; GOOD : out BOOLEAN);

procedure READ(L:inout LINE; VALUE: out BOOLEAN);

procedure WRITE(L : inout LINE; VALUE : in integer;

JUSTIFIED: in SIDE := right;

procedure READ(L:inout LINE; VALUE: out character; GOOD: out BOOLEAN);

FIELD: in WIDTH := 0);

procedure READ(L:inout LINE; VALUE: out character);

procedure WRITE(L : inout LINE; VALUE : in real;

procedure READ(L:inout LINE; VALUE: out integer; GOOD : out BOOLEAN);

JUSTIFIED: in SIDE := right;

procedure READ(L:inout LINE; VALUE: out integer);

FIELD: in WIDTH := 0;

DIGITS: in NATURAL := 0);

procedure READ(L:inout LINE; VALUE: out real; GOOD : out BOOLEAN);

procedure READ(L:inout LINE; VALUE: out real);

procedure WRITE(L : inout LINE; VALUE : in string;

JUSTIFIED: in SIDE := right;

procedure READ(L:inout LINE; VALUE: out string; GOOD : out BOOLEAN);

FIELD: in WIDTH := 0);

procedure READ(L:inout LINE; VALUE: out string);

procedure WRITE(L : inout LINE; VALUE : in time;

procedure READ(L:inout LINE; VALUE: out time; GOOD : out BOOLEAN);

JUSTIFIED: in SIDE := right;

procedure READ(L:inout LINE; VALUE: out time);

FIELD: in WIDTH := 0;

UNIT: in TIME := ns);

end TEXTIO;

```

# Post synthesis, post implementation simulation and testbenches

- Mostly relevant for ASIC design

- Post synthesis, post route

- Using the same testbench may be difficult

- Simulation information in design files will normally be stripped during synthesis.

- Assertions will be gone

- · Adaptations may be necessary to compile

- Generics may be frozen/ not generic

- Timing information will be there

- · Much more to test on...

- Signal attributes next slide

- Does not replace static timing analysis and constraints

- Timing constraints are used for synthesis...

https://docs.xilinx.com/r/en-US/ug900-vivado-logic-simulation/Post-Synthesis-Simulation

Performing a thorough timing simulation ensures that the completed design is free of defects that could otherwise be missed, such as:

- functionality changes that are caused by:

- Synthesis properties or constraints that create mismatches

- UNISIM properties applied in the Xilinx Design Constraints (XDC) file

- The interpretation of language during simulation by different simulators

- · Dual port RAM collisions

- Missing, or improperly applied timing constraints

- · Operation of asynchronous paths

- Functional issues due to optimization techniques

# Signal Attributes for simulation 1/2

These attributes are predefined for any signal X:

| Name          | Definition               |

|---------------|--------------------------|

| X'event       | True when X changes      |

|               | (boolean)                |

| X'active      | True when X assigned     |

|               | to (boolean)             |

| X'last_event  | When X last changed      |

|               | (time)                   |

| X'last_active | When X was last assigned |

|               | to (time)                |

| X'last_value  | Previous value of X      |

|               | (same type as X)         |

- These are signal only!

- Each signal maintains these throughout simulation

- Variables don't have these

- => v. faster in simulation

- 'event used in rising\_edge()

- (other use not intended for synthesis)

- 'last...

- Can be useful in testbenches

- Example (oblig 8):

```

assert en'last_event < LONG_PWM_CYCLE/2

report "PWM is not happening,.."

severity error;</pre>

```

**University of Oslo**

## Signal Attributes for simulation 2/2

These attributes create a **new signal**, based on signal X:

Name Definition

X'delayed(T) X, delayed by T

(same type as X)

X'stable(T) True if X unaltered

for time T (boolean)

X'quiet(T) True if X unassigned

for time T (boolean)

X'transaction "Toggles" when X is

assigned (bit)

- May be used to create simulation logic and tests

- (not synthesizable)

### **Attributes in cocotb?**

- Cocotb and GHDL does not (Jan. 2023) have built in support for VHDL signal attributes.

- Other simulators may have an API for this...

- Solution: create a signal monitor class

- It will run slightly slower than a pure VHDL simulation due to added context switching

- Alternative: build a new top layer in VHDL with signal attributes as outputs along with the other signals.

- Downside for this is spreading testbench code into multiple modules and languages

```

import cocotb

from cocotb import start soon

from cocotb.triggers import Edge, ReadOnly

from cocotb.utils import get sim time

# Conversion to pico-seconds using dictionary

ps conv = {'fs': 0.001, 'ps': 1, 'ns': 1000, 'us': 1e6, 'ms':1e9}

class SignalEventMonitor():

Tracks a signals last event.

def init (self, signal):

self.signal = signal

self.last event = get sim time('ps

core "attributes"

self.last rise = self.last event

self.last fall = self.last event

start soon(self.update())

async def update(self):

Monitoring service

while 1:

await Edge (self.signal)

# Avoid multiple triggers on a single event

await ReadOnly()

self.last event = get sim time('ps')

if self.signal == 1: self.last rise = self.last event

else: self.last fall = self.last event

Secondary

def stable interval(self, units='ps'):

# convert last event to the prefix in use

attribute

last event c = self.last event/ps conv[units]

calculation

# calculate stable interval

on demand

stable = get sim time(units) - last event c

return stable

#... Monitoring a signal ...

en mon = SignalEventMonitor(self.dut.en)

PERIOD NS = 10

```

assert en mon.stable interval('ns') > PERIOD NS-1, (

"not stable long enough!")

### More on VHDL attributes

- There are attributes for

- Signals

- (previous slides)

- Types

- Notable:

- 'image(v) returns a string ex: report("current value is: ", integer image(my\_int));

'value(s) returns a value (exposite of 'image)

34

- 'value(s) returns a value (opposite of 'image)

- Array types/objects (vectors)

- 'left, 'right, 'low, 'high, 'range, 'reverse\_range, 'length,

'ascending (= false when «downto»), 'element (== subtype of the vector)

- Entities

- attributes to get compiled name hierarchy- as seen in simulator when selecting signals

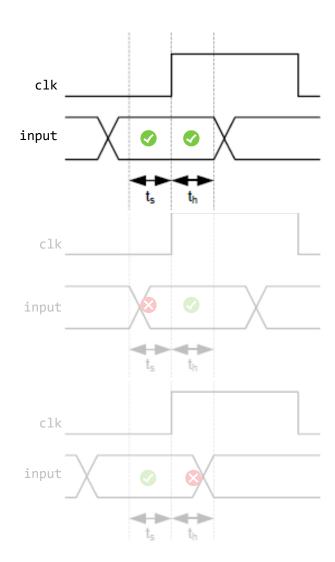

# Testcase: Set-up/hold time in flipflops

To avoid metastability (neither 0 nor 1), inputs must be stable some time before (set-up) and after (hold) clock edge

- Output (not shown) will return to 0 or 1 after being in the metastable state, but it's not given which one.

- This means; the system is no longer deterministic.

# Timing and logic check

```

27: entity D FF is

28:

29:

port (D, Clk, Set, Reset: in std logic;

30:

Q : out std logic);

31: begin

32:

assert (not(Clk = '1' and Clk'EVENT and not D'STABLE(Setup)))

33:

report "Setup time violation" severity WARNING:

34:

assert (not(Clk = '1' and D'EVENT and not Clk'STABLE(Hold)))

35:

report "Hold time violation" severity WARNING;

36:

assert (not(Set ='0' and Reset = '0'))

37:

report "Set and Reset are both asserted"

38:

severity ERROR;

39: end entity D FF;

```

- The stable attribute can be used to check set-up- and hold times

- Returns true if a signal has been stable >= time given as input parameter

- Assert in an entity =>

checking is being done for all architectures that belongs to this entity.

**CAUTION!** Care should be taken using asserts. Vivado can only support static asserts that do not create, or are created by, behavior. For example, performing as assert on a value of a constant or a operator/generic works; however, as asset on the value of a signal inside an if statement will not work.

### **Clock generator**

Asymmetric low and high time (dutycycle)

```

🗏 entity clock gen is

27

generic (Freq : REAL := 10.0; -- MHz

28

Mark: REAL:= 0.3); -- Mark length (0-1.0)

29

end entity clock gen;

30

31

🗏 architecture cg of clock gen is

32

-- Mark time in us

33

constant ClockHigh :TIME := (Mark/Freq)*us;

34

-- Space time in us

constant ClockLow :TIME := ((1.0-Mark)/Freg)*us;

35

36

signal clock : std logic := '0';

37

■ begin

38

process is

39

begin

4.0

wait for ClockLow;

41

clock <= '1';

42

wait for ClockHigh;

43

clock <= '0';

44

end process;

45

end architecture cg;

```

```

Example:

Clock with jitter

```

**UiO** • Department of Informatics

- Jitter:

- (random) variable delay

- Occurs naturally in all digital electronic

- math\_real.uniform:

```

procedure UNIFORM(

variable SEED1, SEED2 : inout POSITIVE;

variable X : out REAL);

```

- pseud-random number generator procedure

- uniform distribution

- uniform distributionalters seed values and setsrnd number

```

2: use IEEE.std logic 1164.all;

3: use IEEE.math real.all;

```

4: 5: Entity RAND CLOCK is

6: -- generic parameters

7: generic (delay : DELAY\_LENGTH := 100 ns);

8: port(clock : out std logic);

library IEEE;

9: end entity RAND\_CLOCK;

10:

11: architecture RTL\_RAND\_CLOCK of RAND\_CLOCK is

12:

13: begin 14: 15: RAND CLK:

16: process

17: variable seed1, seed2 : INTEGER := 42;

18: variable rnd : REAL;

19: begin

20: loop

21: clock <= '0';

22: uniform (seed1, seed2, rnd);

23: wait for delay + (rnd - 0.5)</pre>

29:

23: wait for delay + (rnd - 0.5) \* (10 NS); 24: clock <= '1'; 25: uniform (seed1, seed2, rnd);

26: wait for delay + (rnd - 0.5) \* (10 NS);

27: end loop;

28: end process;

30: end architecture RTL RAND CLOCK;

# Suggested reading

- D&H

- File access, ROM

- 8.8 p184-189

- Attributes

- B.8 p 638-640

- Timing constraints:

- 15.1-3 p 328 334

- 15.4-6 p 334- 340