UiO Department of Informatics

University of Oslo

IN5230

Electronic noise –

Estimates and countermeasures

# Lecture 13 (Mot 10) Amplifier Architectures

# Miller capacitance

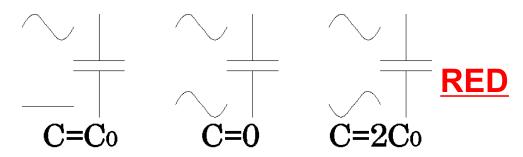

Before we look at the transistor configurations we need a fast repetition of the Miller effect.

- When a capacitor is connected between a signal line and a stable potential the signal line will experience a capacitance according to the standard formula (C=εA/t).

- If the potential on the other side are in phase a smaller capacitance will be experienced. If the signal is exactly equal the capacitance will "disappear".

- If the signal is in opposite phase the experienced capacitance will be larger. If it is in opposite phase and exactly equal the capacitance will be double.

# **Transistor configurations:**

There are mainly three alternatives for placing a FET/BJT in an architecture:

CS/CE has both voltage and current amplification resulting in the highest gain. But it has also the highest input capacitance (due to the Miller effect)

**CD/CC** has a high current gain but a voltage gain close to one. It has a low input capacitance (from the Miller effect) resulting in a high input impedance. It also has low output impedance.

**CG/CB** is used to achieve low input impedance and high output impedance.

| FET                     | BJT                        |                    |

|-------------------------|----------------------------|--------------------|

| CS:<br>Common<br>Source | CE:<br>Common<br>Emitter   |                    |

| CD:<br>Common<br>Drain  | CC:<br>Common<br>Collector |                    |

| CG:<br>Common<br>Gate   | CB:<br>Common<br>Base      | CG CB Z=low Z=high |

|                         |                            | RED <sub>3</sub>   |

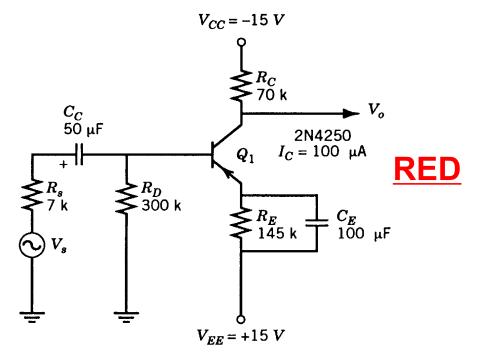

### **10-2 Common Emitter**

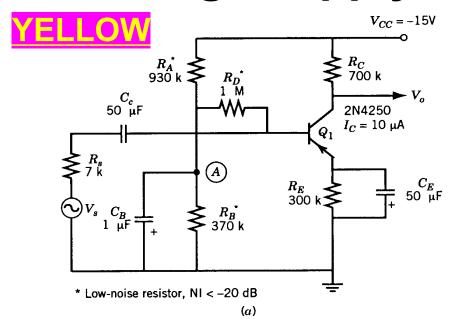

The schematic shows a transistor that is biased for low noise operation between 10Hz and 10kHz.

The noise values are as follows:

|       | 10Hz         | 10kHz        |

|-------|--------------|--------------|

| En    | 2nV          | 2nV          |

| ln    | 2pA          | 0.3pA        |

| Ro    | $1000\Omega$ | $6700\Omega$ |

| NF@Ro | 1.8dB        | 0.3dB        |

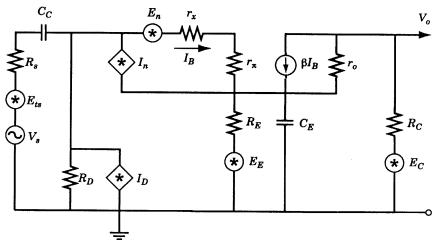

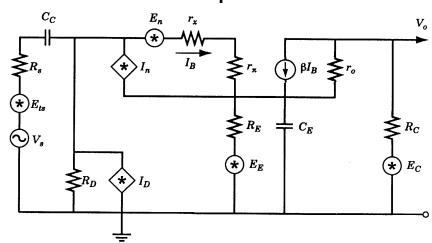

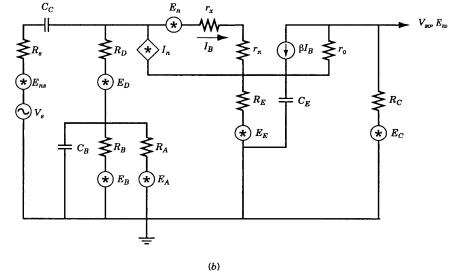

The noise schematic shows a hybrid- $\pi$  model together with passive bias elements.

Note that when VEE and Vcc are stable DC-sources, they are merged together with ground during noise analysis.

Figure 10-2 Noise and small-signal equivalent circuit for CE stage.

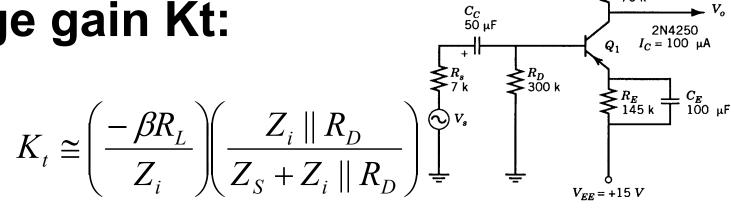

# The voltage gain Kt:

Kt is the voltage gain from Vs to Vo. The first parenthesis is the voltage gain within the transistor ( $\beta$  is IcE/IBE) while the second parenthesis is the network in front of the base.

$$Z_i = r_x + r_\pi + (\beta + 1)Z_E$$

The input resistance *Zi* includes the resistance you can see through the base towards emitter.

$$R_L \cong R_C \parallel r_0 \parallel R_{i2}$$

The load resistance consists of the collector bias resistance, the transistor internal resistance and the input resistance of the next stage:  $R_{i2}$ .

$$Z_E = R_E \parallel -jX_E$$

The emitter impedance consists of a real part and an imaginary part (a resistance and a capacitance in parallel).

$V_{CC} = -15 V$

### UiO Department of Informatics

University of Oslo

$$Z_S = R_S - jX_C$$

The source impedance is a resistance in series with a capacitor.

If we assume ignorable loss in biasing, coupling and feedback we can simplify the expression for *Kt* to:

$$K_{t} \cong -\frac{\beta R_{L}}{Z_{S} + r_{x} + r_{\pi} + \beta Z_{E}}$$

Figure 10-2 Noise and small-signal equivalent circuit for CE stage.

If  $Zs \ll r_{\pi}$  and  $ZE \ll r_{e}$  the expression is simplified to:

$$K_t \cong -\frac{R_L}{r_e} = -g_m R_L$$

If we simplify and ignore the external load we have:

$$K'_t = K_t$$

for  $R_L = R_C$

We will then have the following expression for the equivalent input noise:

$$E_{ni}^2 \cong E_{ns}^2 + E_n^2 \left(\frac{R_S + R_D}{R_D}\right)^2 + (I_n^2 + I_D^2)(R_S - jX_C)^2 + \frac{E_E^2}{1 + (\omega R_E C_E)^2} + \left(\frac{E_C}{K_{t}}\right)^2.$$

In the expression, we recognise the first part (say from section. 7.3). Last term is also known. The second last term, however, needs some comments. The noise voltage over  $R_E$  will not be  $E_E$  for higher frequencies, because  $C_E$  will "attempt to short-circuit" this. To find the expression we first model the thermal noise in  $R_E$  as a current noise of size  $I_E = E_E/R_E$ . The noise current over  $R_E$  and  $C_E$  will be:

$$E'_{E}^{2} = I_{E}^{2} \cdot \left(C_{E} \parallel R_{E}\right) = \frac{E_{E}^{2}}{R_{E}^{2}} \left| \frac{R_{E}}{j \omega R_{E} C_{E} + 1} \right|^{2} = \frac{E_{E}^{2}}{1 + \left(\omega R_{E} C_{E}\right)^{2}}$$

# Common-emitter with one voltage supply

Here a point A is established supplying a stable DC potential for the base. The point A is AC-wise short circuited to ground through  $C_B$ .

|                | 10Hz                  | 10kHz                 |  |

|----------------|-----------------------|-----------------------|--|

| En             | 4.5nV                 | 4.5nV                 |  |

| In             | 0.3pA                 | 0.1pA                 |  |

| R <sub>0</sub> | $10 \mathrm{k}\Omega$ | $45 \mathrm{k}\Omega$ |  |

| NF@Ro          | 0.68dB                | 0.35dB                |  |

| Kt             | 280                   |                       |  |

| Ri             | 780                   |                       |  |

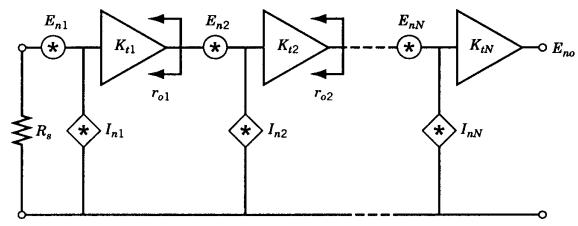

# Noise in cascaded stages

We have previously studied the noise figure for cascaded amplifiers. We will now look at the equivalent input noise:

The expression for equivalent input noise can be expressed as follows

$$E_{ni}^{2} = E_{ns}^{2} + E_{n1}^{2} + I_{n1}^{2}R_{s}^{2} + \frac{E_{n2}^{2} + I_{n2}^{2}r_{o1}^{2}}{K_{t1}^{2}} + \frac{E_{n3}^{2} + I_{n3}^{2}r_{o2}^{2}}{K_{t1}^{2}K_{t2}^{2}} + \cdots$$

Here  $r_{01}$  is the output resistance of stage 1. Similarly for  $r_{02}$ ,  $r_{03}$  etc.  $K_{ti}$  is as earlier the voltage gain.

As previously if the gain is large enough in the first stage, noise from subsequent stages can be ignored.