IN5230 Electronic noise – Estimates and countermeasures

Lecture X (Razavi 7) Noise – Razavi – Chapter 7

#### UiO **Content of Informatics**

University of Oslo

# **MOSFET Thermal Noise**(29)

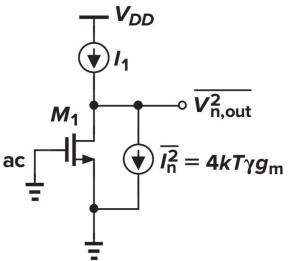

- MOS transistors exhibit thermal noise with the most significant source being the noise generated in the channel

- For long-channel MOS devices operating in saturation, the channel noise can be modelled by a <u>current source</u> connected <u>between the drain and source</u> terminals with a spectral density

$$\overline{I_n^2} = 4kT\gamma g_m$$

Red:

Equation

- The coefficient 'γ' (Not body effect coefficient!) is derived to be 2/3 for long-channel transistors and is higher for submicron MOSFETs

- As a rule of thumb, Razavi assume  $\gamma=1$

$$-I_{F} = 4kT\gamma g_{m}$$

Red:

Figure

University of Oslo

### **MOSFET Thermal: Example**

- The maximum output noise occurs if the transistor sees only its own output impedance as the load, i.e., if the external load is an ideal current source

- Output noise voltage spectrum is given by (7.29,7.30)

$$S_{out}(f) = S_{in}(f)|H(f)|^2$$

$$\overline{V_n^2} = \overline{I_n^2} r_O^2 = (4kT\gamma g_m) r_O^2$$

3

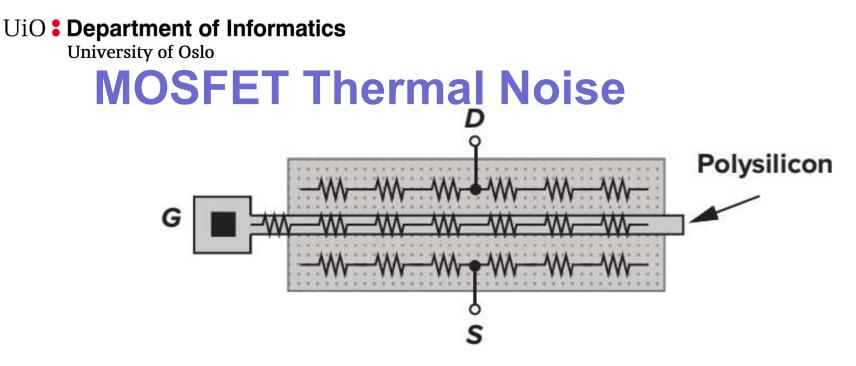

- Ohmic sections of a MOSFET have a finite resistivity and exhibit thermal noise

- For a wide transistor, source and drain resistance is negligible whereas the gate distributed resistance may become noticeable.

= contact

4

University of Oslo

### **MOSFET Thermal Noise**

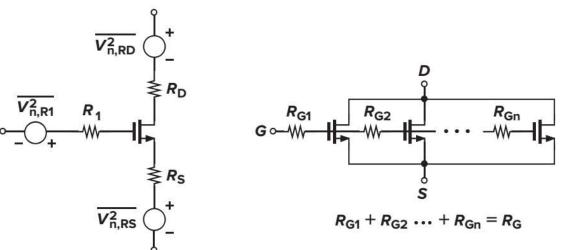

- In the noise model (left fig), the lumped resistance *R*<sup>1</sup> represents the distributed gate resistance

- In the distributed structure of the right figure, unit transistors near the left end see the noise of only a fraction of *R<sub>G</sub>* whereas those near the right end see the noise of most of *R<sub>G</sub>* Red:

- It can be proven that  $R_1 = R_G/3$  and hence the noise generated by gate resistance is  $\overline{V_{nRG}^2} = 4kTR_G/3$

# UiO Department of Informatics University of Oslo MOSFET Thermal Noise

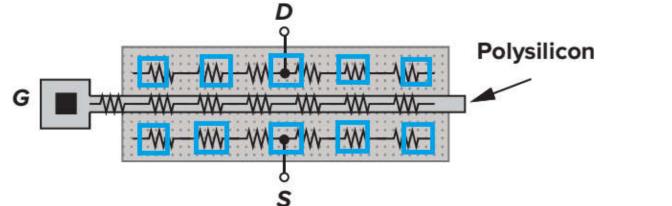

- Effect of *R<sub>G</sub>* can be reduced by proper layout

- In left fig, the two ends of the gate are shorted by a metal line, reducing the distributed resistance from *R<sub>G</sub>* to *R<sub>G</sub>*/4

- Alternatively, the transistor can be folded as in the right figure so that each gate "finger" exhibits a resistance of *R<sub>G</sub>*/4 for composite transistor

UiO **Compartment of Informatics**

University of Oslo

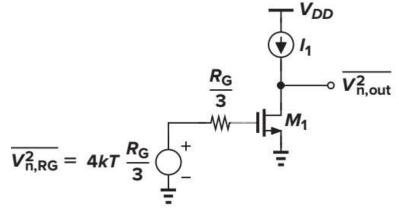

### **MOSFET Thermal Noise: Example**

• If the total distributed gate resistance is R<sub>G</sub>, the output noise voltage due to R<sub>G</sub> is given by (7.32)

$$\overline{V_{n,out}^2} = 4kT \frac{R_G}{3} (g_m r_O)^2$$

• For the gate resistance noise to be negligible, we must ensure (7.33)

$$rac{R_G}{3} \ll rac{\gamma}{g_m}$$

[Yellow: Equation]

University of Oslo

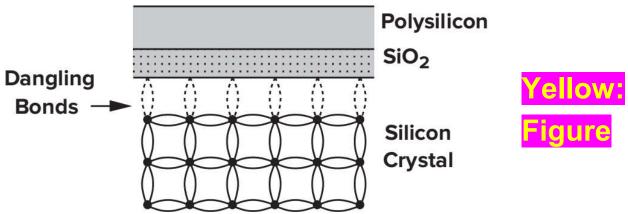

#### Flicker Noise (36)

- At the interface between the gate oxide and silicon substrate, many "dangling" bonds appear, giving rise to extra energy states

- Charge carriers moving at the interface are randomly trapped and later released by such energy states, introducing "flicker" noise in the drain current

- Other mechanisms in addition are believed to generate flicker noise

- Average power of flicker noise cannot be predicted easily

- It varies depending on cleanness of oxide-silicon interface and from one CMOS technology to another

- Flicker noise is more easily modelled as a <u>voltage source</u> in <u>series with the gate</u> and in saturation region, is roughly given by

$$\overline{V_n^2} = \frac{K}{C_{ox}WL} \cdot \frac{1}{f} \quad \begin{array}{c} \text{Red:} \\ \text{Equation} \end{array}$$

• K is a process-dependent constant on the order of 10E-25V<sup>2</sup>F

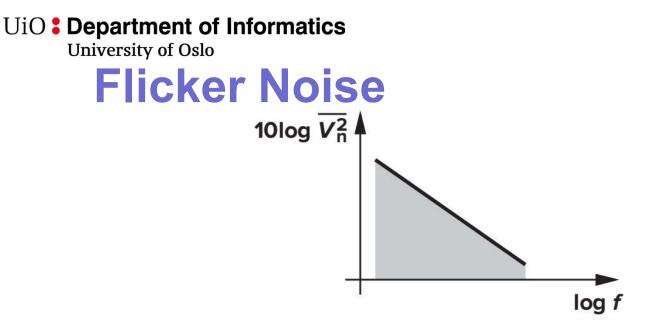

- The noise spectral density is inversely proportional to frequency

- Trap and release phenomenon occurs at low frequencies more often

- Flicker noise is also called "1/f" noise

- To reduce 1/f noise, device area must be increased

- Generally, PMOS devices exhibit less 1/f noise than NMOS transistors

- Holes are carried in a "buried" channel, at some distance from the oxide-silicon interface

University of Oslo

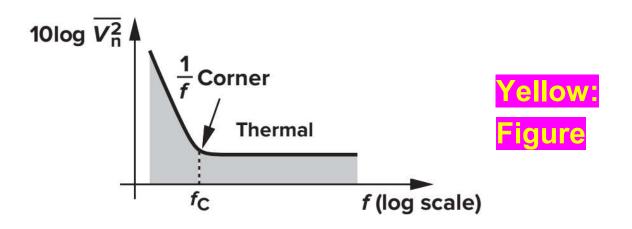

### Flicker Noise Corner Frequency

- At low frequencies, the flicker noise power approaches infinity

- At very slow rates, flicker noise becomes indistinguishable from thermal drift or aging of devices

- Noise component below the lowest frequency in the signal of interest does not corrupt it significantly

- Intersection point of thermal noise and flicker noise spectral densities is called "corner frequency" fc

University of Oslo

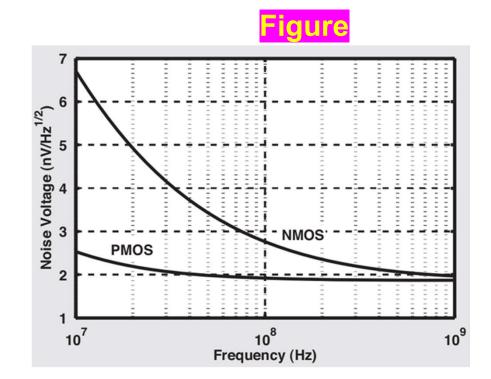

### **Nanometer Design Notes**

- W/L =  $5\mu$ m/40nm,

- ID = 250µA

- Low frequencies: Flicker noise

- High frequencies: Thermal noise

- ⇒ PMOS exhibit less noise than NMOS (and PNP less than NPN)

- ⇒NMOS noise corner at several hundred MHz

University of Oslo

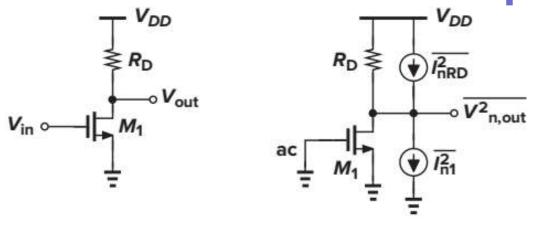

#### Input-Referred Noise: Example 3/9

- For the simple CS stage, the input-referred noise voltage is given by (7.45,7.46,7.47)  $\overline{V_{n,in}^2} = \frac{\overline{V_{n,out}^2}}{A_v^2}$  $= \left(4kT\gamma g_m + \frac{K}{C_{ox}WL} \cdot \frac{1}{f} \cdot g_m^2 + \frac{4kT}{R_D}\right) R_D^2 \frac{1}{g_m^2 R_D^2}$  $= 4kT\frac{\gamma}{g_m} + \frac{K}{C_{ox}WL} \cdot \frac{1}{f} + \frac{4kT}{g_m^2 R_D}$

- First and third terms combined can be viewed as thermal noise of an equivalent resistance Rτ, so that the equivalent input-referred thermal noise is 4kTRτ

University of Oslo

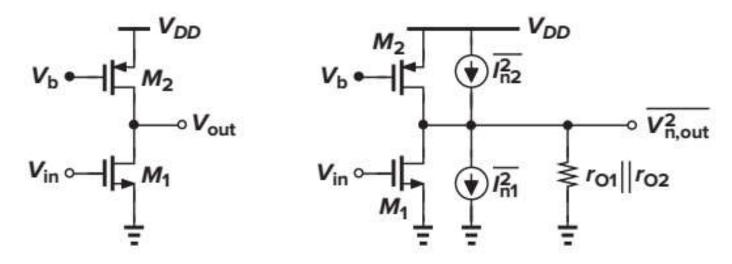

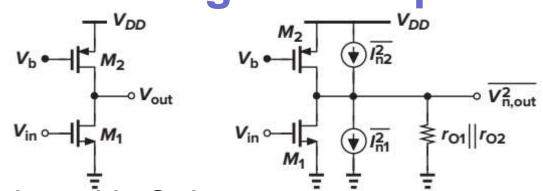

**Common-Source Stage: Example 3/4**

• Since the voltage gain is equal to  $g_{m1}(r_{O1}||r_{O2})$ , total noise voltage referred to the gate of  $M_1$  is (7.77,7.78)

$$\overline{V_{n,in}^2} = 4kT(\gamma g_{m1} + \gamma g_{m2})\frac{1}{g_{m1}^2} = 4kT\gamma \left(\frac{1}{g_{m1}} + \frac{g_{m2}}{g_{m1}^2}\right)$$

• Thus, *gm*<sup>2</sup> must be minimized because *M*<sup>2</sup> serves as a current source rather than a transconductor

University of Oslo

#### **Common-Source Stage: Example 4/4**

• Total output noise with CL is (7.79,7.80)

$$\overline{V_{n,out,tot}^2} = \int_0^\infty 4kT \gamma (g_{m1} + g_{m2})(r_{O1} || r_{O2})^2 \frac{df}{1 + (r_{O1} || r_{O2})^2 C_L^2 (2\pi f)^2}$$

$$\overline{V_{n,out,tot}^2} = \gamma (g_{m1} + g_{m2})(r_{O1} || r_{O2}) \frac{kT}{C_L}$$

• A low-frequency input sinusoid of amplitude Vm yields an output amplitude equal to  $g_{m1}(r_{O1}||r_{O2})V_m$  with an output SNR of (7.81,7.82)

Yellow:

SNR<sub>out</sub> =

$$\left[\frac{g_{m1}(r_{O1} || r_{O2}) V_m}{\sqrt{2}}\right]^2 \cdot \frac{1}{\gamma(g_{m1} + g_{m2})(r_{O1} || r_{O2})(kT/C_L)}$$

=  $\frac{C_L}{2\gamma kT} \cdot \frac{g_{m1}^2(r_{O1} || r_{O2})}{g_{m1} + g_{m2}} V_m^2$

15

UiO **Contemport of Informatics**

University of Oslo

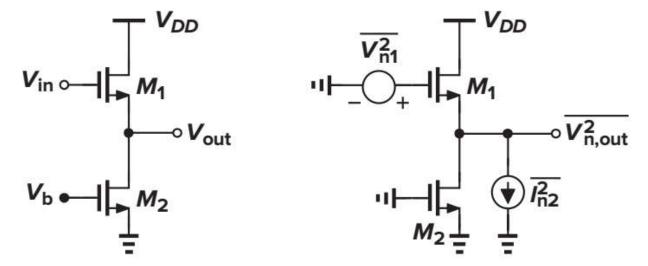

#### **Source Followers: Thermal Noise 2/2**

• The voltage gain is  $A_{v} = \frac{\frac{1}{g_{mb1}} \left\| r_{01} \right\| r_{02}}{\frac{1}{g_{mb1}} \left\| r_{01} \right\| r_{02} + \frac{1}{g_{m1}}}$

Total input-referred noise voltage is (7.110,7.111)

$$\overline{V_{n,in}^2} = \overline{V_{n1}^2} + \frac{\overline{V_{n,out}^2}|_{M2}}{A_v^2} = 4kT\gamma \left(\frac{1}{g_{m1}} + \frac{g_{m2}}{g_{m1}^2}\right) \quad \frac{\text{Yellow:}}{\text{Equation}}$$

Source followers add noise to the input signal and provide a voltage gain less than unity

UiO **Department of Informatics**

University of Oslo

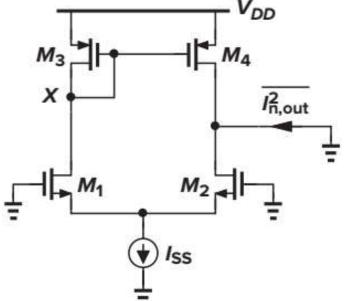

## Noise in five-transistor OTA

- The noise current of  $M_3$ primarily circulates through the diode-connected impedance  $1/g_{m3}$ , producing a voltage at the gate of  $M_4$  with spectral density  $4kT_{\gamma}/g_{m3}$

- This noise is multiplied by  $g_{m4}^2$  as it emerges from the drain of  $M_4$ ; the noise current of  $M_4$  also flows directly through the output short-circuit thus (7.141)  $\overline{I_{n,out}^2} = 4kT\gamma(2g_{m1,2} + 2g_{m3,4})$

- Multiplying this noise by  $R_{out}^2 \approx (r_{O1,2}||r_{O3,4})^2$  and dividing the result by  $A_v^2 = G_m^2 R_{out}^2$  the total input-referred noise is

$$\overline{V_{n,in}^2} = 8kT\gamma \left(\frac{1}{g_{m1,2}} + \frac{g_{m3,4}}{g_{m1,2}^2}\right) \quad \frac{\text{Yellow:}}{\text{Equation}}$$

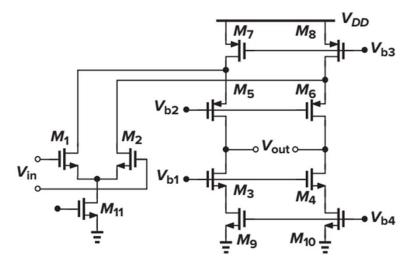

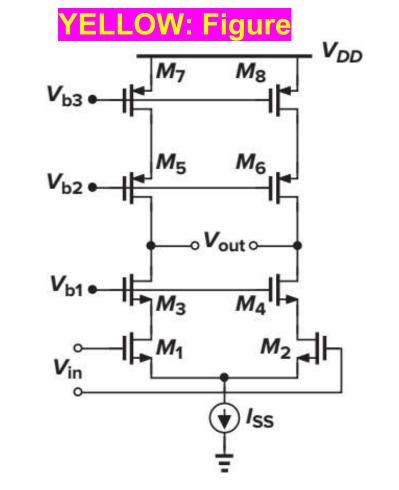

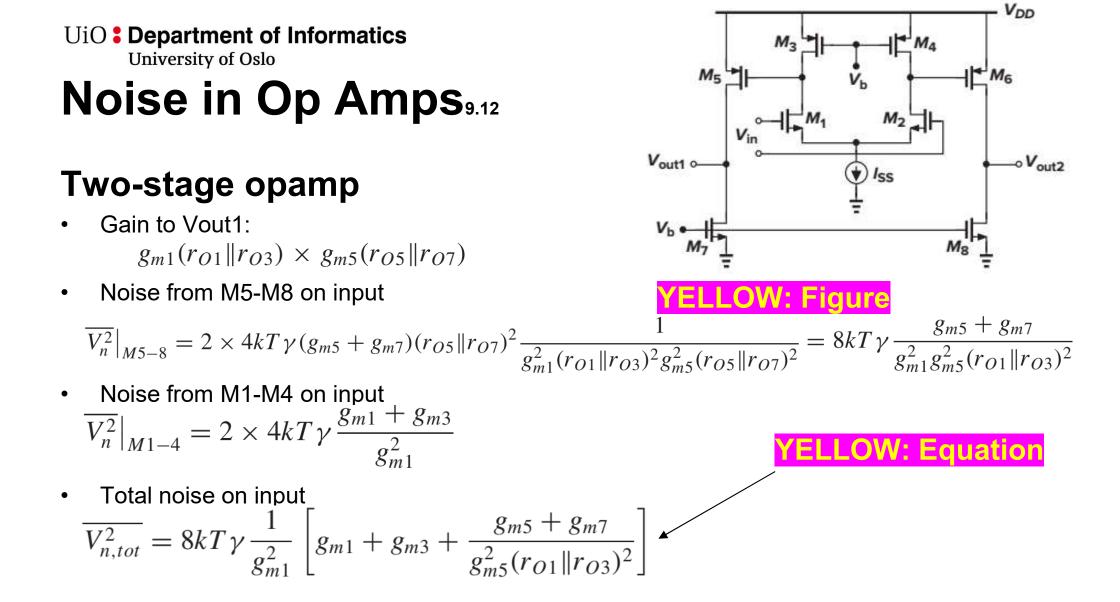

# Noise in Op Amps<sub>9.12</sub>

- How to analyse for noise in more complex amplifier structures?

- ⇒ Find which gate voltages that influence most on the output!

- $\Rightarrow$  Analyse manually or by simulation!

- Upper right: Telescopic

- Lower left: Folded cascode

- Lower right: Two-stage opamp

Noise in field effect transistors

University of Oslo

# Noise in Op Amps<sub>9.12</sub>

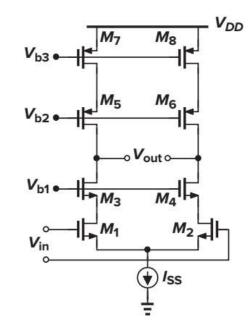

#### Telescopic

- M7-M8 give a coarse regulation of current while M5-M6 gives fine tuning i.e. M7-M8 has larger influence

- M1-M2 is the signal inputs, obviously more sensitive than M3-M4.

- $\Rightarrow$  M1-M2 and M7-M8 are the most noise sensitive.

• Resulting expression below:

$$\overline{V_n^2} = 4kT \left( 2\frac{\gamma}{g_{m1,2}} + 2\frac{\gamma g_{m7,8}}{g_{m1,2}^2} \right) + 2\frac{K_N}{(WL)_{1,2}C_{ox}f} + 2\frac{K_P}{(WL)_{7,8}C_{ox}f}\frac{g_{m7,8}^2}{g_{m1,2}^2}$$

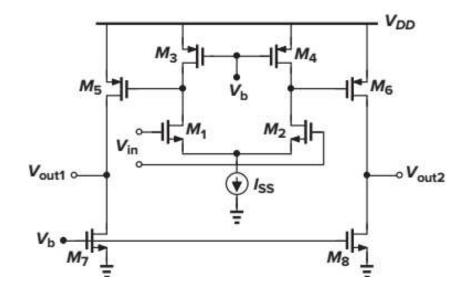

# Noise in Op Amps<sub>9.12</sub>

#### Folded-cascode

- The gate voltage of M1-M2, M7-M8, M9-M10 will give the largest influence on the output and are hence most noise sensitive. (We test by making a small step on M7 and keep the others fixed etc.)

- We calculate (thermal) noise from M7-M8 and M9-M10 to output.

$$\overline{V_{n,out}^2}\Big|_{M7,8} = 2\left(4kT\frac{\gamma}{g_{m7,8}}g_{m7,8}^2R_{out}^2\right)$$

$$\overline{V_{n,out}^2}\Big|_{M9,10} = 2\left(4kT\frac{\gamma}{g_{m9,10}}g_{m9,10}^2R_{out}^2\right)$$

• Then we add M1-M2 contribution and calculate back to the input Vin

$$\overline{V_{n,int}^2} = 8kT \left( \frac{\gamma}{g_{m1,2}} + \gamma \frac{g_{m7,8}}{g_{m1,2}^2} + \gamma \frac{g_{m9,10}}{g_{m1,2}^2} \right)$$

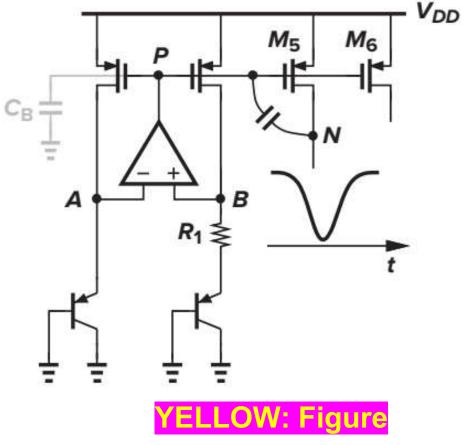

YELLOW: Figure

$$M_7$$

$M_8$   $V_{DD}$

$M_1$   $V_{b2}$   $V_{b1}$   $M_5$   $M_6$

$M_1$   $M_2$   $V_{b1}$   $M_3$   $M_4$   $V_{b4}$

$M_1$   $M_2$   $M_3$   $M_4$   $M_6$   $V_{b4}$

$M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_2$   $M_1$   $M_2$   $M_2$   $M_1$   $M_2$   $M_2$   $M_3$   $M_4$   $M_8$   $M_8$   $M_8$   $M_8$   $M_8$   $M_8$   $M_8$   $M_8$   $M_8$   $M_1$   $M_1$   $M_2$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$   $M_2$   $M_1$

IN5230

Noise in field effect transistors

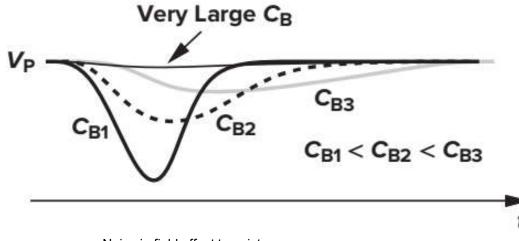

### Bandgap - Speed and Noise Issues12.6

- The bandgap reference generates a stable voltage on P independent of temperature variations. This is used to generate stable currents on M5, M6 etc.

- An unwanted voltage spike on N may be transferred to P and further on to M6 and other parts using the reference.

- In a low power implementation the amplifier will be slow and this makes it less resistant towards noise

### Bandgap - Speed and Noise Issues12.6

- Using a faster amplifier will reduce the noise but increase the power consumption

- An alternative is to add a capacitor CB in node P. A large CB reduces the noise spike but makes it last for a longer time. It also increases the time before the circuit is settled after power on. This is a disadvantage in particular when the reference is normally off and only turned on when it should be used.

## Bandgap - Speed and Noise Issues12.6

- Whether a fast amplifier or large capacitance (or a combination) should be used will depend on the application.

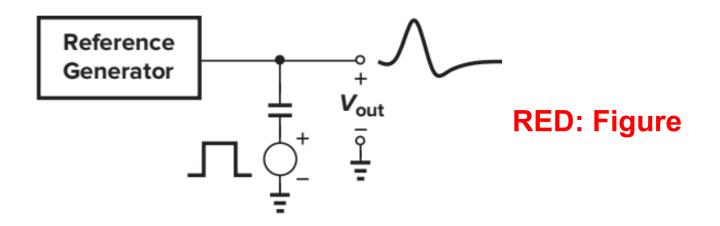

- The noise resistivity towards this type of noise can be modelled by adding a voltage pulse on a capacitor connected to the generated reference voltage.

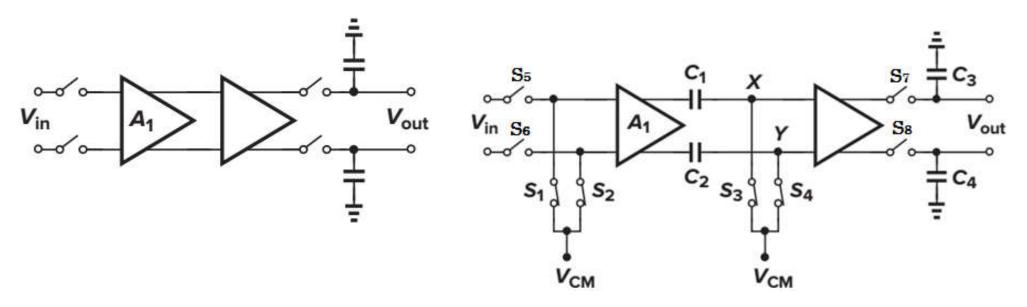

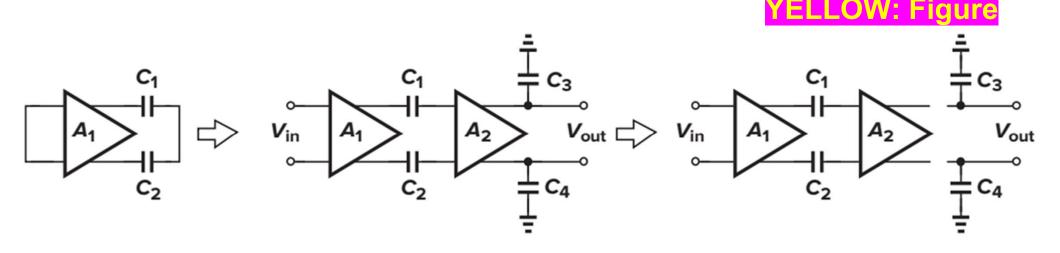

#### **Reduction of Noise by Offset Cancellation**<sub>14.2.3</sub>

- DC-offset ≈ low frequency

- Periodic cancellation?

• Problem: Noise of A1 corrupts Vin

University of Oslo

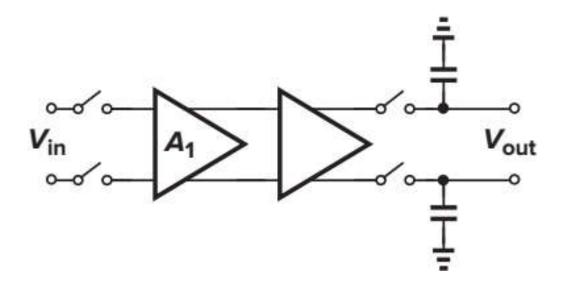

#### **Reduction of Noise by Offset Cancellation**<sub>14.2.3</sub>

- Offset cancellation before every sampling

- CDS: Correlated Double Sampling

- (Leads to aliasing of wideband noise)

#### **Reduction of Noise by Offset Cancellation**<sub>14.2.3</sub>

- S1-S4 closed, S5-S8 open: Offset of A1 stored on C1 and C2

- 2. S1-S4 open, S5-S8 closed: Input sets C3 and C4

- 3. (S1-S6 closed, S5-S6 open), S7-S8 open: C3 and C4 keeps sampled value

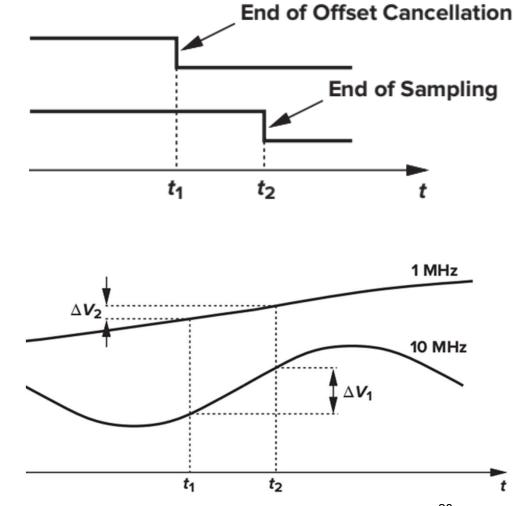

## **Reduction of Noise by Offset Cancellation**<sub>14.2.3</sub>

- $\Delta t = t_2 t_1 = 10 \text{ ns}$

- Offset/noise under 1/∆t is supressed

- Sinus maximum slew rate: 2πfA, maximum voltage change: ΔV= 2πfAΔt.

- 1MHz: ∆V1/A=6.3%

- 10MHz: ∆V1/A=63%

- Low frequency has not time to change