## INF2270, exercise in combinational logic two's complement arithmetic: example solution

## P. Häfliger

February 10, 2010

## Task 1

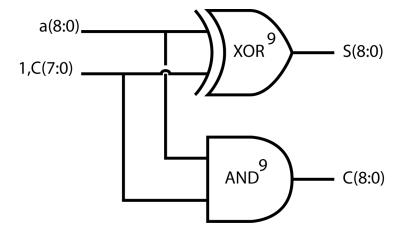

Figure 1 shows a cascade of half adders that increment a 9-bit signed integer by 1. ISE notation is used for the busses and the XOR and AND gate represent 9 gates in parallel. The first half adder receives a constant 1 as carry in bit and thus, 1 is added to the the input a(8:0) and the result S is equal to a+1.

## Task 2

```

11011

27 - 32

-5

1110111

119-128

-9

-43

1010101

85 - 128

100000001

257-512

-255

=

1111111111

511-512

-1

```

What is the corresponding 8 bit two's complement number for:

```

-31

_

-31+256=225

11100001

\hat{=}

-32

-32+256=224

11100000

-127

-127 + 256 = 129

10000001

=

-128

-128 + 256 = 128

10000000

ê

-77

-77+256=179

10110011

22

22

00001010

```

Figure 1: A circuit that increments a 9-bit integer by  $1\,$