## INF2270 — Spring 2010

HF1

Philipp Häfliger

#### Feture 4: Signed Binaries and Arithmetic

UNIVERSITETET I OSLO

Karnaugh maps revisited

**Binary Addition**

Signed Binary Numbers

**Binary Subtraction**

Arithmetic Right-Shift and Bit Number Extension

Lecture 4: Signed Binaries and Arithmetic

NIVERSITETET OSLO

Karnaugh maps revisited

**Binary Addition**

Signed Binary Numbers

**Binary Subtraction**

Arithmetic Right-Shift and Bit Number Extension

Lecture 4: Signed Binaries and Arithmetic

NIVERSITETET OSLO

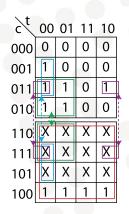

#### Karnaugh maps with 5 or 6 variables

With 3 variables along one edge a Karnaugh map needs to be folded into 3-dimensions and one has to look for cubes instead of rectangels.

X's can arbitrarily be assigned a '0' or a '1' and can thus be used to extend cubes.

$= (c_2)$   $\vee (t_1 \land c_1)$   $\vee (t_0 \land t_1 \land c_0)$   $\vee (t_0 \land c_0 \land c_1)$

#### Lecture 4: Signed Binaries and Arithmetic

h

Karnaugh maps revisited

**Binary Addition**

Signed Binary Numbers

**Binary Subtraction**

Arithmetic Right-Shift and Bit Number Extension

Lecture 4: Signed Binaries and Arithmetic

OSLO

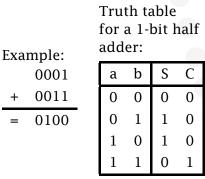

## Half Adder

S is the result and C is the carry bit, i.e. a bit indicating if there is an overflow and an additional bit is necessary to represent the result.

Lecture 4: Signed Binaries and Arithmetic

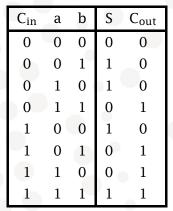

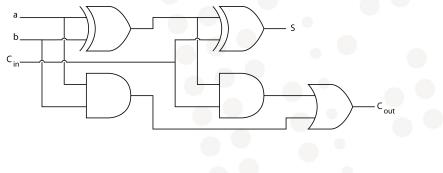

## Full Adder (1/2)

A half adder cannot be cascaded to a binary addition of an arbitrary bit-length since there is no carry input. An extension of the circuit is needed.

#### Full Adder truth table:

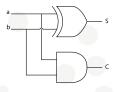

## Full Adder (2/2)

#### Schematics:

Lecture 4: Signed Binaries and Arithmetic

Karnaugh maps revisited

**Binary Addition**

Signed Binary Numbers

**Binary Subtraction**

Arithmetic Right-Shift and Bit Number Extension

Lecture 4: Signed Binaries and Arithmetic

NIVERSITETET OSLO

#### Sign and Magnitude representation

Maybe the most obvious way of representing positive and negative binary numbers is to add a sign-bit. Example for 8 bit numbers (7-bit magnitude and 1 sign-bit, -127 to +127):

87 = 01010111-87 = 11010111

A problem here is that there is also a 'signed zero', i.e. +0 and -0, which does not really make sense.

Lecture 4: Signed Binaries and Arithmetic

NIVERSITETET OSLO

#### **Two's complement Representation**

The two's complement (used in most digital circuits today) is a signed binary number representation that does not have this problem and comes with a number of other convenient properties. In 8-bit two's complement the unsigned numbers 0 to 127 represent themselves, whereas the unsigned numbers 128 to 255 represent the numbers -128 to -1 (=the unsigned number -256). Thus, also in this representation all numbers with the first bit equal to '1' are negative numbers.

87 = 01010111

-41 = 11010111 (= 215-256)

-87 = 10101001 (= 169-256)

Lecture 4: Signed Binaries and Arithmetic

## **Inverting in Two's Complement**

Finding the inverse of a number in two's complement is simple. The same operation is performed for both, positive to negative and negative to positive:

- 1. invert each bit

- 2. add 1

Example:

- 87=01010111 10101000 1

- 2. 10101000+1

- 1. -87 = 10101001

- 01010110+12.

- 10101001 = -87

- 01010110

- 01010111 = 87

Karnaugh maps revisited

Binary Addition

Signed Binary Numbers

**Binary Subtraction**

Arithmetic Right-Shift and Bit Number Extension

Lecture 4: Signed Binaries and Arithmetic

NIVERSITETET OSLO

## **Binary Subtraction**

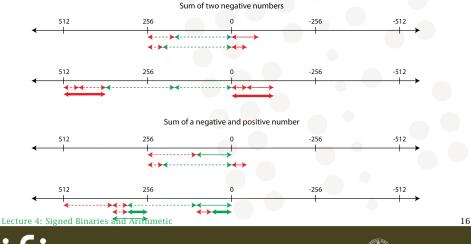

A really cool property of the two's complement representation is that one can simply add two positive or two negative or a negative and a positive number with a full-adder of the same length, ignore an eventual overflowing carry, and the result *will be correct* (provided the result is not bigger than the positive maximum (e.g. 127 with 8 bit numbers) and no smaller than the negative minimum(e.g. -128 with 8 bit numbers)). Note that 'ignoring an overflowing carry' in effect is a modulo operation of the result. For example adding two unsigned 8 bit numbers and ignoring an eventual overflow carry (which would mean that the unsigned result is bigger than 255) is performing a modulo 256 operation on the result. Signed Binaries and Arithmetic

## ifi

## Two's Complement Addition/Subtraction 8-bit Examples

| signed op | equiv. un-<br>signed op | mod 256 | signed res |

|-----------|-------------------------|---------|------------|

| -41-87    | 215+169 =<br>384        | 128     | -128       |

| 87-41     | 87+215 =<br>302         | 46      | 46         |

## **Two's Complement Addition/Subtraction** 8-bit Graphically

## **Two's Complement Subtraction**

Thus, if negative and positive numbers can simply be added, a subtraction can be performed by inverting the number that is to be subtracted and adding them. Thus, to compute a-b:

- 1. invert b by inverting every single bit

- 2. add the two numbers and set the carry in signal for the adder to 1 (in order to complete the inversion of b)

## **Arithmetic Right-Shift**

An *arithmetic right-shift* is a shift operation that performs a division by two correctly in the two's complement representation. Obviously a so called *logic shift* that shifts in a '0' from the left would turn a negative number into a positive one, which cannot be correct. Instead, the bit that is shifted in from the left needs to be the former most significant bit (MSB). Note that the result is rounded towards  $-\infty$  and not towards zero.

#### Examples:

| decimal | binary   | shifted  | decimal |

|---------|----------|----------|---------|

| -3      | 1101     | 1110     | -2      |

| -88     | 10101000 | 11010100 | -44     |

Lecture 4: Signed Binaries and Arithmetic

# Extending the bit-length in two's complement

A last note that will come in handy for the mandatory exercise: To extend the number of bits with which to represent a signed integer, the additional bits on the left need to be filled in with the formar MSB.

Examples:

| decimal | 4 bit |               | 8 bit    |

|---------|-------|---------------|----------|

| -2      | 1110  | $\rightarrow$ | 11111110 |

| -5      | 1011  | $\rightarrow$ | 11111011 |

| 5       | 0101  | $\rightarrow$ | 00000101 |