## **INF2270 – Spring 2011**

JF1

Lecture 2: Boolean Functions, Combinational Logic

NIVERSITETET OSLO

### content

Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits Concepts Encoder/Decoder Multiplexer/Demultiplexer

NIVERSITETET OSLO

### content

### Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits Concepts Encoder/Decoder Multiplexer/Demultiplexer

NIVERSITETET OSLO

## Simplification Example 2 (Lecture 1) Revisited

### $F = a \land b \land c \lor \bar{a} \land b \land c \lor \bar{a} \land b \land \bar{c} \land (a \lor c)$

|     |     |   | 1 |

|-----|-----|---|---|

| a   | b   | С | F |

| 0   | 0   | 0 | 0 |

| 0   | 0   | 1 | 0 |

| 0   | 1   | 0 | 0 |

| 0   | 1   | 1 | 1 |

| 1   | 0   | 0 | 0 |

| 1   | 0   | 1 | 0 |

| 1   | 1   | 0 | 0 |

| 1 ( | ) 1 | 1 | 1 |

UNIVERSITETET I OSLO

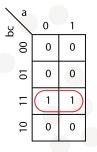

### Transscribing a Truth Table into a K-Map

| a | b | С | F |  |

|---|---|---|---|--|

| 0 | 0 | 0 | 0 |  |

| 0 | 0 | 1 | 0 |  |

| 0 | 1 | 0 | 0 |  |

| 0 | 1 | 1 | 1 |  |

| 1 | 0 | 0 | 0 |  |

| 1 | 0 | 1 | 0 |  |

| 1 | 1 | 0 | 0 |  |

| 1 | 1 | 1 | 1 |  |

The input variables are listed on the xand y-axis as Gray-code: only one bit shift between two subsequent positions.

## Identify the 'minterms'

Identify rectangles filled with 1's and containing  $2^n$  1's (i.e. 1,2,4,8 ... elements). Find a set of a minimal number of such rectangles that covers all 1's. Overlap of the rectangles is allowed, actually desired to maximize their size. Note that the K-map wraps around at its boundaries, i.e rectangles can be formed across the map edges.

# ifi

### The minterms define a 'sum' of 'products'

#### (b ∧ c)

Each rectangle defines a 'product' (elements and-ed) where the elements are the input variables that remain *constant* within the rectangle. Finally, all 'products' are or-ed. (Note: there is only one 'product' in this first example. See next example!)

# ifi

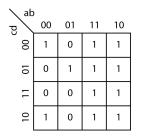

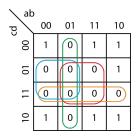

## K-map simplification: Example 2

(a)  $\vee$  ( $\bar{b} \wedge \bar{d}$ )  $\vee$  ( $b \wedge \bar{c} \wedge d$ )

UNIVERSITETET I OSLO

### K-Maps Based on the '0's

One can also use the 0 to form the minterms and derive an expression for the inverse function  $\overline{F}$  instead of F by exact same procedure. Then one can use the deMorgan theorem to turn the sum of product into a product of sums to derive F.

### K-Maps Based on the '0's: Example

$\overline{F} = (b \land d) \lor (\overline{a} \land d) \lor (\overline{a} \land b) \lor (c \land d)$ Employing deMorgan's theorem:

$$\overline{\overline{F}} = F = (\overline{\overline{b}} \vee \overline{\overline{d}}) \land (\overline{a} \vee \overline{\overline{d}}) \land (\overline{a} \vee \overline{\overline{b}}) \land (\overline{\overline{c}} \vee \overline{\overline{d}})$$

### **Properties of K-maps**

- Karnaugh maps are useful to a size of up to 6 Boolean variables

- It is only possible to have up to two variables along one axis. Karnaugh maps with 5-8 variables become, thus, 3-dimensional. (Example in the weekly exercise for lecture 3)

### content

Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits Concepts Encoder/Decoder Multiplexer/Demultiplexer

NIVERSITETET OSLO

### content

### Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits Concepts Encoder/Decoder

Multiplexer/Demultiplexer

## **Combinational Logic**

Combinational logic circuits are feed-forward logic/digital circuits with no memory that can be described by Boolean functions.

Note what is implied here: logic gates can *also* be connected in ways that include feed-back connections that implement/include *memory* that *cannot* be described as Boolean functions! This is then not 'combinational logic', but 'sequential logic', of which we will talk later.

## **Design and Analysis of Digital Circuits**

Design of a digital circuit is the process of assembling circuit blocks to form a bigger digital circuit.

Analysis of a digital circuit is the process of finding out what it is doing, e.g. (in the case of combinational logic!) by finding an equivalent Boolean function or a complete truth table.

A complete analysis of a digital circuit is quite trivial for small digital circuits but neigh impossible for circuits of the complexity of a modern CPU. Hierarchical approaches in design and analysis provide some help.

The first Pentium on the market had a mistake in its floating point unit.

After the Intel 286 there was the 386 and then the 486, but the 585.764529 was then dubbed 'Pentium' for simplicity sake.

## **Logic Gate Signals**

A certain range of input voltage is defined as 'high' or logic '1' and another range is defined as 'low' or '0'. Note: the range is defined bigger at a logic gate *input* E.g. in a digital circuit with a 1.8V supply one can, for instance, guarantee an input voltage of 0V to 0.5V to be recognised as '0' and 1.2V to 1.8V as '1' by a logic gate. On the output side the gate can guarantee to deliver a voltage of either >1.75V or <0.05V.

The assymetric ranges correct 'errors' in a cascade of gates, adding a safety margin between input and output, makeing (correctly designed!) digital circuits very robust (which is necessary with millions of logic gates in a CPU, where a single error might impair the global function!)

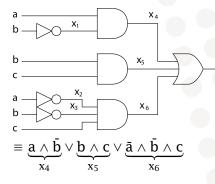

## **Analysis Example**

F

UNIVERSITETET I OSLO

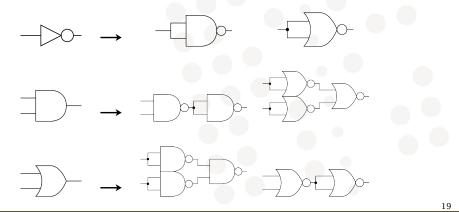

# Design Example (Universality of NAND and NOR)

Design equivalent circuits with only NANDs (NORs)

ifi

UNIVERSITETET OSLO

## **Standard Combinational Logic**

Some combinational logic (and of course also sequential logic  $\rightarrow$  later) is often used in computational devices and are usually provided as 'black boxes' guaranteeing a defined function.

Examples:

- encoder/decoder

- multiplexer/demultiplexer

- adders/multipliers

There are actually variations on how those functions are implemented, resulting in different processing speeds and/or power consumption and/or scalability (i.e. how easy it is to adapt the same function for more inputs).

### content

### Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits

#### Concepts Encoder/Decoder Multiplexer/Demultiplexer

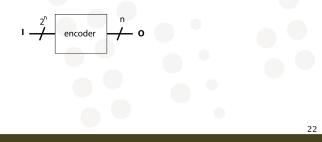

## **3-bit Encoder Specification**

An encoder in digital electronics refers to a circuit that converts  $2^n$  inputs (one-hot code) into n outputs (binary number), as specified by the following truth table.

## Simple 3-bit Encoder Truth Table

| <i>I</i> <sub>7</sub> | $I_6$ | $I_5$ | $I_4$ | I <sub>3</sub> | I <sub>2</sub> | $I_1$ | $I_0$ | <i>O</i> <sub>2</sub> | 01 | <i>O</i> <sub>0</sub> |

|-----------------------|-------|-------|-------|----------------|----------------|-------|-------|-----------------------|----|-----------------------|

| 0                     | 0     | 0     | 0     | 0              | 0              | 0     | 1     | 0                     | 0  | 0                     |

| 0                     | 0     | 0     | 0     | 0              | 0              | 1     | 0     | 0                     | 0  | 1                     |

| 0                     | 0     | 0     | 0     | 0              | 1              | 0     | 0     | 0                     | 1  | 0                     |

| 0                     | 0     | 0     | 0     | 1              | 0              | 0     | 0     | 0                     | 1  | 1                     |

| 0                     | 0     | 0     | 1     | 0              | 0              | 0     | 0     | 1                     | 0  | 0                     |

| 0                     | 0     | 1     | 0     | 0              | 0              | 0     | 0     | 1                     | 0  | 1                     |

| 0                     | 1     | 0     | 0     | 0              | 0              | 0     | 0     | 1                     | 1  | 0                     |

| 1                     | 0     | 0     | 0     | 0              | 0              | 0     | 0     | 1                     | 1  | 1                     |

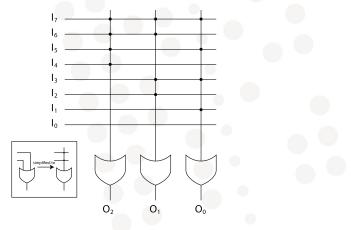

## **3-bit Encoder Implementation Variant**

## **3-bit Encoder Remarks**

The truth table that was given is not complete: some inputs are 'illegal' (not one-hot codes). Circuitry that produces the input should ensure to only produce legal states. In our specific digital circuit implementation we can deduct what the output in each illegal case would be, but other implementation may provide different outputs in those non-defined cases, and still be valid encoders! The following truth table is a deterministic specification of an encoder, without 'illegal' inputs, where the 'highest' active input bit determines the output. 'X' in the table means 'do not care', or 'for any state' and allows to abbreviate the truth table. This would require a different implementation, but we will not present it here.

## **3-bit Priority Encoder Truth Table**

| <i>I</i> <sub>7</sub> | $I_6$ | $I_5$ | $I_4$ | I <sub>3</sub> | I <sub>2</sub> | $I_1$ | $I_0$ | <i>O</i> <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|-----------------------|-------|-------|-------|----------------|----------------|-------|-------|-----------------------|-------|-----------------------|

| 0                     | 0     | 0     | 0     | 0              | 0              | 0     | 1     | 0                     | 0     | 0                     |

| 0                     | 0     | 0     | 0     | 0              | 0              | 1     | Х     | 0                     | 0     | 1                     |

| 0                     | 0     | 0     | 0     | 0              | 1              | Х     | Х     | 0                     | 1     | 0                     |

| 0                     | 0     | 0     | 0     | 1              | Х              | Х     | X     | 0                     | 1     | 1                     |

| 0                     | 0     | 0     | 1     | Х              | X              | Х     | Х     | 1                     | 0     | 0                     |

| 0                     | 0     | 1     | Х     | Х              | Х              | Х     | X     | 1                     | 0     | 1                     |

| 0                     | 1     | Х     | Х     | Х              | Х              | Х     | X     | 1                     | 1     | 0                     |

| 1                     | Х     | Х     | Х     | Х              | Х              | Х     | Х     | 1                     | 1     | 1                     |

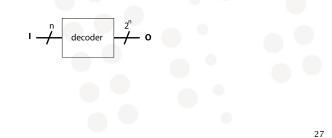

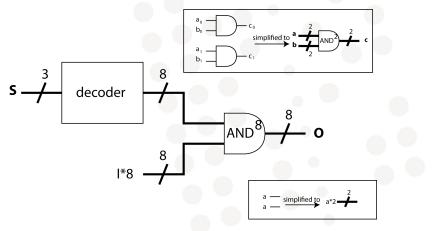

## **3-bit Decoder Specification**

A decoder is the inverse function of a encoder, in digital circuits usually decoding n (binary number) inputs into  $2^n$  outputs (one-hot code).

**ERSITETET**

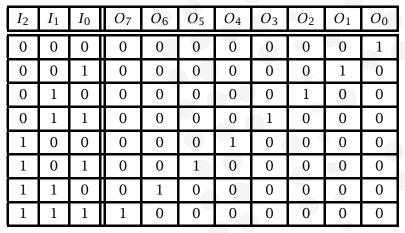

### **3-bit Decoder Truth Table**

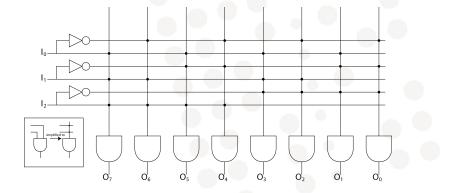

## **3-bit Decoder Implementation Variant**

ifi

UNIVERSITETET I OSLO

### content

### Simplifying Boolean Functions with Karnaugh Maps

### Combinational Logic Circuits

Concepts Encoder/Decoder Multiplexer/Demultiplexer

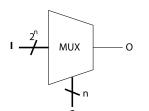

## **3-bit Multiplexer Specification**

A multiplexer routes one of  $2^n$  input signals as defined by the binary control number **S** to the single output.

| the single supput |       |       |       |  |  |  |  |  |

|-------------------|-------|-------|-------|--|--|--|--|--|

| $S_2$             | $S_1$ | $S_0$ | 0     |  |  |  |  |  |

| 0                 | 0     | 0     | $I_0$ |  |  |  |  |  |

| 0                 | 0     | 1     | $I_1$ |  |  |  |  |  |

| 0                 | 1     | 0     | $I_2$ |  |  |  |  |  |

| 0                 | 1     | 1     | $I_3$ |  |  |  |  |  |

| 1                 | 0     | 0     | $I_4$ |  |  |  |  |  |

| 1                 | 0     | 1     | $I_5$ |  |  |  |  |  |

| 1                 | 1     | 0     | $I_6$ |  |  |  |  |  |

| 1                 | 1     | 1     | $I_7$ |  |  |  |  |  |

# ifi

## **3-bit Multiplexer Implementation Variant**

ifi

UNIVERSITETET I OSLO

## **Bus Multiplexer**

A *bus*-multiplexer combines several multiplexers in parallel, i.e. routing an entire bus of digital signals.

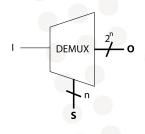

## **3-bit Demultiplexer Specification**

A demultiplexer performs the inverse function of a multiplexer, routing one input signal to one of  $2^n$  outputs as defined by the binary control number **S**

## **3-bit Demultiplexer Truth Table**

ifi

| <i>S</i> <sub>2</sub> | $S_1$ | <i>S</i> <sub>0</sub> | 07 | 06 | <i>O</i> <sub>5</sub> | $O_4$ | <i>O</i> <sub>3</sub> | <i>O</i> <sub>2</sub> | $O_1$ | <i>O</i> <sub>0</sub> |

|-----------------------|-------|-----------------------|----|----|-----------------------|-------|-----------------------|-----------------------|-------|-----------------------|

| 0                     | 0     | 0                     | 0  | 0  | 0                     | 0     | 0                     | 0                     | 0     | I                     |

| 0                     | 0     | 1                     | 0  | 0  | 0                     | 0     | 0                     | 0                     | Ι     | 0                     |

| 0                     | 1     | 0                     | 0  | 0  | 0                     | 0     | 0                     | Ι                     | 0     | 0                     |

| 0                     | 1     | 1                     | 0  | 0  | 0                     | 0     | Ι                     | 0                     | 0     | 0                     |

| 1                     | 0     | 0                     | 0  | 0  | 0                     | Ι     | 0                     | 0                     | 0     | 0                     |

| 1                     | 0     | 1                     | 0  | 0  | Ι                     | 0     | 0                     | 0                     | 0     | 0                     |

| 1                     | 1     | 0                     | 0  | Ι  | 0                     | 0     | 0                     | 0                     | 0     | 0                     |

| 1                     | 1     | 1                     | Ι  | 0  | 0                     | 0     | 0                     | 0                     | 0     | 0                     |

35

UNIVERSITETET I OSLO

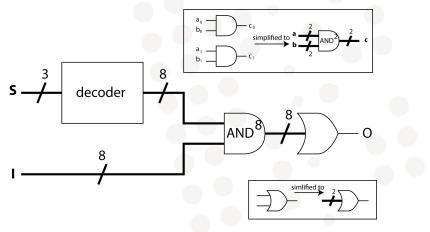

## **3-bit Demultiplexer Implementation Variant**

UNIVERSITETET I OSLO