## Intro

# INF4140 - Models of concurrency Intro, lecture 1

Høsten 2014

29. 08. 2014

# Today's agenda

#### Introduction

- overview

- motivation

- simple examples and considerations

#### Start

- a bit about

- concurrent programming with critical sections and waiting.

Read<sup>a</sup> also [Andrews, 2000, chapter 1] for some background

- interference

- the await-language

<sup>&</sup>lt;sup>a</sup>you!, as course particpant

#### What this course is about

- Fundamental issues related to cooperating parallel processes

- How to think about developing parallel processes

- Various language mechanisms, design patterns, and paradigms

- Deeper understanding of parallel processes:

- (informal and somewhat formal) analysis

- properties

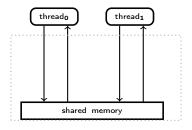

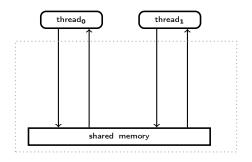

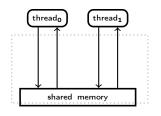

## Parallel processes

- Sequential program: one control flow thread

- Parallel program: several control flow threads

Parallel processes need to exchange information. We will study two different ways to organize communication between processes:

- Reading from and writing to shared variables (part I of the course)

- Communication with messages between processes (part II of the course)

## Course overview – part I: Shared variables

- atomic operations

- interference

- deadlock, livelock, liveness, fairness

- parallel programs with locks, critical sections and (active) waiting

- semaphores and passive waiting

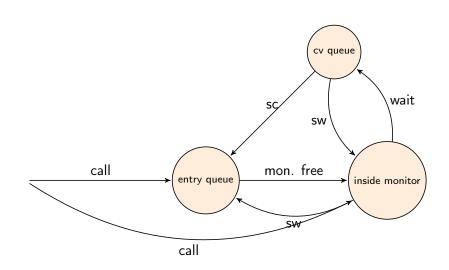

- monitors

- formal analysis (Hoare logic), invariants

- Java: threads and synchronization

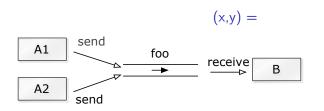

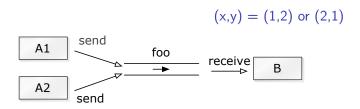

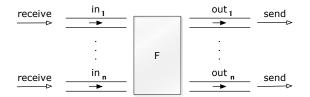

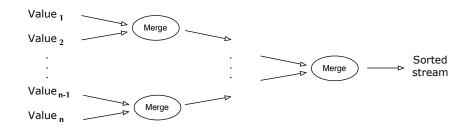

## Course overview – part II: Communication

- asynchronous and synchronous message passing

- basic mechanisms: RPC (remote procedure call), rendezvous, client/server setting, channels

- Java's mechanisms

- analysis using histories

- asynchronous systems

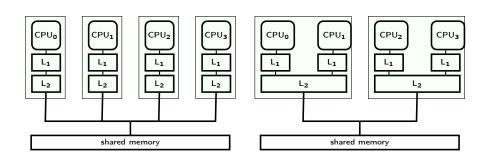

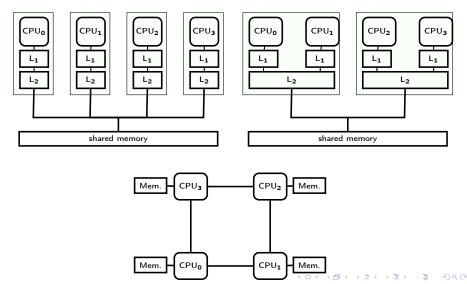

#### Part I: shared variables

#### Why shared (global) variables?

- reflected in the HW in conventional architectures

- there may be several CPUs inside one machine (or multi-core nowadays).

- natural interaction for tightly coupled systems

- used in many important languages, e.g., Java's multithreading model.

- even on a single processor: use many processes, in order to get a natural partitioning

- potentially greater efficiency and/or better latency if several things happen/appear to happen "at the same time".

e.g.: several active windows at the same time

$<sup>^{1}</sup>$ Holds for concurrency in general, not just shared vars, of course.  $\leftarrow \ge$

## Simple example

Global variables: x, y, and z. Consider the following program:

$$x := x + z; y := y + z;$$

### Pre/post-condition

- executing a program (resp. a program fragment) ⇒ state-change

- the conditions describe the state of the global variables before and after a program statement

- These conditions are meant to give an understanding of the program, and are not part of the executed code.

## Can we use parallelism here (without changing the results)?

If operations can be performed *independently* of one another, then concurrency may increase performance

## Simple example

Global variables: x, y, and z. Consider the following program:

```

before \{ x \text{ is a and } y \text{ is } b \} x := x + z; y := y + z;

```

### Pre/post-condition

- executing a program (resp. a program fragment) ⇒ state-change

- the conditions describe the state of the global variables before and after a program statement

- These conditions are meant to give an understanding of the program, and are not part of the executed code.

## Can we use parallelism here (without changing the results)?

If operations can be performed *independently* of one another, then concurrency may increase performance

## Simple example

Global variables: x, y, and z. Consider the following program:

```

before \{ \ x \ \text{is a and } y \ \text{is } b \ \} \quad x := x+z; y := y+z; \quad \{ \ x \ \text{is } a+z \ \text{and } y \ \text{is } b+z \ \}

```

#### Pre/post-condition

- executing a program (resp. a program fragment) ⇒ state-change

- the conditions describe the state of the global variables before and after a program statement

- These conditions are meant to give an understanding of the program, and are not part of the executed code.

## Can we use parallelism here (without changing the results)?

If operations can be performed *independently* of one another, then concurrency may increase performance

## Parallel operator |

Extend the language with a construction for parallel composition:

co

$$S_1 \parallel S_2 \parallel \ldots \parallel S_n$$

oc

Execution of a parallel composition happens via the concurrent execution of the component processes  $S_1, \ldots, S_n$  and terminates normally if all component processes terminate normally.

Example

$$\{ x \text{ is } a, y \text{ is } b \} x := x + z ; y := y + z \{ x = a + z, y = b + z \}$$

## Parallel operator |

Extend the language with a construction for parallel composition:

co

$$S_1 \parallel S_2 \parallel \ldots \parallel S_n$$

oc

Execution of a parallel composition happens via the concurrent execution of the component processes  $S_1, \ldots, S_n$  and terminates normally if all component processes terminate normally.

Example

$$\{ x \text{ is } a, y \text{ is } b \} \text{ } \mathbf{co} x := x + z \parallel y := y + z \text{ } \mathbf{oc} \{ x = a + z, y = b + z \}$$

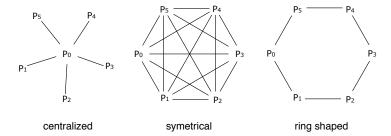

## Interaction between processes

Processes can interact with each other in two different ways:

- cooperation to obtain a result

- competition for common resources

The organization of this interaction is what we will call *synchronization*.

### Synchronization

Synchronization (veeeery abstractly) = restricting the possible interleavings of parallel processes (so as to avoid "bad" things to happen and to achieve "positive" things)

- increasing "atomicity" and mutual exclusion (Mutex): We introduce critical sections of which cannot be executed concurrently

- Condition synchronization: A process must wait for a specific condition to be satisfied before execution can continue.

## Concurrent processes: Atomic operations

### Definition (Atomic)

An operation is atomic if it cannot be subdivided into smaller components.

#### Note

- A statement with at most one atomic operation, in addition to operations on local variables, can be considered atomic!

- We can do as if atomic operations do not happen concurrently!

- What is atomic depends on the language/setting: fine-grained and coarse-grained atomicity.

- e.g.: Reading and writing of a global variable is usually atomic.<sup>2</sup>

- For some (high-level) languages: assignments x := e atomic operations, for others, not (reading of the variables in the expression e, computation of the value e, followed by writing to x.)

## Atomic operations on global variables

- fundamental for (shared var) concurrency

- also: process communication may be represented by variables: a communication channel corresponds to a variable of type vector.

- associated to global variables: a set of atomic operations

- typically: read + write,

- in HW, e.g. LOAD/STORE

- channels as gobal data: send and receive

- x-operations: atomic operations on a variable x

#### Mutual exclusion

Atomic operations on a variable cannot happen simultaneously.

## Example

$$P_1$$

$P_2$  {  $x = 0$  }  $\cos x := x + 1 \parallel x := x - 1 \text{ oc}$  { ? }

final state? (i.e., post-condition)

- Assume:

- each process is executed on its own processor

- and/or: the processes run on a multi-tasking OS

and that x is part of a shared state space, i.e. a shared var

- Arithmetic operations in the two processes can be executed simultaneously, but read and write operations on x must be performed sequentially/atomically.

- order of these operations: dependent on relative processor speed and/or scheduling

- outcome of such programs: difficult to predict!

- "race" on x or race condition

- as for races in practice: it's simple, avoid them at (almost) all costs

## Atomic read and write operations

$$\{ x = 0 \} \quad \cos x := x + 1 \parallel x := x - 1 \text{ oc } \{ ? \}$$

Listing 1: Atomic steps for x := x + 1

```

read x;

inc;

write x;

```

#### 4 atomic x-operations:

- $P_1$  reads (R1) value of x

- $P_1$  writes (W1) a value into x,

- $P_2$  reads (R2) value of x, and

- $P_2$  writes (W2) a value into x.

# Interleaving & possible execution sequences

- "program order":3

- R1 must happen before W1 and

- R2 before W2

- inc and dec ("-1") work process-local<sup>4</sup>

- ⇒ remember (e.g.) inc; write x behaves "as if" atomic (alternatively read x; inc)

operations can be sequenced in 6 ways ("interleaving")

| R1 | R1 | R1 | R2 | R2 | R2 |

|----|----|----|----|----|----|

| W1 | R2 | R2 | R1 | R1 | W2 |

| R2 | W1 | W2 | W1 | W2 | R1 |

| W2 | W2 | W1 | W2 | W1 | W1 |

| 0  | -1 | 1  | -1 | 1  | 0  |

<sup>&</sup>lt;sup>3</sup>A word aside: as natural as this seems: in a number of modern architecture/modern languages & their compilers, this is not guaranteed! Cf. Java's memory model, or weak memory models in general.

<sup>&</sup>lt;sup>4</sup>e.g.: in an arithmetic register, or a local variable (not mentioned in the code).

### Non-determinism

- final states of the program (in x):  $\{0, 1, -1\}$

- Non-determinism: result can vary depending on factors *outside* the program code

- timing of the execution

- scheduler

- as (post)-condition:  $x = -1 \lor x = 0 \lor x = 1$

$<sup>^5</sup>$ Of course, things like  $x \in \{-1,0,1\}$  or  $-1 \le x \le 1$  are equally adequate formulations of the postcondition.

#### Non-determinism

- final states of the program (in x):  $\{0, 1, -1\}$

- Non-determinism: result can vary depending on factors *outside* the program code

- timing of the execution

- scheduler

- as (post)-condition:  $x = -1 \lor x = 0 \lor x = 1$

$$\{ \ \} \ x := 0; co x := x + 1 \parallel x := x - 1 oc; \ \{ x = -1 \lor x = 0 \lor x = 1 \ \}$$

$<sup>^5</sup>$ Of course, things like  $x \in \{-1,0,1\}$  or  $-1 \le x \le 1$  are equally adequate formulations of the postcondition.

## State-space explosion

- Assume 3 processes, each with the same number of atomic operations

- consider executions of  $P_1 \parallel P_2 \parallel P_3$

| nr. of atomic op's | nr. of executions |

|--------------------|-------------------|

| 2                  | 90                |

| 3                  | 1680              |

| 4                  | 34 650            |

| 5                  | 756 756           |

- different executions can lead to different final states.

- even for simple systems: impossible to consider every possible execution

For n processes with m atomic statements each:

number of exec's =

$$\frac{(n * m)!}{m!^n}$$

## The "at-most-once" property

### Fine grained atomicity

only the very most basic operations (R/W) are atomic "by nature"

- however: some non-atomic interactions appear to be atomic.

- note: expressions do only read-access (≠ statements)

- critical reference (in an e): a variable changed by another process

- e without critical reference  $\Rightarrow$  evaluation of e as if atomic

## Definition (At-most-once property)

x := e satisfies the "amo"-property if

- 1. e contains no crit. reference

- 2. e with at most one crit. reference & x not referenced<sup>a</sup> by other proc's

<sup>&</sup>lt;sup>a</sup>or just read

## The "at-most-once" property

### Fine grained atomicity

only the very most basic operations (R/W) are atomic "by nature"

- however: some non-atomic interactions appear to be atomic.

- note: expressions do only read-access (≠ statements)

- critical reference (in an e): a variable changed by another process

- e without critical reference  $\Rightarrow$  evaluation of e as if atomic

## Definition (At-most-once property)

x := e satisfies the "amo"-property if

- 1. e contains no crit. reference

- 2. e with at most one crit. reference & x not referenced by other proc's

<sup>&</sup>lt;sup>a</sup>or just read.

### At most once examples

- In all examples: initially x = y = 0. And r, r' etc: local var's (registers)

- ullet co and oc around ...  $\| \dots$  omitted

```

\begin{array}{l} x := x + 1 \parallel y := x + 1 \\ x := y + 1 \parallel y := x + 1 \qquad \{ \ (x,y) \in \{(1,1),(1,2),(2,1)\} \ \} \\ x := y + 1 \parallel x := y + 3 \parallel y := 1 \qquad \{ y = 1 \land x = 1,2,3,4\} \\ r := y + 1 \parallel r' := y - 1 \parallel y := 5 \\ r := x - x \parallel \dots \qquad \{ \text{is r now 0?} \} \\ x := x \parallel \dots \qquad \{ \text{same as skip?} \} \\ \text{if } y > 0 \text{ then } y := y - 1 \text{ fi} \parallel \text{if } y > 0 \text{ then } y := y - 1 \text{ fi} \\ \end{array}

```

# The course's first programming language: the await-language

- the usual sequential, imperative constructions such as assignment, if-, for- and while-statements

- cobegin-construction for parallel activity

- processes

- critical sections

- await-statements for (active) waiting and conditional critical sections

#### Syntax

We use the following syntax for non-parallel control-flow<sup>6</sup>

```

Declarations

Assignments

int i = 3:

x := e:

int a[1:n];

a[i] := e;

int a[n]:7

a[n]++:

int a[1:n] = ([n] 1):

sum +:= i;

Seq. composition

statement: statement

Compound statement

{statements}

Conditional

if statement

While-loop

while (condition) statement

for [i = 0 \text{ to } n-1] statement

For-loop

```

<sup>&</sup>lt;sup>6</sup>The book uses more C/Java kind of conventions, like = for assignment and == for logical equality.

<sup>&</sup>lt;sup>7</sup>corresponds to: int a[0:n-1]

### Parallel statements

$$co S_1 \parallel S_2 \parallel \ldots \parallel S_n oc$$

- The statement(s) of each arm  $S_i$  are executed in parallel with thos of the other arms.

- Termination: when all "arms"  $S_i$  have terminated ("join" synchronization)

## Parallel processes

```

process foo {

int sum := 0;

for [i=1 to 10]

sum +:= 1;

x := sum;

}

```

- Processes evaluated in arbitrary order.

- Processes are declared (as methods/functions)

- side remark: the convention "declaration = start process" is not used in practice.<sup>8</sup>

<sup>&</sup>lt;sup>8</sup>one typically separates declaration/definition from "activation" (with good reasons). Note: even *instantiation* of a runnable interface in Java starts a process. Initialization (filling in initial data into a process) is tricky business.

```

process bar1 dir0o

for [i = 1 to n]

write(i); }

```

```

process bar2[i=1 to n] dir0o

write(i);

}

```

Starts one process.

The numbers are printed in increasing order.

Starts *n* processes.

The numbers are printed in arbitrary order because the execution order of the process is *non-deterministic*.

#### Read- and write-variables

- V : statement → variable set: set of global variables in a statement (also for expressions)

- W: statement  $\rightarrow$  variable set set of global write-variables

$$\mathcal{V}(x := e) = \mathcal{V}(e) \cup \{x\}$$

$\mathcal{V}(S_1; S_2) = \mathcal{V}(S_1) \cup \mathcal{V}(S_2)$

$\mathcal{V}(\text{if } b \text{ then } S) = \mathcal{V}(b) \cup \mathcal{V}(S)$

$\mathcal{V}(\text{while } (b)S) = \mathcal{V}(b) \cup \mathcal{V}(S)$

${\cal W}$  analogously, except the most important difference:

$$\mathcal{W}(x := e) = \{x\}$$

note: expressions side-effect free

## Disjoint processes

Parallel processes without common (=shared) global variables: without interference

$$\mathcal{V}(S_1)\cap\mathcal{V}(S_2)=\emptyset$$

- read-only variables: no interference.

- The following *interference criterion* is thus sufficient:

$$\mathcal{V}(S_1) \cap \mathcal{W}(S_2) = \mathcal{W}(S_1) \cap \mathcal{V}(S_2) = \emptyset$$

- cf. notion of race (or race condition)

- remember also: critical references/amo-property

- programming practice: final variables in Java

## Semantic concepts

- A *state* in a parallel program consists of the values of the global variables at a given moment in the execution.

- Each process executes independently of the others by *modifying* global variables using atomic operations.

- An execution of a parallel program can be modelled using a history, i.e. a sequence of operations on global variables, or as a sequence of states.

- For non-trivial parallel programs: very many possible histories.

- synchronization: conceptually used to *limit* the possible histories/interleavings.

## **Properties**

- property = predicate over programs, resp. their histories

- A (true) *property* of a program<sup>9</sup> is a predicate which is true for all possible histories of the program.

- Two types:

- safety property: program will not reach an undesirable state

- liveness property: program will reach a desirable state.

- partial correctness: If the program terminates, it is in a desired final state (safety property).

- termination: all histories are finite. 10

- total correctness: The program terminates and is partially correct.

<sup>&</sup>lt;sup>9</sup>the program "has" that property, the program satisfies the property . . .

<sup>&</sup>lt;sup>10</sup>that's also called *strong* termination. Remember: non-determinism.

## Properties: Invariants

- invariant (adj): constant, unchanging

- cf. also "loop invariant"

### Definition (Invariant)

an invariant = state property, which holds for holds for all reachable states.

- safety property

- appropriate for also non-terminating systems (does not talk about a final state)

- global invariant talks about the state of many processes at once, preferably the entire system

- local invariant talks about the state of one process

#### proof principle: induction

one can show that an invariant is correct by

- 1. showing that it holds initially,

- 2. and that each atomic statement maintains it.

## How to check properties of programs?

- Testing or debugging increases confidence in a program, but gives no guarantee of correctness.

- Operational reasoning considers all histories of a program.

- Formal analysis: Method for reasoning about the properties of a program without considering the histories one by one.

### Dijkstra's dictum:

A test can only show errors, but "never" prove correctness!

### Critical sections

Mutual exclusion: combines sequences of operations in a *critical* section which then behave like atomic operations.

- When the non-interference requirement parallel processes does not hold, we use synchronization to restrict the possible histories.

- Synchronization gives coarse-grained atomic operations.

- The notation  $\langle S \rangle$  means that S is performed atomically.<sup>11</sup>

### Atomic operations:

- Internal states are *not visible* to other processes.

- Variables cannot be changed underway by other processes.

- S: like executed in a transaction

Example The example from before can now be written as:

int

$$x := 0$$

; co  $\langle x := x + 1 \rangle \| \langle x := x - 1 \rangle$  oc $\{ x = 0 \}$

$<sup>^{11} {\</sup>rm In}$  programming languages, one could find it as  ${\tt atomic} \{ \! \! \mathcal{S} \}$  or similar.

### Conditional critical sections

#### Await statement

$$\langle await(b) S \rangle$$

- boolean condition b: await condition

- body S: executed atomically (conditionally on b)

### Example

$$\langle await(y > 0) \ y := y - 1 \rangle$$

• synchronization: decrement delayed until (if ever) y > 0 holds

### 2 special cases

unconditional critical section or "mutex"

$$\langle x := 1; y := y + 1 \rangle$$

Condition synchronization:<sup>13</sup>

$$\langle await(counter > 0) \rangle$$

<sup>&</sup>lt;sup>12</sup>Later, a special kind of semaphore (a binary one) is also called a "mutex". Terminology is a bit flexible sometimes.

<sup>&</sup>lt;sup>13</sup>one may also see sometimes just await(b): however, eval. of b better be atomic and under no circumstances must b have side-effects (never, ever. Seriously).

# Typical pattern

```

int counter = 1;

await (counter > 0)

counter := counter -1; > // start CS

critical statements;

counter := counter+1 // end CS

```

- "critical statements" *not* enclosed in \( \text{angle brackets} \). Why?

- invariant:  $0 \le counter \le 1$  (= counter acts as "binary lock")

- very bad style would be: touch counter inside "critical statements" or elsewhere (e.g. access it not following the "await-inc-CR-dec" pattern)

- in practice: beware(!) of exceptions in the critical statements

# Example: (rather silly version of) producer/consumer synchronization

- strong coupling

- buf as shared variable ("one element buffer")

- synchronization

- coordinating the "speed" of the two procs (rather strictly here)

- to avoid, reading data which is not yet produced

- (related:) avoid w/r conflict on shared memory

```

int buf, p := 0; c := 0;

2

3

process Producer {

process Consumer {

int a[N];...

int b[N];...

5

while (p < N) {

while (c < N) {

6

< await (p = c); >

< await (p > c); >

7

buf := a[p];

b[c] := buf;

8

p := p+1;

c := c+1:

10

11

```

# Example (continued)

| a ·        |  | l | l . |

|------------|--|---|-----|

| <b>a</b> . |  | l | l . |

|            |  | l | l . |

|            |  |   |     |

| ouf: | p: | c: | n: | _ |

|------|----|----|----|---|

|------|----|----|----|---|

- An invariant holds in all states in all histories (traces/executions) of the program (starting in its initial state(s)).

- Global invariant:  $c \le p \le c+1$

- Local invariant (Producer):  $0 \le p \le n$

# Locks & barriers

# INF4140 - Models of concurrency

Locks & barriers, lecture 2

Høsten 2014

5. 9. 2014

### Practical Stuff

### Mandatory assignment 1 ("oblig")

- Deadline: Friday September 26 at 18.00

- Possible to work in pairs

- Online delivery (Devilry): https://devilry.ifi.uio.no

### Introduction

- Central to the course are general mechanisms and issues related to parallel programs

- Previous class: await language and a simple version of the producer/consumer example

### Today

- Entry- and exit protocols to *critical sections*

- Protect reading and writing to shared variables

- Barriers

- Iterative algorithms:

Processes must *synchronize* between each iteration

- Coordination using flags

### Introduction

- Central to the course are general mechanisms and issues related to parallel programs

- Previous class: await language and a simple version of the producer/consumer example

### Today

- Entry- and exit protocols to critical sections

- Protect reading and writing to shared variables

- Barriers

- Iterative algorithms:

Processes must *synchronize* between each iteration

- Coordination using flags

```

int buf, p := 0; c := 0;

process Producer {

int a[N];...

while (p < N) {

< await (p = c); >

buf := a[p];

p := p+1;

}

}

int b[N];...

while (c < N) {

< await (p > c); >

b[c] := buf;

c := c+1;

}

}

```

#### Invariants

2

3

5

6 7

8

10 11

- global invariant:

- local (in the producer):

```

int buf, p := 0; c := 0;

2

3

process Producer {

process Consumer {

int a[N];...

5

int b[N];...

while (p < N) {

while (c < N) {

7

< await (p = c); >

< await (p > c); >

buf := a[p];

b[c] := buf;

8

p := p+1;

c := c+1;

10

11

```

#### Invariants

- global invariant:

- local (in the producer):

```

\begin{array}{|c|c|c|c|c|} & \textbf{int} & \textbf{buf}, & \textbf{p} := 0; & \textbf{c} := 0; \\ & \textbf{process} & \textbf{Producer} & \textbf{process} & \textbf{Consumer} & \textbf{f} \\ & \textbf{int} & \textbf{a}[N]; \dots & \textbf{int} & \textbf{b}[N]; \dots \\ & \textbf{while} & (\textbf{p} < \textbf{N}) & \textbf{f} & \textbf{while} & (\textbf{c} < \textbf{N}) & \textbf{f} \\ & < \textbf{await} & (\textbf{p} = \textbf{c}) & ; & > & \textbf{b}[\textbf{c}] & := \textbf{buf}; \\ & \textbf{p} := \textbf{p} + 1; & \textbf{c} := \textbf{c} + 1; \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} \\ & \textbf{f} & \textbf{f} & \textbf{f} & \textbf{f} \\

```

#### Invariants

2

5

7

8

10 11

- global invariant:

- local (in the producer):

#### Invariants

2

5

7

8

10 11

- global invariant:  $c \le p \le c + 1$

- local (in the producer):

```

int buf, p := 0; c := 0;

2

3

process Producer {

process Consumer {

int a[N];...

5

int b[N];...

while (p < N) {

while (c < N) {

7

< await (p = c); >

< await (p > c); >

buf := a[p];

b[c] := buf;

8

c := c+1:

p := p+1;

10

11

```

#### Invariants

- global invariant:  $c \le p \le c + 1$

- local (in the producer):  $0 \le p \le N$

### Critical section

- Fundamental for concurrency

- Immensely intensively researched, many solutions

- Critical section: part of a program that is/needs to be "protected" against interference by other processes

- Execution under mutual exclusion

- Related to "atomicity"

Main question we are discussing today:

How can we implement critical sections / conditional critical sections?

- Various solutions and properties/guarantees

- Using locks and low-level operations

- SW-only solutions? HW or OS support?

- Active waiting (later semaphores and passive waiting)

### Critical section

- Fundamental for concurrency

- Immensely intensively researched, many solutions

- Critical section: part of a program that is/needs to be "protected" against interference by other processes

- Execution under mutual exclusion

- Related to "atomicity"

### Main question we are discussing today:

How can we implement critical sections / conditional critical sections?

- Various solutions and properties/guarantees

- Using locks and low-level operations

- SW-only solutions? HW or OS support?

- Active waiting (later semaphores and passive waiting)

### Critical section

- Fundamental for concurrency

- Immensely intensively researched, many solutions

- Critical section: part of a program that is/needs to be "protected" against interference by other processes

- Execution under mutual exclusion

- Related to "atomicity"

### Main question we are discussing today:

How can we implement critical sections / conditional critical sections?

- Various solutions and properties/guarantees

- Using locks and low-level operations

- SW-only solutions? HW or OS support?

- Active waiting (later semaphores and passive waiting)

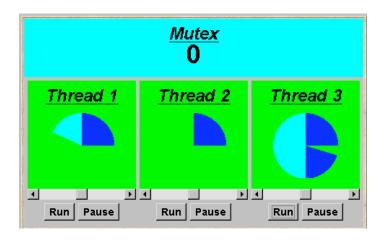

# Access to Critical Section (CS)

- Several processes compete for access to a shared resource

- Only one process can have access at a time: "mutual exclusion" (mutex)

- Possible examples:

- Execution of bank transactions

- Access to a printer

- A solution to the CS problem can be used to implement await-statements

# Access to Critical Section (CS)

- Several processes compete for access to a shared resource

- Only one process can have access at a time: "mutual exclusion" (mutex)

- Possible examples:

- Execution of bank transactions

- Access to a printer

- A solution to the CS problem can be used to implement await-statements

# Access to Critical Section (CS)

- Several processes compete for access to a shared resource

- Only one process can have access at a time: "mutual exclusion" (mutex)

- Possible examples:

- Execution of bank transactions

- Access to a printer

- A solution to the CS problem can be used to implement await-statements

# Critical section: First approach to a solution

Operations on shared variables happen inside the CS. Access to the CS must then be protected to prevent interference.

```

process p[i=1 to n] {

while (true) {

CSentry # entry protocol to CS

CS

CSexit # exit protocol from CS

non-CS

}

}

```

### General pattern for CS

- Assumption: A process which enters the CS will eventually leave it.

- ⇒ Programming advice: be aware of exceptions inside CS!

### Critical section: First approach to a solution

Operations on shared variables happen inside the CS. Access to the CS must then be protected to prevent interference.

### General pattern for CS

- Assumption: A process which enters the CS will eventually leave it.

- ⇒ Programming advice: be aware of exceptions inside CS!

### Critical section: First approach to a solution

Operations on shared variables happen inside the CS. Access to the CS must then be protected to prevent interference.

### General pattern for CS

- Assumption: A process which enters the CS will eventually leave it.

- ⇒ Programming advice: be aware of exceptions inside CS!

### Naive solution

```

int in = 1

# possible values in {1,2}

1

2

3

process p1 {

4

5

process p2 {

while (true) {

while (true) {

6

while (in=2) \{skip\};

while (in=1) {skip};

7

CS:

CS:

8

in := 2;

in := 1

non-CS

non-CS

10

```

- entry protocol: active/busy waiting

- exit protocol: atomic assignment

```

int in = 1

# possible values in {1,2}

2

3

4

5

process p1 {

process p2 {

while (true) {

while (true) {

6

while (in=2) {skip};

while (in=1) {skip};

7

8

CS:

CS:

in := 2;

in := 1

non-CS

non-CS

10

```

- entry protocol: active/busy waiting

- exit protocol: atomic assignment

Good solution? A solution at all? What's good, what's less so?

```

int in = 1

# possible values in {1,2}

2

3

process p1 {

process p2 {

while (true) {

while (true) {

5

while (in=2) {skip};

while (in=1) {skip};

6

CS:

CS:

8

in := 2;

in := 1

non-CS

non-CS

10

```

- entry protocol: active/busy waiting

- exit protocol: atomic assignment

Good solution? A solution at all? What's good, what's less so?

- More than 2 processes?

- Different execution times?

# Desired properties

- Mutual exclusion (Mutex): At any time, at most one process is inside CS.

- 2. Absence of deadlock: If all processes are trying to enter CS, at least one will succeed.

- Absence of unnecessary delay: If some processes are trying to enter CS, while the other processes are in their non-critical sections, at least one will succeed.

- Eventual entry: A process attempting to enter CS will eventually succeed.

**NB**: The three first are safety properties, <sup>14</sup> The last a liveness property.

(SAFETY: no bad state, LIVENESS: something good will happen.)

# Desired properties

- Mutual exclusion (Mutex): At any time, at most one process is inside CS.

- 2. Absence of deadlock: If all processes are trying to enter CS, at least one will succeed.

- Absence of unnecessary delay: If some processes are trying to enter CS, while the other processes are in their non-critical sections, at least one will succeed.

- Eventual entry: A process attempting to enter CS will eventually succeed.

**NB**: The three first are safety properties, <sup>14</sup> The last a liveness property.

(SAFETY: no bad state, LIVENESS: something good will happen.)

<sup>&</sup>lt;sup>14</sup>The question for points 2 and 3, whether it's safety or liveness, is slightly up-to discussion/standpoint!

# Desired properties

- Mutual exclusion (Mutex): At any time, at most one process is inside CS.

- 2. Absence of deadlock: If all processes are trying to enter CS, at least one will succeed.

- Absence of unnecessary delay: If some processes are trying to enter CS, while the other processes are in their non-critical sections, at least one will succeed.

- Eventual entry: A process attempting to enter CS will eventually succeed.

**NB**: The three first are safety properties, <sup>14</sup> The last a liveness property.

(SAFETY: no bad state, LIVENESS: something good will happen.)

$<sup>^{14}</sup>$ The question for points 2 and 3, whether it's safety or liveness, is slightly up-to discussion/standpoint!

# Safety: Invariants (review)

A safety property expresses that a program does not reach a "bad" state. In order to prove this, we can show that the program will never leave a "good" state:

- Show that the property holds in all initial states

- Show that the program statements preserve the property

Such a (good) property is often called a global invariant.

# Safety: Invariants (review)

A safety property expresses that a program does not reach a "bad" state. In order to prove this, we can show that the program will never leave a "good" state:

- Show that the property holds in all initial states

- Show that the program statements preserve the property

Such a (good) property is often called a global invariant.

# Safety: Invariants (review)

A safety property expresses that a program does not reach a "bad" state. In order to prove this, we can show that the program will never leave a "good" state:

- Show that the property holds in all initial states

- Show that the program statements preserve the property

Such a (good) property is often called a *global invariant*.

### Atomic sections

### Used for synchronization of processes

• General form:

$$\langle await(B) S \rangle$$

- B: Synchronization condition

- Executed atomically when B is true

- Unconditional critical section (B is true):

$$\langle S \rangle$$

(1)

S executed atomically

Conditional synchronization: <sup>15</sup>

$$|\operatorname{await}(B)\rangle$$

(2)

### Atomic sections

## Used for synchronization of processes

• General form:

$$\langle await(B) S \rangle$$

- B: Synchronization condition

- Executed atomically when B is true

- Unconditional critical section (B is true):

$$\langle S \rangle$$

(1)

## S executed atomically

Conditional synchronization:<sup>15</sup>

$$\langle await(B) \rangle$$

(2)

## Atomic sections

Used for synchronization of processes

• General form:

$$\langle \mathtt{await}(B) | S \rangle$$

- B: Synchronization condition

- Executed atomically when B is true

- Unconditional critical section (B is true):

$$\langle S \rangle$$

(1)

S executed atomically

Conditional synchronization:<sup>15</sup>

$$\langle await(B) \rangle$$

(2)

$<sup>^{15}</sup>$ We also use then just **await** (B) or maybe **await** B. But also in this case we assume that B is evaluated atomically.

# Critical sections using locks

### Safety properties:

- Mutex

- Absence of deadlock

- Absence of unnecessary waiting

What about taking away the angle brackets <...>

## Critical sections using locks

```

bool lock = false;

process [i=1 to n] {

while (true) {

< await (¬ lock) lock := true >;

CS;

lock := false;

non CS;

}

}

```

### Safety properties:

- Mutex

- Absence of deadlock

- Absence of unnecessary waiting

What about taking away the angle brackets < ... > ?

## Critical sections using locks

```

bool lock = false;

process [i=1 to n] {

while (true) {

< await (¬ lock) lock := true >;

CS;

lock := false;

non CS;

}

```

#### Safety properties:

- Mutex

- Absence of deadlock

- Absence of unnecessary waiting

What about taking away the angle brackets <...>?

# Test & Set is a method/pattern for implementing conditional atomic action:

## Effect of TS(lock)

- side effect: The variable lock will always have value true after TS(lock),

- returned value: true or false, depending on the original state of lock

- exists as an atomic HW instruction on many machines.

# Test & Set is a method/pattern for implementing conditional atomic action:

## Effect of TS(lock)

- side effect: The variable lock will always have value true after TS(lock),

- returned value: true or false, depending on the original state of lock

- exists as an atomic HW instruction on many machines.

# Test & Set is a method/pattern for implementing conditional atomic action:

## Effect of TS(lock)

- side effect: The variable lock will always have value true after TS(lock),

- returned value: true or false, depending on the original state of lock

- exists as an atomic HW instruction on many machines.

## Critical section with TS and spin-lock

## Spin lock:

2

5

6

7

8 9 10

```

bool lock := false;

process p [i=1 to n] {

while (true) {

while (TS(lock)) {skip}; # entry protocol

CS

lock := false; # exit protocol

non-CS

}

}

```

#### NB:

Safety: Mutex, absence of deadlock and of unnecessary delay.

Strong fairness needed to guarantee eventual entry for a process

Variable lock becomes a hotspot!

## Critical section with TS and spin-lock

#### Spin lock:

```

bool lock := false:

2

3

process p [i=1 to n] {

while (true) {

while (TS(lock)) {skip};

# entry protocol

5

CS

6

lock := false;

7

# exit protocol

non-CS

8

10

```

#### NB:

Safety: Mutex, absence of deadlock and of unnecessary delay.

Strong fairness needed to guarantee eventual entry for a process

Variable lock becomes a hotspot!

## Critical section with TS and spin-lock

## Spin lock:

```

bool lock := false:

2

3

process p [i=1 to n] {

while (true) {

while (TS(lock)) {skip};

# entry protocol

5

CS

6

lock := false;

7

# exit protocol

non-CS

8

10

```

#### NB:

Safety: Mutex, absence of deadlock and of unnecessary delay.

Strong fairness needed to guarantee eventual entry for a process

Variable lock becomes a hotspot!

## Better safe than sorry?

What about *double-checking* in the entry protocol whether it is *really, really* safe to enter?

```

bool lock := false;

process p[i = i to n] {

while (true) {

while (lock) {skip}; # additional spin-lock check

while (TS(lock)) {skip};

CS;

lock := false;

non-CS

}

}

```

Does that make sense?

## Better safe than sorry?

What about *double-checking* in the entry protocol whether it is *really, really* safe to enter?

```

bool lock := false;

process p[i = i to n] {

while (true) {

while (lock) {skip};  # additional spin lock check

while (TS(lock)) {

while (lock) {skip}}; # + more inside the TAS loop

CS;

lock := false;

non-CS

}

}

```

Does that make sense?

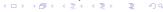

# Multiprocessor performance under load (contention)

# A glance at HW for shared memory

# A glance at HW for shared memory

### Test and test & set

- Test-and-set operation:

- (Powerful) HW instruction for synchronization

- Accesses main memory (and involves "cache synchronization")

- Much slower than cache access

- Spin-loops: faster than TAS loops

- "Double-checked locking": important design pattern/programming idiom for efficient CS (under certain architectures)<sup>16</sup>

## Implementing await-statements

Let CSentry and CSexit implement entry- and exit-protocols to the critical section.

Then the statement < S;> can be implemented by

```

CSentry; S; CSexit;

```

Implementation of conditional critical section < await (B) S;> :

```

CSentry;

while (!B) {CSexit ; CSentry};

S;

CSexit;

```

The implementation can be optimized with Delay between the exit and entry in the body of the while statement.

## Implementing await-statements

Let CSentry and CSexit implement entry- and exit-protocols to the critical section.

Then the statement < S;> can be implemented by

CSentry; S; CSexit;

Implementation of conditional critical section < await (B) S;> :

```

CSentry;

while (!B) {CSexit; CSentry};

S;

CSexit;

```

The implementation can be optimized with Delay between the exit and entry in the body of the while statement.

## Implementing await-statements

Let CSentry and CSexit implement entry- and exit-protocols to the critical section.

Then the statement  $\langle S; \rangle$  can be implemented by

```

CSentry; S; CSexit;

```

Implementation of *conditional critical section* < **await** (B) S;> :

```

CSentry;

while (!B) {CSexit; CSentry};

S;

CSexit;

```

The implementation can be optimized with Delay between the exit and entry in the body of the **while** statement.

## Liveness properties

So far: no(!) solution for "Eventual Entry"-property, except the very first (which did not satisfy "Absence of Unnecessary Delay").

- Liveness: Something good will happen

- Typical example for sequential programs: (esp. in our context)

Program termination<sup>17</sup>

- Typical example for parallel programs:

A given process will eventually enter the critical section

**Note**: For parallel processes, *liveness is affected by the scheduling strategies.*

## Liveness properties

So far: no(!) solution for "Eventual Entry"-property, except the very first (which did not satisfy "Absence of Unnecessary Delay").

- Liveness: Something good will happen

- Typical example for sequential programs: (esp. in our context) Program termination<sup>17</sup>

- Typical example for parallel programs: A given process will eventually enter the critical section

<sup>&</sup>lt;sup>17</sup>In the first version of the slides of lecture 1, termination was defined misleadingly. 4 □ > 4 □ > 4 □ > 4 □ > ...

## Liveness properties

So far: no(!) solution for "Eventual Entry"-property, except the very first (which did not satisfy "Absence of Unnecessary Delay").

- Liveness: Something good will happen

- Typical example for sequential programs: (esp. in our context)

Program termination<sup>17</sup>

- Typical example for parallel programs:

A given process will eventually enter the critical section

**Note:** For parallel processes, *liveness is affected by the scheduling strategies.*

<sup>&</sup>lt;sup>17</sup>In the first version of the slides of lecture 1, termination was defined misleadingly.

- A command is enabled in a state if the statement can in principle be executed next

- Concurrent programs: often more than 1 statement enabled!

## Scheduling: resolving non-determinism

A strategy such that for all points in an execution: if there is more than one statement enabled, pick one of them.

#### **Fairness**

- A command is enabled in a state if the statement can in principle be executed next

- Concurrent programs: often more than 1 statement enabled!

```

bool x := true;

co while (x){ skip }; || x := false co

```

## Scheduling: resolving non-determinism

A strategy such that for all points in an execution: if there is more than one statement enabled, pick one of them.

#### Fairness

- A command is enabled in a state if the statement can in principle be executed next

- Concurrent programs: often more than 1 statement enabled!

```

bool x := true;

co while (x){ skip }; || x := false co

```

## Scheduling: resolving non-determinism

A strategy such that for all points in an execution: if there is more than one statement enabled, pick one of them.

#### Fairness

- A command is enabled in a state if the statement can in principle be executed next

- Concurrent programs: often more than 1 statement enabled!

```

bool x := true;

co while (x){ skip }; || x := false co

```

## Scheduling: resolving non-determinism

A strategy such that for all points in an execution: if there is more than one statement enabled, pick one of them.

#### Fairness

- Fairness: how to pick among enabled actions without being "passed over" indefinitely

- Which actions in our language are potentially non-enabled? <sup>18</sup>

- Possible status changes:

- disabled  $\rightarrow$  enabled (of course),

- ullet but also enabled o disabled

- Differently "powerful" forms of fairness: guarantee of progress

- 1. for actions that are always enabled

- 2. for those that stay enabled

- 3. for those whose enabledness show "on-off" behavior

$<sup>^{18}</sup>$  provided the control-flow/program pointer stands in from took beam. otin > 18

- Fairness: how to pick among enabled actions without being "passed over" indefinitely

- Which actions in our language are potentially non-enabled? <sup>18</sup>

- Possible status changes:

- disabled → enabled (of course),

- but also enabled → disabled

- Differently "powerful" forms of fairness: guarantee of progress

- 1. for actions that are always enabled

- 2. for those that stay enabled

- 3. for those whose enabledness show "on-off" behavior

$<sup>^{18}</sup> provided$  the control-flow/program pointer stands in front of them.  $\center{1}{\equiv}$

- Fairness: how to pick among enabled actions without being "passed over" indefinitely

- Which actions in our language are potentially non-enabled? <sup>18</sup>

- Possible status changes:

- disabled  $\rightarrow$  enabled (of course),

- ullet but also enabled o disabled

- Differently "powerful" forms of fairness: guarantee of progress

- 1. for actions that are always enabled

- 2. for those that stay enabled

- 3. for those whose enabledness show "on-off" behavior

$<sup>^{18}</sup> provided$  the control-flow/program pointer stands in front of them.  $\cite{10}$

- Fairness: how to pick among enabled actions without being "passed over" indefinitely

- Which actions in our language are potentially non-enabled? <sup>18</sup>

- Possible status changes:

- disabled → enabled (of course),

- ullet but also enabled o disabled

- Differently "powerful" forms of fairness: guarantee of progress

- 1. for actions that are always enabled

- 2. for those that stay enabled

- 3. for those whose enabledness show "on-off" behavior

<sup>&</sup>lt;sup>18</sup>provided the control-flow/program pointer stands in front of them.

A scheduling strategy is *unconditionally fair* if each unconditional atomic action which can be chosen, will eventually be chosen.

```

bool x := true;

co while (x){ skip }; || x := false co

```

A scheduling strategy is *unconditionally fair* if each unconditional atomic action which can be chosen, will eventually be chosen.

```

bool x := true;

co while (x){ skip }; || x := false co

```

A scheduling strategy is *unconditionally fair* if each unconditional atomic action which can be chosen, will eventually be chosen.

```

bool x := true;

co while (x){ skip }; || x := false co

```

- x := false is unconditional

- ⇒ The action will eventually be chosen

- This guarantees termination

- Example: "Round robin" execution

- Note: if-then-else, while (b); are not conditional atomic statements!

A scheduling strategy is *unconditionally fair* if each unconditional atomic action which can be chosen, will eventually be chosen.

```

1 | bool x := true;

2 | co while (x){ skip }; || x := false co

```

- x := false is unconditional

- ⇒ The action will eventually be chosen

- This guarantees termination

- Example: "Round robin" execution

- Note: if-then-else, while (b); are not conditional atomic statements!

A scheduling strategy is *unconditionally fair* if each unconditional atomic action which can be chosen, will eventually be chosen.

```

bool x := true;

co while (x){ skip }; || x := false co

```

- x := false is unconditional

- ⇒ The action will eventually be chosen

- This guarantees termination

- Example: "Round robin" execution

- Note: if-then-else, while (b); are not conditional atomic statements!

#### Weak fairness

#### Weak fairness

A scheduling strategy is weakly fair if

- it is unconditionally fair

- every conditional atomic action will eventually be chosen, assuming that the condition becomes true and thereafter remains true until the action is executed.

#### Example:

```

bool x = true, int y = 0;

co while (x) y = y + 1; || < await y \ge 10; > x = false; oc

```

#### Weak fairness

#### Weak fairness

A scheduling strategy is weakly fair if

- it is unconditionally fair

- every conditional atomic action will eventually be chosen, assuming that the condition becomes true and thereafter remains true until the action is executed.

#### Example:

```

bool x = \text{true}, int y = 0;

co while (x) y = y + 1; || < await y \ge 10; > x = \text{false}; oc

```

#### Weak fairness

A scheduling strategy is weakly fair if

- it is unconditionally fair

- every conditional atomic action will eventually be chosen, assuming that the condition becomes true and thereafter remains true until the action is executed.

#### Example:

```

\begin{array}{|c|c|c|c|c|} \hline \textbf{bool} \ \times = \ \textbf{true} \ , \ \ \textbf{int} \ \ y = 0; \\ \hline \textbf{co while} \ \ (\times) \ \ y = y + 1; \ \ |\ | < \ \textbf{await} \ \ y \geq 10; \ > \times = \ \textbf{false} \ ; \ \ \textbf{oc} \end{array}

```

- ullet When y  $\geq$  10 becomes true, this condition remains true

- This ensures termination of the program

- Example: Round robin execution

## Strong fairness

#### Example

### Strong fairness

#### Example

## Definition (Strongly fair scheduling strategy)

- unconditionally fair and

- each conditional atomic action will eventually be chosen, if the condition is true infinitely often.

## Strong fairness

#### Example

### Definition (Strongly fair scheduling strategy)

- unconditionally fair and

- each conditional atomic action will eventually be chosen, if the condition is true infinitely often.

#### For the example:

- under strong fairness: y true  $\infty$ -often  $\Rightarrow$  termination

- under weak fairness: non-termination possible

# Fairness for critical sections using locks

The CS solutions shown need to assume strong fairness to guarantee liveness, i.e., access for a given process (i):

- Steady inflow of processes which want the lock

- value of lock alternates (infinitely often) between true and false

- Weak fairness:

Process i can read lock only when the value is false

- Strong fairness:

Guarantees that i eventually sees that lock is true

**Difficult**: to make a scheduling strategy that is both practical and strongly fair.

We look at CS solutions where access is guaranteed for *weakly* fair strategies

## Fairness for critical sections using locks

The CS solutions shown need to assume strong fairness to guarantee liveness, i.e., access for a given process (i):

- Steady inflow of processes which want the lock

- value of lock alternates

(infinitely often) between true and false

- Weak fairness:

Process i can read lock only when the value is false

- Strong fairness:

Guarantees that i eventually sees that lock is true

**Difficult:** to make a scheduling strategy that is both practical and strongly fair.

We look at CS solutions where access is guaranteed for *weakly* fair strategies

## Fairness for critical sections using locks

The CS solutions shown need to assume strong fairness to guarantee liveness, i.e., access for a given process (i):

- Steady inflow of processes which want the lock

- value of lock alternates

(infinitely often) between true and false

- Weak fairness:

Process i can read lock only when the value is false

- Strong fairness:

Guarantees that i eventually sees that lock is true

**Difficult:** to make a scheduling strategy that is both practical and strongly fair.

We look at CS solutions where access is guaranteed for *weakly* fair strategies

## Fair solutions to the CS problem

- Tie-Breaker Algorithm

- Ticket Algorithm

- The book also describes the bakery algorithm

- Requires no special machine instruction (like TS)

- We will look at the solution for two processes

- Each process has a private lock

- Each process sets its lock in the entry protocol

- The private lock is read, but is not changed by the other process

- Requires no special machine instruction (like TS)

- We will look at the solution for two processes

- Each process has a private lock

- Each process sets its lock in the entry protocol

- The private lock is read, but is not changed by the other process

- Requires no special machine instruction (like TS)

- We will look at the solution for two processes

- Each process has a private lock

- Each process sets its lock in the entry protocol

- The private lock is read, but is not changed by the other process

- Requires no special machine instruction (like TS)

- We will look at the solution for two processes

- Each process has a private lock

- Each process sets its lock in the entry protocol

- The private lock is read, but is not changed by the other process

#### Naive solution

```

int in = 1

# possible values in {1,2}

1

2

3

process p1 {

4

5

process p2 {

while (true) {

while (true) {

6

while (in=2) \{skip\};

while (in=1) {skip};

7

CS:

CS:

8

in := 2;

in := 1

non-CS

non-CS

10

```

- entry protocol: active/busy waiting

- exit protocol: atomic assignment

```

in1 := false, in2 := false;

2

process p1 {

process p2 {

while (true){

while (true) {

while (in2) {skip};

while (in1) {skip};

5

in1 := true;

in2 := true;

6

CS

CS:

7

in1 := false;

in2 := false;

non-CS

non-CS

10

11

```

```

in1 := false, in2 := false;

process p2 {

3

process p1 {

while (true){

while (true) {

while (in2) {skip};

while (in1) {skip};

5

in1 := true;

in2 := true;

6

CS

CS:

in1 := false;

in2 := false;

non-CS

non-CS

10

11

```

What is the global invariant here?

```

in1 := false, in2 := false;

2

process p2 {

process p1 {

while (true) {

while (true){

while (in2) {skip};

while (in1) {skip};

5

in1 := true;

in2 := true;

6

CS

CS:

in1 := false;

in2 := false;

non-CS

non-CS

10

11

```

What is the global invariant here?

Problem: No mutex

```

in1 := false, in2 := false;

process p2 {

process p1 {

while (true){

while (true) {

while (in2) {skip};

while (in1) {skip};

5

in1 := true;

in2 := true;

CS

CS :

7

in1 := false;

in2 := false;

non-CS

non-CS

10

11

```

- Problem seems to be the entry protocol

- Reverse the order: first "set", then "test"

```

in1 := false, in2 := false;

2

3

process p1 {

process p2 {

while (true) {

while (true){

4

in1 := true;

in2 := true;

5

while (in1) {skip};

while (in2) {skip};

6

7

CS

CS:

in1 := false;

in2 := false;

non-CS

non-CS

10

11

```

- Problem seems to be the entry protocol

- Reverse the order: first "set", then "test"

```

in1 := false, in2 := false;

2

3

process p1 {

process p2 {

while (true){

while (true) {

4

in1 := true;

in2 := true;

5

while (in2) {skip};

while (in1) {skip};

6

CS

CS:

7

in1 := false;

in2 := false;

8

non-CS

non-CS

10

11

```

$Deadlock^{19}:-($

129 / 578

<sup>&</sup>lt;sup>19</sup>Technically, it's more of a live-lock, since the processes still are doing "something", namely spinning endlessly in the empty while-loops, never leaving the entry-protocol to do real work. The situation though is analogous to a "deadlock" conceptually.

- ullet Problem: both half flagged their wish to enter  $\Rightarrow$  deadlock

- Avoid deadlock: "tie-break"

- Be fair: Don't always give priority to one specific process

- Need to know which process last started the entry protocol.

- Add new variable: last

- Problem: both half flagged their wish to enter ⇒ deadlock

- Avoid deadlock: "tie-break"

- Be fair: Don't always give priority to one specific process

- Need to know which process last started the entry protocol.

- Add new variable: last

```

rocess pl {

while (true) {

in1 := true;

last := 1;

< await ( (not in2) or last = 2); >

CS

in1 := false;

non-CS

}

}

process p2 {

while (true) {

in2 := true;

last := 2;

< await ( (not in1) or last = 1); >

CS

in2 := false;

non-CS

}

```

- Problem: both half flagged their wish to enter ⇒ deadlock

- Avoid deadlock: "tie-break"

- Be fair: Don't always give priority to one specific process

- Need to know which process last started the entry protocol.

- Add new variable: last

```

in1 := false, in2 := false; int last

```

- Problem: both half flagged their wish to enter ⇒ deadlock

- Avoid deadlock: "tie-break"

- Be fair: Don't always give priority to one specific process

- Need to know which process last started the entry protocol.

- Add new variable: last

```

in1 := false, in2 := false; int last

```

Even if the variables in1, in2 and last can change the value while a wait-condition evaluates to true, the wait condition will remain true.

p1 sees that the wait-condition is true:

- in2 = false

- in2 can eventually become true,

but then p2 must also set last to 2

- Then the wait-condition to p1 still holds

- last = 2

- Then last = 2 will hold until p1 has executed

Thus we can replace the await-statement with a while-loop

Even if the variables in1, in2 and last can change the value while a wait-condition evaluates to true, the wait condition will remain true.

p1 sees that the wait-condition is true:

- in2 = false

- in2 can eventually become true,

but then p2 must also set last to 2

- Then the wait-condition to p1 still holds

- last = 2

- Then last = 2 will hold until p1 has executed

Thus we can replace the await-statement with a while-loop

Even if the variables in1, in2 and last can change the value while a wait-condition evaluates to true, the wait condition will remain true.

p1 sees that the wait-condition is true:

- in2 = false

- in2 can eventually become true,

but then p2 must also set last to 2

- Then the wait-condition to p1 still holds

- last = 2

- Then last = 2 will hold until p1 has executed

Thus we can replace the await-statement with a while-loop

Even if the variables in1, in2 and last can change the value while a wait-condition evaluates to true, the wait condition will remain true.

p1 sees that the wait-condition is true:

- in2 = false

- in2 can eventually become true,

but then p2 must also set last to 2

- Then the wait-condition to p1 still holds

- last = 2

- Then last = 2 will hold until p1 has executed

Thus we can replace the **await**-statement with a **while**-loop.

```

process p1 {

while (true){

in1 := true;

last := 1;

while (in2 and last = 2){skip}

CS

in1 := false;

non-CS

}

}

```

Generalizable to many processes (see book)

```

process p1 {

while (true){

in1 := true;

last := 1;

while (in2 and last = 2){skip}

CS

in1 := false;

non-CS

}

}

```

Generalizable to many processes (see book)

# Ticket algorithm

Scalability: If the Tie-Breaker algorithm is scaled up to n processes, we get a loop with n-1 2-process Tie-Breaker algorithms.

The *ticket algorithm* provides a simpler solution to the CS problem for *n* processes.

- Works like the "take a number" queue at the post office (with one loop)

- A customer (process) which comes in takes a number which is higher than the number of all others who are waiting

- The customer is served when a ticket window is available and the customer has the lowest ticket number.

# Ticket algorithm

Scalability: If the Tie-Breaker algorithm is scaled up to n processes, we get a loop with n-1 2-process Tie-Breaker algorithms.

The *ticket algorithm* provides a simpler solution to the CS problem for *n* processes.

- Works like the "take a number" queue at the post office (with one loop)

- A customer (process) which comes in takes a number which is higher than the number of all others who are waiting

- The customer is served when a ticket window is available and the customer has the lowest ticket number.

# Ticket algorithm

Scalability: If the Tie-Breaker algorithm is scaled up to n processes, we get a loop with n-1 2-process Tie-Breaker algorithms.

The *ticket algorithm* provides a simpler solution to the CS problem for *n* processes.

- Works like the "take a number" queue at the post office (with one loop)

- A customer (process) which comes in takes a number which is higher than the number of all others who are waiting

- The customer is served when a ticket window is available and the customer has the lowest ticket number.

# Ticket algorithm: Sketch (*n* processes)

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

5

< turn[i] := number; number := number +1 >;

< await (turn[i] = next)>;

6

7

CS

8

<next = next + 1>;

9

non-CS

10

11

```

- The first line in the loop must be performed atomically!

- await-statement: can be implemented as while-loop

- Some machines have an instruction fetch-and-add (FA)

FA(var, incr):< int tmp := var; var := var + incr; return tmp;>

# Ticket algorithm: Sketch (*n* processes)

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

5

< turn[i] := number; number := number +1 >;

< await (turn[i] = next)>;

6

7

CS

8

<next = next + 1>;

non-CS

10

11

```

- The first line in the loop must be performed atomically!

- await-statement: can be implemented as while-loop

- Some machines have an instruction fetch-and-add (FA)

FA(var, incr):< int tmp := var; var := var + incr; return tmp;>

# Ticket algorithm: Sketch (*n* processes)

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

5

< turn[i] := number; number := number +1 >;

< await (turn[i] = next)>;

6

7

CS

8

<next = next + 1>;

non-CS

9

10

11

```

- The first line in the loop must be performed atomically!

- await-statement: can be implemented as while-loop

- Some machines have an instruction fetch-and-add (FA):

FA(var, incr):< int tmp := var; var := var + incr; return tmp;>

# Ticket algorithm: Implementation

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

turn[i] := FA(number, 1);

5

while (turn [i] != next) {skip};

6

7

CS

8

next := next + 1;

non-CS

10

11

```

```

FA(var, incr): < int tmp := var; var := var + incr; return tmp; >

```

Without this instruction, we use an extra CS:20

```

CSentry; turn[i]=number; number = number + 1; CSexit

```

Problem with fairness for CS. Solved with the bakery algorithm (see book).

<sup>&</sup>lt;sup>20</sup>Why?

## Ticket algorithm: Implementation

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

turn[i] := FA(number, 1);

5

while (turn [i] != next) {skip};

6

7

CS

8

next := next + 1;

non-CS

10

11

```

```

FA(var, incr):< int tmp := var; var := var + incr; return tmp;>

```

Without this instruction, we use an extra CS:20

```

CSentry; turn[i]=number; number = number + 1; CSexit;

```

Problem with fairness for CS. Solved with the bakery algorithm (see book).

<sup>&</sup>lt;sup>20</sup>Why?

## Ticket algorithm: Implementation

```

int number := 1; next := 1; turn [1:n] := ([n] \ 0);

2

3

process [i = 1 \text{ to } n] {

while (true) {

4

turn[i] := FA(number, 1);

5

while (turn [i] != next) {skip};

6

7

CS

8

next := next + 1;

non-CS

10

11

```

```

FA(var, incr):< int tmp := var; var := var + incr; return tmp;>

```

Without this instruction, we use an extra CS:20

```

CSentry; turn[i]=number; number = number + 1; CSexit;

```

Problem with fairness for CS. Solved with the bakery algorithm (see book).

<sup>&</sup>lt;sup>20</sup>Why?

#### **Invariants**

- What is the global invariant for the ticket algorithm?

- What is the local invariant for process is

#### **Invariants**

• What is the global invariant for the ticket algorithm?

0 < next≤number

What is the local invariant for process i:

#### **Invariants**

• What is the global invariant for the ticket algorithm?

0 < next<number

• What is the *local* invariant for process *i*:

#### **Invariants**

• What is the global invariant for the ticket algorithm?

```

0 < next<number

```

- What is the *local* invariant for process *i*:

- turn[i] < number</li>

- if p[i] is in the CS then turn[i] == next.

#### **Invariants**

• What is the *global* invariant for the ticket algorithm?

```

0 < next<number

```

- What is the *local* invariant for process *i*:

- turn[i] < number</li>

- if p[i] is in the CS then turn[i] == next.

- for pairs of processes  $i \neq j$ :

```

if turn[i] > 0 then turn[j] \neq turn[i]

```

#### **Invariants**

• What is the global invariant for the ticket algorithm?

- What is the *local* invariant for process *i*:

- turn[i] < number</li>

- if p[i] is in the CS then turn[i] == next.

- for pairs of processes  $i \neq j$ :

if

$$turn[i] > 0$$

then  $turn[j] \neq turn[i]$

This holds initially, and is preserved by all atomic statements.

## Barrier synchronization

- Computation of disjoint parts in parallel (e.g. array elements).

- Processes go into a loop where each iteration is dependent on the results of the previous.

```

process Worker[i=1 to n] {

while (true) {

task i;

wait until all n tasks are done # barrier

}

}

```

All processes must reach the barrier ("join") before any can continue.

## Barrier synchronization

- Computation of disjoint parts in parallel (e.g. array elements).

- Processes go into a loop where each iteration is dependent on the results of the previous.

```

process Worker[i=1 to n] {

while (true) {

task i;

wait until all n tasks are done # barrier

}

}

```

All processes must reach the barrier ("join") before any can continue.

## Barrier synchronization

- Computation of disjoint parts in parallel (e.g. array elements).

- Processes go into a loop where each iteration is dependent on the results of the previous.

```

process Worker[i=1 to n] {

while (true) {

task i;

wait until all n tasks are done # barrier

}

}

```

All processes must reach the barrier ("join") before any can continue.

A number of processes will synchronize the end of their tasks. Synchronization can be implemented with a *shared counter*:

Can be implemented using the FA instruction.

#### Disadvantages:

- count must be reset between each iteration.

- Must be updated using atomic operations.

- Inefficient: Many processes read and write count concurrently.

#### Shared counter

A number of processes will synchronize the end of their tasks. Synchronization can be implemented with a *shared counter*:

```

int count := 0;

process Worker[i=1 to n] {

while (true) {

task i;

< count := count+1>;

< await(count=n)>;

}

}

```

Can be implemented using the FA instruction.

#### Disadvantages:

- count must be reset between each iteration.

- Must be updated using atomic operations.

- Inefficient: Many processes read and write count concurrently.

#### Shared counter

A number of processes will synchronize the end of their tasks. Synchronization can be implemented with a *shared counter*:

Can be implemented using the FA instruction.

#### Disadvantages

- count must be reset between each iteration.

- Must be updated using atomic operations.

- Inefficient: Many processes read and write count concurrently.

A number of processes will synchronize the end of their tasks. Synchronization can be implemented with a *shared counter*:

Can be implemented using the FA instruction.

#### Disadvantages:

- count must be reset between each iteration.

- Must be updated using atomic operations.

- Inefficient: Many processes read and write count concurrently.

#### Goal: Avoid too many read- and write-operations on one variable!!

Divides shared counter into several local variables

```

Worker[i]:

arrive[i] = 1;

< await (continue[i] == 1);>

Coordinator:

for [i=1 to n] < await (arrive[i]==1);>

for [i=1 to n] continue[i] = 1;

```

NB: In a loop, the flags must be cleared before the next iteration!

#### Flag synchronization principles:

- 1. The process waiting for a flag is the one to reset that flag

- 2. A flag will not be set before it is reset

Goal: Avoid too many read- and write-operations on one variable!!

Divides shared counter into several local variables.

```

Worker[i]:

arrive[i] = 1;

< await (continue[i] == 1);>

Coordinator:

for [i=1 to n] < await (arrive[i]==1);>

for [i=1 to n] continue[i] = 1;

```

NB: In a loop, the flags must be cleared before the next iteration!

- 1. The process waiting for a flag is the one to reset that flag

- 2. A flag will not be set before it is reset

Goal: Avoid too many read- and write-operations on one variable!!

Divides shared counter into several local variables.