## Last time – and today, Tuesday 16th of March:

### Last time:

- 13.1 Integrating Converters

- 13.2 Successive-Approx. Converters

- 13.3 Algorithmic (or cyclic) A/D Converters

- 13.4 Flash (or parallel) converters

- 13.5 Two-Step A/D converters

- 13.8 Pipelined A/D Converters

- 13.9 Time-Interleaved A/D Converters

### Today – from the following chapters:

- 13.6 Interpolating A/D Converters

- 13.7 Folding A/D Converters

- 14.1 Oversampled converters

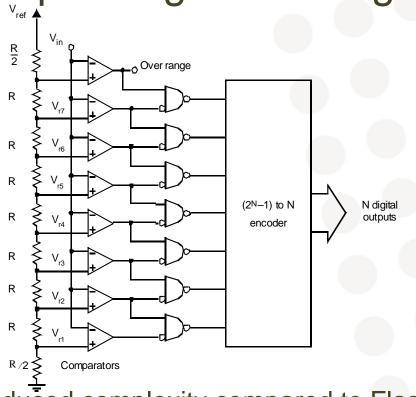

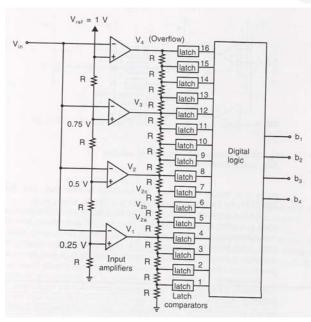

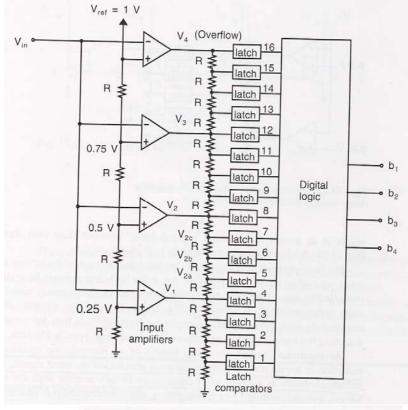

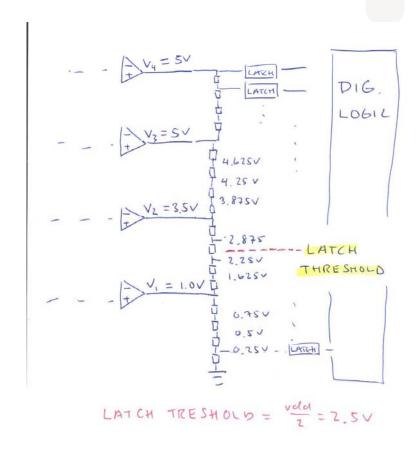

## Interpolating ADCs. Rightmost interpol.=4 (1/4)

- Reduced complexity compared to Flash ADCs → reduced input capacitance and slightly reduced power.

- In the <u>mathematical</u> subfield of <u>numerical analysis</u>, **interpolation** is a method of constructing new data points within the range of a <u>discrete set</u> of <sup>16</sup>kmown data points.

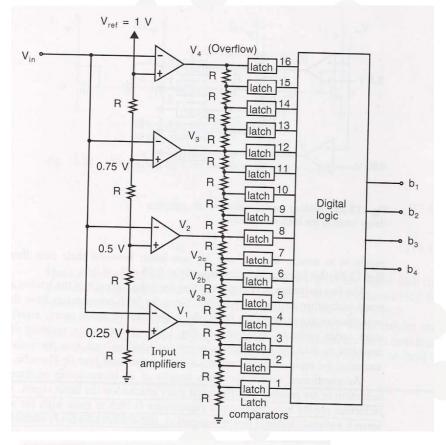

# Interpolating ADCs (2/4)

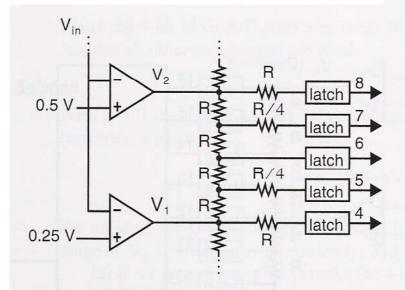

- Uses input amplifiers behaving as linear amplifiers near their threshold voltages, allowed to saturate for moderately large input signals

- Thus "noncritical" latches need only determine the sign of the amplifier outputs

# Interpolating ADCs (3/4)

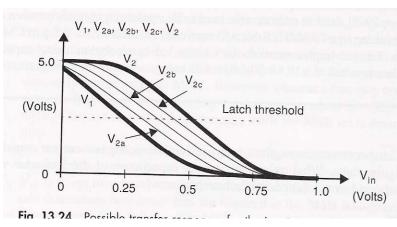

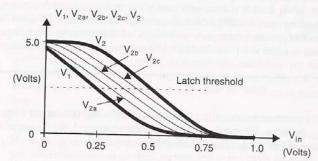

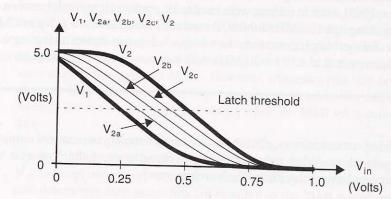

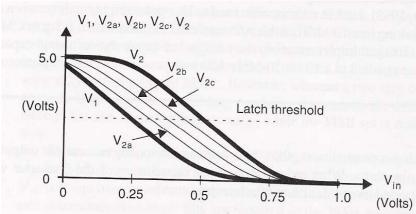

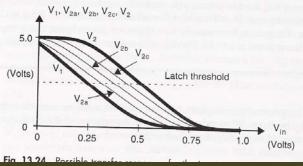

- Amplifier outputs V<sub>1</sub> and V<sub>2</sub> as well as their interpolated values are shown lowermost (fig. 13.24)

- The reference points created from interpolated values (for example V<sub>2a</sub>, V<sub>2b</sub>, V<sub>2c</sub>) have latches potentially triggering in order, for increasing (or decreasing) input.

- For good linearity the interpolated signals need only cross the latch threshold at the correct points

# Interpolating ADCs (4/4)

Fig 13 24 Possible transfer ---- ( il .

**Fig. 13.25** Adding series resistors to equalize delay times to the latch comparators.

- To achieve good linearity V<sub>1</sub> and V<sub>2</sub> need to be linear between their own thresholds. In figure 13.24 this linear region corresponds to 0.25 < V<sub>in</sub> < 0.5 (horizontally)</li>

- For fast operation the delays to each of the latches must be made to equal each other as much as possible. In fig. 13.25 this is done using resistors.

# Example, based on Fig. 13.23 (1/2)

Vin = 0.4 V, gain of

-10, logic levels of 0

and 5 volts. →

# Example – interpolating ADC (2/2)

16. mars 2010

8

JNIVERSITETET OSLO

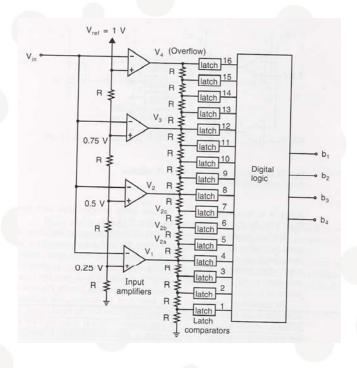

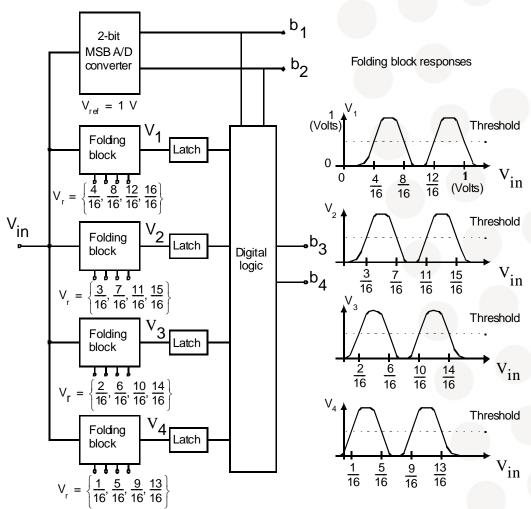

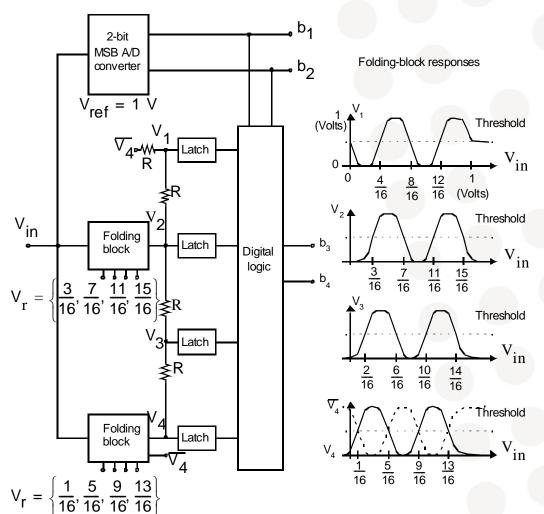

# Folding A/D Converters (13.7)

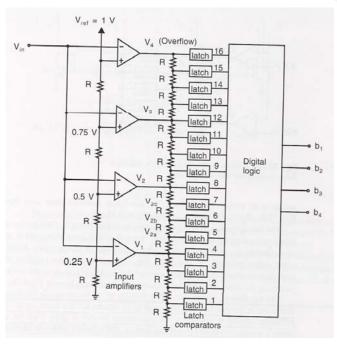

- The number of latches is reduced compared to the interpolating ADC, and even more from FLASH

- The figure shows a 4 bit converter with folding rate of 4

- A group of LSBs are found separately from a group of MSBs.

- whether the input signal, V<sub>in</sub>, is in one of four voltage regions (between 0 and ¼, ¼ and ½, ½ and ¾, or ¾ and 1)

- V<sub>1</sub> to V<sub>4</sub> produce a

thermometer code for each of the four MSB regions

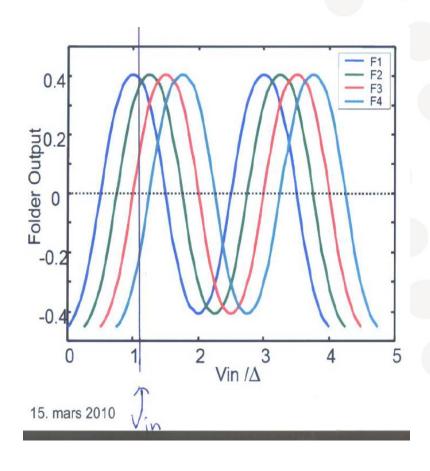

## Similar to folding block responses on previous slide..

- Bipolar folder outputs

- Ex: Input 1.05:

- F1 > threshold=0 -> "1"

- F2 > threshold=0 -> "1"

- F3 > threshold=0 -> "1"

- F4 < threshold=0 -> "0"

- Thermometer code produced for each of the four MSB regions (between 0 and ¼, ¼ and ½, ½ and ¾, or ¾ and 1 for previous slide)

- (in certain respects related to interpolation in Fig 13.24)

16. mars 2010

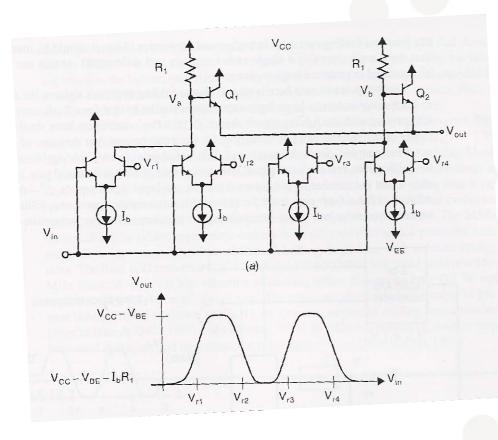

# Folding block with a folding rate of four

- Input-output response for the cross-coupled differential pair is shown lowermost

- Vout is low if, and only if, both V<sub>a</sub> and V<sub>b</sub> are low, otherwise high

- The output from a folding block is at a much higher frequency than the input signal, limiting the practical folding rate.

- Differential solutions in practice

# Folding and Interpolating ADC

- By introducing interpolation, the number of folding blocks is reduced

- Input capacitance is reduced (if both folding and interpolating is combined)

- Folding-rate of four and interpolate-by-two

- (Literature references on page 523)

## Interpolating and folding and interpolating ADCs

| Resolution | Sampling rate | ENOB                      | Power dissip.   | Supply<br>voltage | architecture              | reference                                         |

|------------|---------------|---------------------------|-----------------|-------------------|---------------------------|---------------------------------------------------|

| 8 bit      | 100 MHz       | 6.5 bit@5V,<br>7.1 bit@8V | 1.2W@5V         | 5 or 8 V          | interpolating             | Steyaert ,<br>Roovers,<br>Craninckx,<br>CICC 1993 |

| 5 bit      | 5 GHz         | 4 bit at 5GHz             | 113<br>mW@1V    | 1 V               | interpolating             | Wang, Liu,<br>VLSI-DAT<br>'2007                   |

| 6 bit      | 200 MHz       | 5.35 bit                  | 35<br>mW@3.3V   | 3.3V              | folding and interpolating | Yin, Wang,<br>Liu, ICSICT,<br>2008                |

| 6 bit      | 200 MHz       | 5.5 bit                   | 78.8<br>mW@2.5V | 2.5V              | folding and interpolating | Silva,<br>Fernandes,<br>ISCAS, 2003               |

|            |               |                           |                 |                   |                           |                                                   |

16. mars 2010

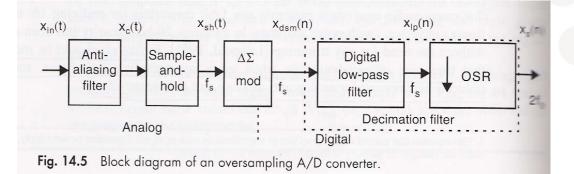

## Oversampling converters (chapter 14 in "J & M")

For high resolution, low-to-medium-speed applications like for example digital audio

- Relaxes requirements placed on analog circuitry, including matching tolerances and amplifier gains

- Simplify requirements placed on the analog antialiasing filters for A/D converters and smoothing filters for D/A converters.

- Sample-and-Hold is usually not required on the input

- Extra bits of resolution can be extracted from converters that samples much faster than the Nyquist-rate. Extra resolution can be obtained with lower oversampling rates by exploiting noise shaping

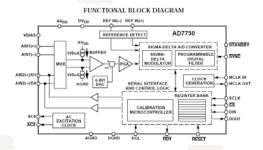

# Resolution and clock cycles per sample

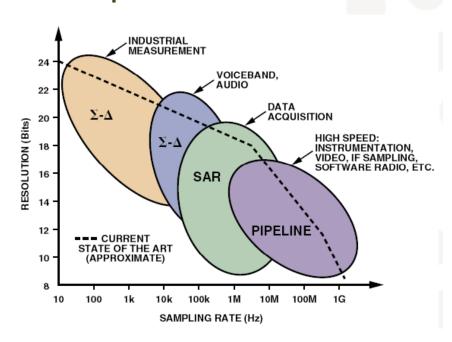

. Dependence of achievable resolution and required clock cycles per sample for various ADC systems.

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 27, NO. 10, OCTOBER 1992

A Gigasample/Second 5-b ADC with On-Chip Track and Hold Based on an Industrial 1-μm GaAs MESFET E/D Process

Richard Hagelauer, Member, IEEE, Frank Oehler, Günter Rohmer, Josef Sauerer, and Dieter Seitzer, Senior Member, IEEE

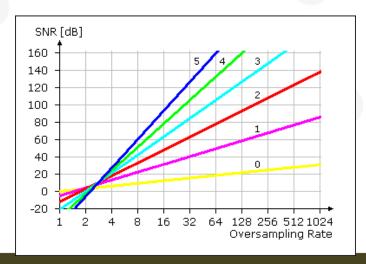

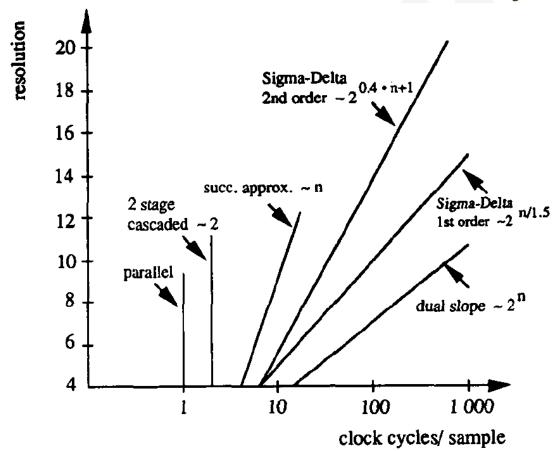

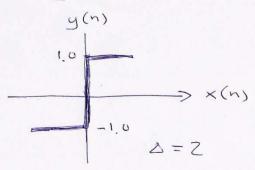

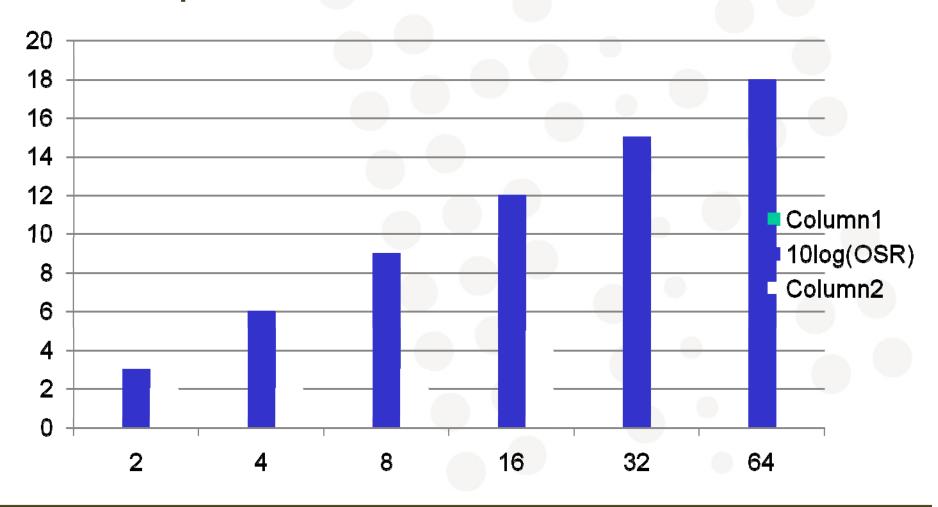

## Nyquist Sampling and Oversampling

- Figure from [Kest05]

- Straight oversampling gives an SNR improvement of 3 dB / octave

- $fs > 2f_0 (2f_0 = Nyquist Rate)$

- OSR =  $f_s/2f_0$

- SNRmax = 6.02N+1.76+ 10log (OSR)

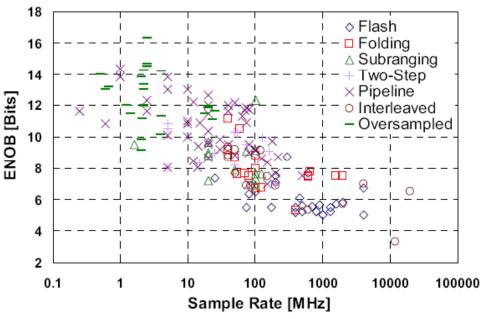

# Oversampled converters; High resolution and relatively low speed

Figure 1. ADC architectures, applications, resolution, and sampling rates.

Fig. 2. ADC sample rate vs. ENOB from 1987 to 2005.

# Which ADC Architecture Is Right for Your Application?

By Walt Kester [walt.kester@analog.com]

IEEE 2005 CUSTOM INTEGRATED CIRCUITS CONFERENCE

Scaling of Analog-to-Digital Converters into Ultra-Deep-Submicron CMOS

Y. Chiu 1, B. Nikolić 2, and P. R. Gray 2

<sup>&</sup>lt;sup>1</sup> Electrical and Computer Engineering, University of Illinois at Urbana-Champaign

<sup>&</sup>lt;sup>2</sup> Electrical Engineering and Computer Sciences, University of California at Berkeley

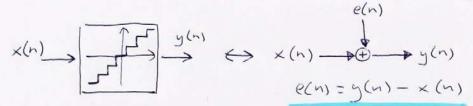

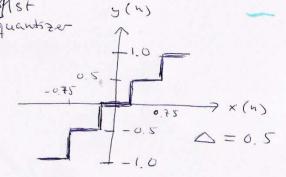

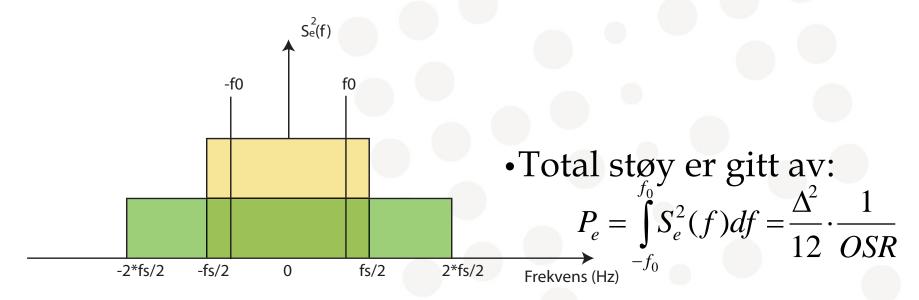

### QUANTIZATION NOISE (p. 532-533 Th "Jdm")

The quantization voice is the difference between the input and output values.

This model is exact under the assumption that the quantization error is strongly related to the input signed ("I'd m" p. 532). The model becomes approximate when consumptions are made about the Statistical properties. Of e(n), such as e(n) being an independent white-noise signal. This model leads to a simpler undertanding of ZA and with some exceptions is usually reasonably accurate.

- If x(n) is very active, e(n) can be approximated as an independent random number uniformly distributed between ± €, where △ equals the difference between two adjacent,

quantization levels.

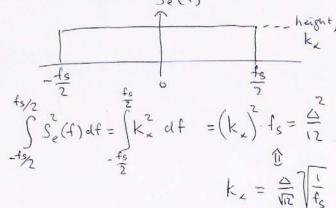

Thus, the quantization noise

power equals  $\frac{\Delta^2}{12}$  (sec. 11.3)

and is independent of the

Sampling frequency, fs

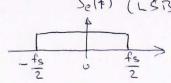

The spectral density of e(n),

Se(f) is white (constant over freq.)

and all its power within ± fs/2,

as shown in the figure:

Se(f)

The spectral density height is calculated by noting that the total noise power is 62/12 and with a two-sided def. of power equals the area under Se(f) within +/- fs/2

14.1 Output and quantization errors for two quantizariest ×(n) = {0.01, 0.31, -0.11, 0.80, 0.52, -0.70} = quantizer Quantizer 1:  $y(n) = \{0.0, 0.5, 0, 1.0, 0.5, -0.5\}$ Quantizer 2:

$$y_2(n) = \{1.0, 1.0, -1.0, 1.0, 1.0, -1.0\}$$

e(n) is approximated as an independent

random number uniformly distributed between # = where A equals the difference between two adjacent

quantitation levels. Pe = \$\frac{\Delta}{12}\$

quant. ?:

$$\frac{\Delta c_{\text{m}}}{12} = \frac{2 c_{\text{m}}}{12} = 0.33 (\text{m})$$

e(n) = y(n) - x(n)

"OVERSAMPLING IS BASED ON THE ASSUMPTION THAT AN ADC'S TOTAL QUANTIZATION NOISE POWER (VARIANCE) IS THE SQUARED VALUE OF THE CONVERTER'S LEAST SIGNIFICANT BIT Self) (LSB) VOLTAGE DIVIDED BY 12" (LYONS'OF)

$$S_{eI}^{2}(f) = \frac{0.02083}{211} \left[ \frac{W}{rad/gample} \right] = 0.00331 \frac{W}{vad/gample}$$

$$S_{eII}^{2}(f) = \frac{0.333}{211} \left[ \frac{W}{rad/gample} \right] = 0.053 \frac{W}{rad/gample}$$

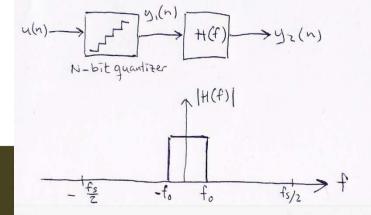

### GVERSAMPLING

signal of interest is bandlimited to to

After quantization, y, (n) is filtered by H(f) to create yz (n) that eliminates quantization norse (together with any other signals) greater than fo.

ADVANTAGE P. 535 PEAKT

If the input is Sinusoidal, its maximum peak value without clipping is  $2^{N}(\Delta/2)$  For this wave the signal power,  $P_{s}$ , has a power equal to  $P_{s} = \left(\frac{\Delta 2^{N} + 1}{2}\right)^{2} = \frac{\Delta^{2} 2^{N}}{8}$

The power of the input signal within yz(n) remains the same as before since we assumed the signal's frequency content is below to.

HOWEVER, THE QUANTIZATION NOISE POWER IS

REDUCED TO  $f_{s/2}$   $P_{e} = \int_{-4s_{2}}^{2} S_{e}^{2}(f) |H(f)|^{2} df = \int_{-4s_{2}}^{2} k_{x}^{2} df$

$$= \frac{2f_0}{f_s} \cdot \frac{\Delta^2}{12} = \frac{\Delta^2}{12} \left[ \frac{1}{0SR} \right]$$

EREFORE DOUBLING OSR DECRE

THEREFORE, DOUBLING OSR DECREASES

THE QUANTIZATION NOISE POWER BY ONEHALF, OR EQUIVALENTLY, 3 dB (or equiv. OSbits)

SNR<sub>mAx</sub> = lo log

$$\left(\frac{Ps}{Pe}\right)$$

= lo log  $\left(\frac{3}{2}2^{2N}\right)$  + lo log (GSR)

= 6.02N + 1.76 + lo log (GSR) [dB]

due to N-bit quantiter due to oversampling

$$= 10 \log \frac{3}{2} \cdot 2^{2N} + 10 \log 6SR$$

$$= 10 \log \frac{3}{2} + 10 \log 2^{2N} + 10 \log 6SR$$

$$= 10 \log 2^{2N} + 1.76 + 10 \log 6SR$$

$$= 10 \cdot 2N \cdot \log 2 + 1.76 + 10 \log 6SR$$

$$= 10 \cdot 2 \cdot N \cdot \log 2 + 1.76 + 10 \log 6SR$$

$$= 10 \cdot 2 \cdot N \cdot 0.301 + 1.76 + 10 \log 6SR$$

16. mars 2010

## Oversampling (without noise shaping)

- Doubling of the sampling frequency increases the dynamic range by 3 dB = 0.5 bit.

- To get a high SNR a very high fs is needed → high power consumption.

- Oversampling usually combined with noise shaping and higher order modulators, for higher increase in dynamic range per octave ("OSR")

# SNRmax = 6.02N+1.76+10log(OSR) [dB] SNR improvement 0.5 bits / octave

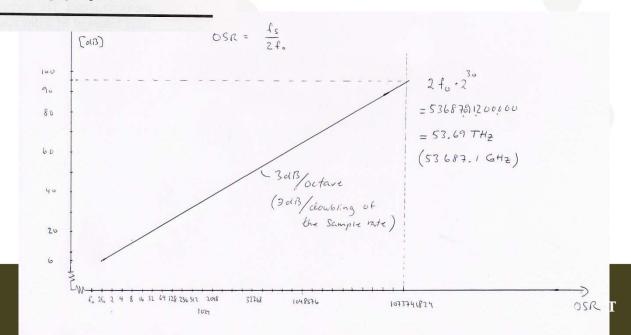

#### **EXAMPLE 14.3**

Given that a 1-bit A/D converter has a 6-dB SNR, what sample rate is required using oversampling (no noise shaping) to obtain a 96-dB SNR (i.e., 16 bits) if  $f_0 = 25 \text{ kHz}$ ? (Note that the input into the A/D converter has to be very active for the white-noise quantization model to be valid—a difficult arrangement when using a 1-bit quantizer with oversampling without noise shaping).

#### Solution

Oversampling (without noise shaping) gives 3 dB/octave where 1 octave implies doubling the sampling rate. We require 90 dB divided by 3 dB/octave, or 30 octaves. Thus, the required sampling rate,  $f_{\rm s}$ , is

$$f_s = 2^{30} \times 2f_0 \cong 54,000 \text{ GHz}!$$

This example shows why noise shaping is needed to improve the SNR faster than 3 dB/octave, since 54,000 GHz is highly impractical.

## Advantages of 1-bit A/D converters (p.537 in "J&M")

- Oversampling improves signal-to-noise ratio, but not linearity

- Ex.: 12-bit converter with oversampling needs component accuracy to match better than 16-bit accuracy if a 16-bit linear converter is desired

- Advantage of 1-bit D/A is that it is inherently linear. Two points define a straight line, so no laser trimming or calibration is required

- Many audio converters presently use 1-bit converters for realizing 16- to 18-bit linear converters (with noise shaping).

## Problems with some 1-bit converters ((?))

## Why 1-Bit Sigma-Delta Conversion is Unsuitable for High-Quality Applications

by

Stanley P. Lipshitz and John Vanderkooy Audio Research Group, University of Waterloo Waterloo, Ontario N2L 3G1, Canada

#### **ABSTRACT**

Single-stage, 1-bit sigma-delta converters are in principle imperfectible. We prove this fact. The reason, simply stated, is that, when properly dithered, they are in constant overload. Prevention of overload allows only partial dithering to be performed. The consequence is that distortion, limit cycles, instability, and noise modulation can never be totally avoided. We demonstrate these effects, and using coherent averaging techniques, are able to display the consequent profusion of nonlinear artefacts which are usually hidden in the noise floor. Recording, editing, storage, or conversion systems using single-stage, 1-bit sigma-delta modulators, are thus inimical to audio of the highest quality. In contrast, multi-bit sigma-delta converters, which output linear PCM code, are in principle infinitely perfectible. (Here, multi-bit refers to at least two bits in the converter.) They can be properly dithered so as to guarantee the absence of all distortion, limit cycles, and noise modulation. The audio industry is misguided if it adopts 1-bit sigma-delta conversion as the basis for any high-quality processing, archiving, or distribution format to replace multi-bit, linear PCM.

Audio Engineering Society

## Convention Paper 5395

Presented at the 110th Convention 2001 May 12–15 Amsterdam, The Netherlands

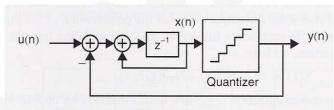

## Oversampling with noise shaping (14.2)

- Oversampling combined with noise shaping can give much more dramatic improvement in dynamic range each time the sampling frequency is doubled.

- The sigma delta modulator converts the analog signal into a noise-shaped low-resolution digital signal.

The decimator converts to a high resolution digital

signal

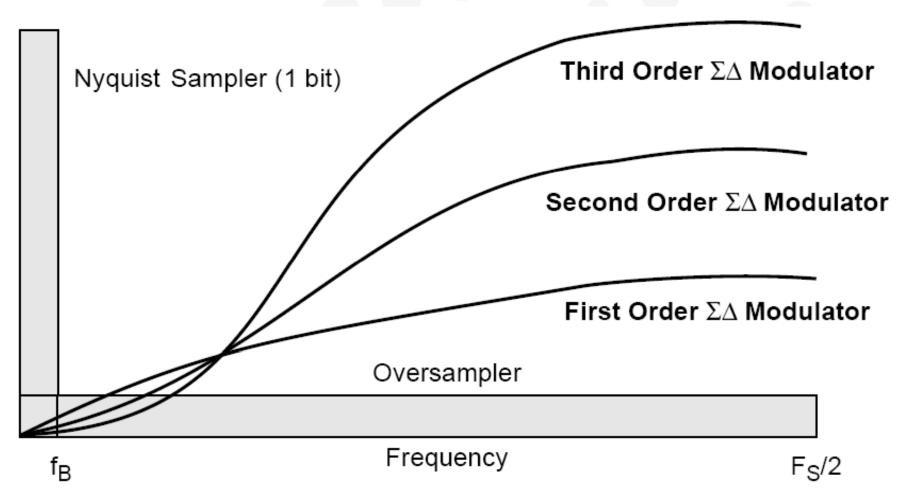

# Multi-order sigma delta noise shapers (Sangil

Park, Motorola)

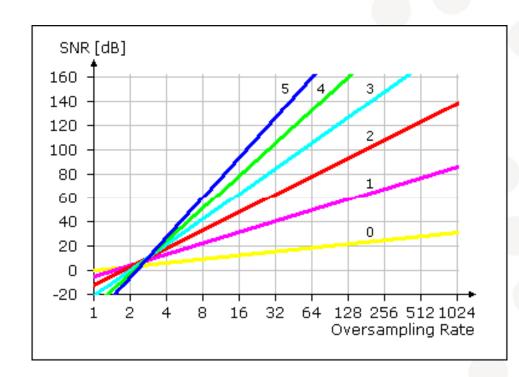

Note: Higher order Noise Shaper has less baseband noise

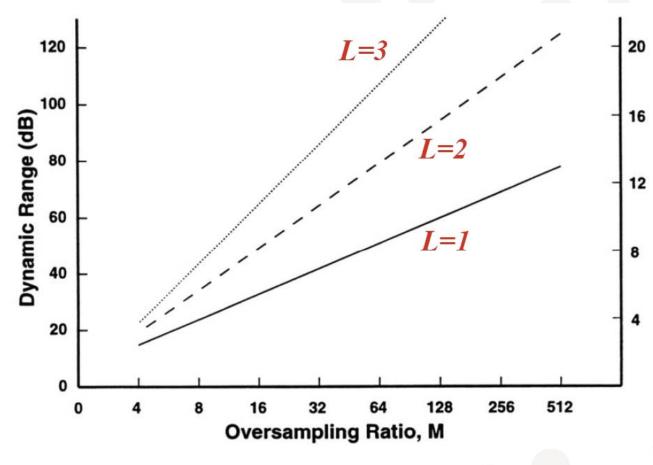

OSR, modulator order and Dynamic Range

2 X increase in  $M \rightarrow$ (6L+3)dB or (L+0.5) bit increase in Resolution (Bits) L: sigma-delta order

Oversampling and noise shaping

Given that a 1-bit A/D converter has a 6 dB SNR, which sample rate is required to obtain a 96-dB SNR (or 16 bits) if  $f_0 = 25 \text{ kHz for straight}$ oversampling as well as first-and second-order noise shaping?

- Oversampling with no noise shaping: From ex. 14.3 we know that straight oversampling requires a sampling rate of 54 THz.

- (6.02N+1.76+10 log (OSR) = 96

$$6 + 10 \log OSR = 96$$

$$<-> 10 log OSR = 90$$

$$SNR_{max} = 6.02N + 1.76 - 5.17 + 30 \log(OSR)$$

(14.26)

We see here that doubling the OSR gives an SNR improvement for a first-order modulator of 9 dB or, equivalently, a gain of 1.5 bits/octave. This result should be compared to the 0.5 bits/octave when oversampling with no noise shaping.

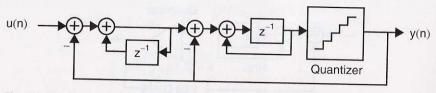

Fig. 14.7 A first-order noise-shaped interpolative modulator.

- Oversampling with 1st order noise shaping:

- $6 5.17 + 30 \log(OSR) = 96$

$$OSR = f_s / 2f_0$$

•  $30\log(OSR) = 96 - 6 + 5.17 = 95.17$

A doubling of the OSR gives an SNR improvement of 9 dB / octave for a 1st order modulator;

$$95.17 / 9 = 10.57$$

$2^{10.56} \times 2^{*}25 \text{ kHz} = 75.48 \text{ MHz}$

OR:  $log(OSR) - 95.17/30 - 3.17 \rightarrow OSR - 1509.6$

1509.6 \* (2\*25kHz) = 75.48 MHz

$$SNR_{max} = 6.02N + 1.76 - 12.9 + 50 \log(OSR)$$

(14.)

We see here that doubling the OSR improves the SNR for a second-order mod lator by 15 dB or, equivalently, a gain of 2.5 bits/octave.

The realization of the second-order modulator using switched-capacitor ter niques is straightforward and is left as an exercise for the interested reader.

Fig. 14.10 Second-order  $\Delta\Sigma$  modulator.

- Oversampling with 2nd order noise shaping:

- $\bullet$  6 12.9 + 50 log(OSR) = 96

$$OSR = fs / 2f_0$$

• 50  $\log (OSR) = 96 - 6 + 12.9 = 102.9$

A doubling of the OSR gives an SNR improvement of 15 dB / octave for a 2nd order modulator;

$$102.9 / 15 = 6.86$$

$$102.9 / 15 = 6.86$$

$2^{6.86} \times 2^*25 \text{ kHz} = 5.81 \text{ MHz}$

## Ex. 14.5 "point":

- 2 X increase in M →

(6L+3)dB or (L+0.5) bit

increase in DR.

- L: sigma-delta order

- 6 db Quantizer, for 96 dB SNR:

- Plain oversampling: f<sub>s</sub>=54

GHz

- 1st order : f<sub>s</sub>=75.48 MHz

- 2nd order:  $f_s$ = 5.81 MHz

- Exam problem (INF4420) below

3 a) (Weight 10 %)

16. mars 2010

A sampled signal is bandlimited to  $f_0 = 22$  kHz. What is the sampling frequency,  $f_s$ , for an oversampling ratio ("OSR") of 128?

A 1-bit analog-to-digital converter ("ADC") has an inherent 6-dB SNR. Which maximum SNR is acquired by combining it with strict oversampling and an OSR of 128, if no noise shaping is used? What is the maximum SNR in the similar case exploiting 2<sup>nd</sup> order noise shaping? If a 1-bit ADC using 3<sup>rd</sup> order noise shaping has a maximum SNR of 125 dB for an OSR of 128, what

If a 1-bit ADC using 3<sup>rd</sup> order noise shaping has a maximum SNR of 125 dB for an OSR of 128, what is the expected maximum SNR if the OSR is reduced to 32?

### Sigma Delta converters, ISSCC 2008

## ISSCC-Foremost global forum

"CT": continous time

#### **ΔΣ DATA CONVERTERS**

Chair: Zhongyuan Chang, IDT Technology, Shanghai, China Associate Chair: Yiannos Manoli, University of Freiburg, Freiburg, Germany

#### 27.1 A 108dB-SNR 1.1mW Oversampling DAC with a Three-Level DEM Technique 8:30 AM

K. Nguyen, A. Bandyopadhyay, B. Adams, K. Sweetland, P. Baginski Analog Devices, Wilmington, MA

A multi-bit audio DAC in a 0.18µm CMOS process uses a three-level DEM scheme and an ISI-free output stage to achieve 108dB SNR while consuming a total of 1.1mW per channel from a 1.8V supply.

#### 27.2 A 0.7V 36 $\mu$ W 85dB-DR Audio $\Delta\Sigma$ Modulator Using a Class-C Inverter

9:00 AM

Y. Chae, I. Lee, G. Han Yonsei University. Seoul. Korea

An audio  $\Delta\Sigma$  modulator is realized in a standard 0.18µm CMOS process, exploiting the possibility of substituting a class-C inverter for an OTA. The measurement results from the fabricated chip demonstrate 81dB SNDR, 84dB SNR, and 85dB DR for a 20kHz signal bandwidth. The chip consumes 36µW from a 0.7V supply.

#### 27.3 An Inverter-Based Hybrid $\Delta\Sigma$ Modulator

9:30 AM

R. Veldhoven, R. Rutten, L. Breems NXP Semiconductors, Eindhoven, Netherlands

A hybrid  $\Delta\Sigma$  modulator with 1%-order analog filter, 5b quantizer, 2%-order digital filter, 1b quantizer, and 1b DAC is presented. The active circuitry is implemented solely with inverter circuits and standard digital cells. The 65nm CMOS modulator achieves a peak SNR of 77dB in 200kHz. Power consumption is 950 $\mu$ W at 1.2V and the area is 0.03mm².

Break 10:00 AM

#### 27.4 A Noise-Coupled Time-Interleaved ΔΣ ADC with 4.2MHz BW, -98dB THD, and 79dB SNDR

10:15 AM

K. Lee<sup>1</sup>, J. Chae<sup>1</sup>, M. Aniya<sup>2</sup>, K. Hamashita<sup>2</sup>, K. Takasuka<sup>2</sup>, S. Takeuchi<sup>2</sup>, G. Temes<sup>1</sup> <sup>1</sup>Oregon State University, Corvallis, OR <sup>2</sup>Asahi Kasei, Atsugi, Japan

A two-channel time-interleaved noise-coupled  $\Delta\Sigma$  ADC is realized in 0.18 $\mu$ m CMOS technology. Time interleaving doubles the effective clock rate while noise coupling raises the effective order of the noise-shaping loops, implements dithering, and also prevents tone generation in all loops. Using a 1.5V supply, the device achieved SFDR>100dB, THD = -98dB, and an SNDR of 79dB in a 4.2MHz signal band.

### 27.5 A 28mW Spectrum-Sensing Reconfigurable 20MHz 72dB-SNR 70dB-SNDR DT $\Delta\Sigma$ ADC for 802.11n/WiMax Receivers

10:45 AM

P. Malla<sup>1,2</sup>, H. Lakdawala<sup>1</sup>, K. Kornegay<sup>3</sup>, K. Soumyanath<sup>1</sup>

<sup>1</sup>Intel, Hillsboro, OR

<sup>2</sup>Cornell University, Ithaca, NY

<sup>3</sup>Georgia Institute of Technology, Atlanta, GA

A reconfigurable MASH 2-2  $\Delta\Sigma$  ADC, fabricated in 90nm CMOS, has an OSR of 10.5 and uses a 1.2V supply. It achieves SNRs of 72, 62, 60, and 54dB with a 20MHz BW while consuming 28, 20, 15, and 12mW, respectively. The configuration and, therefore, power are determined by signal and blocker power. SNRs of 73, 77, and 78dB are achieved for BWs of 10, 5, 2.5MHz, respectively.

#### 27.6 A 100mW 10MHz-BW CT $\Delta\Sigma$ Modulator with 87dB DR and -91dBc IMD

11:15 AM

W. Yang, W. Schofield, H. Shibata, S. Korropati, A. Shaikh, N. Abaskharoun, D. Ribner Analog Devices, Wilmington, MA

A 5<sup>th</sup>-order CT  $\Delta\Sigma$  modulator with a hybrid feedback-feedforward topology and 9-level quantization is implemented in a 0.18 $\mu$ m CMOS process. When clocked at 640MHz, the modulator achieves 87dB DR, 82dB peak SNDR, and -91dBc IMD over a 10MHz BW. The modulator occupies 0.7mm² and consumes 100mW from a 1.8V supply.

#### 27.7 A 65nm CMOS CT ΔΣ Modulator with 81dB DR and 8MHz BW Auto-Tuned by Pulse Injection

11:45 AM

Y-S. Shu<sup>1</sup>, B-S. Song<sup>1</sup>, K. Bacrania<sup>2</sup>

<sup>1</sup>University of California, San Diego, CA

<sup>2</sup>Conexant Systems, Palm Bay, FL

Active filters for CT  $\Delta\Sigma$  modulators are calibrated by injecting a binary pulse dither and nulling it with an LMS algorithm. A 3<sup>rd</sup>-order 4b prototype in 65nm CMOS occupies 0.5mm<sup>2</sup> and consumes 50mW at 1.3V. At 256MS/s (OSR=16), the DR is 81dB with a 2.4V<sub>pp</sub> full-scale range. SNR and SNDR at -1dBFS are 76 and 70dB, respectively.

#### 27.8 A CT $\Delta\Sigma$ ADC for Voice Coding with 92dB DR in 45nm CMOS

12:00 PM

L. Doerrer, F. Kuttner, A. Santner, C. Kropf, T. Puaschitz, T. Hartig Infineon, Villach, Austria

A  $2^{nd}$ -order CT multi-bit (4b)  $\Delta\Sigma$  ADC for voice coding is implemented in a 45nm CMOS process. The input operational amplifier is chopped to eliminate flicker noise and offset. The quantizer, a power-efficient 3-comparator tracking ADC with a capacitive voltage reference DAC, is suitable for low-voltage designs and high clock rates. Over a bandwidth of 20kHz, the DR is 86dB. The ADC consumes 1.2mW from a 1.1V supply when clocked at 12MHz.

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and application to maintain technical currency and to network with leading experts.

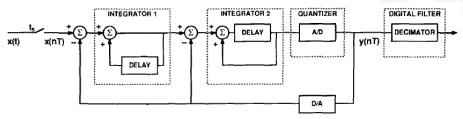

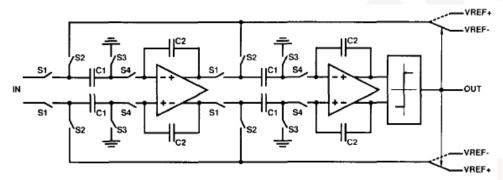

## 2nd order sigma delta modulator

Fig. 1. Block diagram of second-order  $\Sigma\Delta$  modulator with decimator.

Fig. 10. Second-order  $\Sigma\Delta$  modulator implementation.

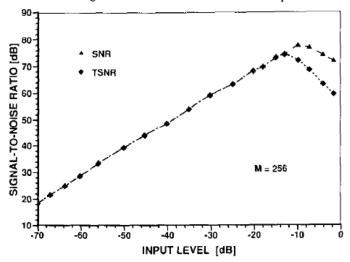

Fig. 13. Measured SNR for a sampling frequency of 4 MHz and a signal frequency of 1.02 kHz.

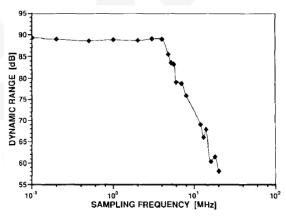

Fig. 14. Maximum operating frequency.

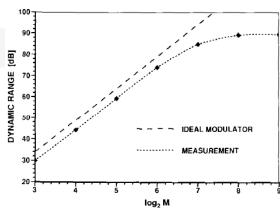

Dynamic range as a function of the oversampling ratio for a sampling frequency of 4 MHz.

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 23, NO. 6, DECEMBER 1988

### The Design of Sigma-Delta Modulation Analog-to-Digital Converters

BERNHARD E. BOSER, STUDENT MEMBER, 1EEE, AND BRUCE A. WOOLEY, FELLOW, 1EEE

## Additional litterature

- Stanley P. Lipshitz, John Vanderkooy: Why 1-bit Sigma Delta Conversion is Unsuitable for High Quality Applications, Journal of the audio engineering society, 2001.

- Y. Chiu, B. Nicolic, P. R. Gray: Scaling of Analog-to-Digital Converters into Ultra-Deep-Submicron CMOS, Proceedings of Custom Integrated Circuits Conference, 2005.

- Richard Hagelauer, Frank Oehler, Gunther Rohmer, Josef Sauerer, Dieter Seitzer: A GigaSample/Second 5-b ADC with On-Chip Track-And-Hold Based on an Industrial 1 um GaAs MESFET E/D Process, IEEE Journal of Solid-State Circuits ("JSSC"), October 1992.

- Walt Kester: Which ADC Architecture is right for your application?, Analog Dialogue, Analog Devices, 2005.

- Richard Lyons, Randy Yates: "Reducing ADC Quantization Noise", MicroWaves & RF, 2005

- Sangil Park: "Principles of sigma-delta modulators for analog to digital converters", Motorola

- B. E. Boser, B. A. Wooley: "The design of sigma delta modulation analog to digital converters, IEEE JSSC, 1988.

- John P. Bentley: Principles of Measurement Systems, 2nd ed., Bentley, 1989.

- Lecture Notes, University of California, Berkeley,

EE247 Analog Digital Interface Integrated Circuits, Fall 07;http://inst.eecs.berkeley.edu/~ee247/fa07/

# Next Time, 23/3-10:

- More from Chapter 14; Oversampling Converters (14.2, 14.3, 14.4, 14.5, 14.7)

- Beginning of chapter 16; Phase-Locked Loops (16.1)

### Guide to writing a thesis / report: The Design and implementation of a Nifty Gadget (page 1 and 2)

#### **Guide to Writing a Thesis**

Department of Applied Electronics Last updated 1997-05-12

Original manuscript written by Sven Mattisson

### The Design and Implementation of a Nifty Gadget

Tekla-Liz Book

April 32, 1992

Abstract

What is all this about?

Why should I read this thesis?

Is it any good?

What's new?

#### Preface

Have you done anything that doesn't have to do with your research? Have you published parts of this work before?

#### Acknowledgement

Who is your advisor? Did anyone help you? Who funded this work? What's the name of your favorite pet?

#### 1 Introduction

What is the use of a Nifty Gadget?

What is the problem?

How can it be solved?

What are the previous approaches?

What is your approach?

Why do it this way?

What are your results?

Why is this better?

Is this a new approach?

Why haven't anyone done it before?

http://www.tde.lth.se/cccd/education/nifty.html

or

Why do you reiterate previous work?

What is your contribution to the field of Nifty Gadgets?

#### 2 Theoretical background

What is the required background knowledge? Where can I find it?

#### 2.1 Various approaches to Nifty Gadgets

What is the relevant prior work?

Where can I find it?

Why should it be done differently?

Has anyone attempted your approach previously?

Where is that work reported?

#### 2.2 Nifty Gadgets my way

What is the outline of your way? Have you published it before?

#### 3 My implementation of a Nifty Gadget

Can you describe your implementation in detail?

Why did you use this technology?

How does the theory relate to your implementation?

What are your underlying assumptions?

What did you neglect and what simplifications have you made?

What tools and methods did you use?

Why use these tools and methods?

#### 4 Nifty Gadget results

Did you actually build it?

How can you test it?

How did you test it?

Why did you test it this way?

Are the results satisfactory?

Why should you (not) test it more?

What compensations had to be made to interpret the results?

Why did you succeed/fail?

#### 5 Discussion

Are your results satisfactory? Can they be improved? Is there a need for improvement?

### "Nifty Gadget" page 3 and 4

Are other approaches worth trying out? Will some restriction be lifted? Will you save the world with your Nifty Gadget?

#### 6 References

What is the background reading list? Where is the related work? Where is the prior work? Where can I find important material?

#### Appendix A

Can you outline fatilary calculus or whatever complicated theory or results you are using that will obscure the text?

#### Appendix B

A thesis should discuss the following topics:

#### Introduction

Presentation of the problem or phenomenon to be addressed, the situation where the problem or phenomenon occurs, and references to earlier relevant research.

#### Common errors

Problem is not properly specified or formulated; insufficient references to earlier work.

#### Purpose

What can be gained by more knowledge about the problem or phenomenon.

#### Common errors

The purpose is not mentioned, not connected to earlier research, or not in line with what the actual contents of the thesis.

#### • Problem/Hypothesis

Questions that need to be answered to reach the goal and/or hypothesis formulated be means of underlying theories.

#### Common errors

Missing problem description; deficiencies in the connections between questions; badly formulated hypothesis.

#### Method

Choice of an adequate method with respect to the purpose and problem/hypothesis.

#### Common errors

An inappropriate method is used, for example due to lack of knowledge about different methods; erroneous use of chosen method.

#### Result

Answers to the forwarded questions by means of the achieved results

#### Common errors

The results are not properly connected to the problem; blurry presentation; the results are intermixed with discussion.

#### Discussion

Discussion of the accuracy and relevance of the results; comparison with other researchers results.

#### Common errors

Too far reaching conclusions; guesswork not supported by the data; introduction of a new problem and a discussion around this.

#### Conclusion

Consequences of the achieved results, for example for new research, theory and applications.

#### Common errors

The conclusions are too far reaching with respect to the achieved results; the conclusions do not correspond with the purpose.

Home Page for the Department of Applied Electronics