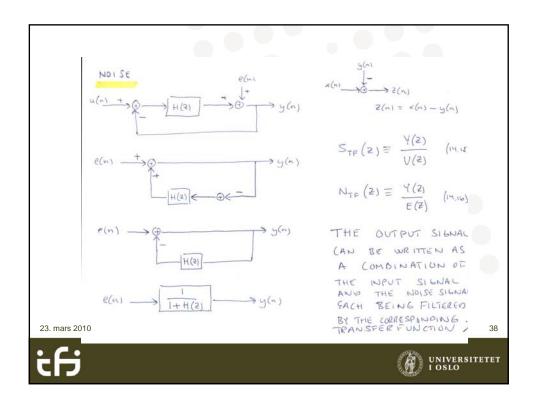

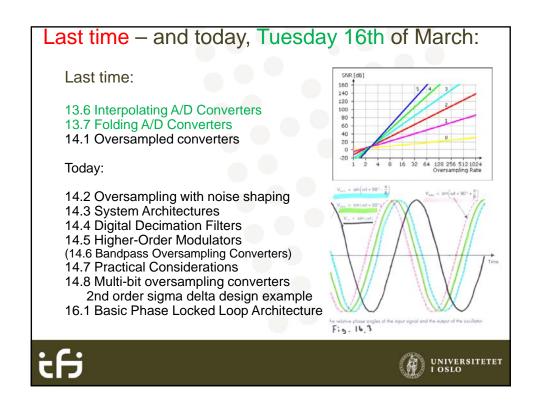

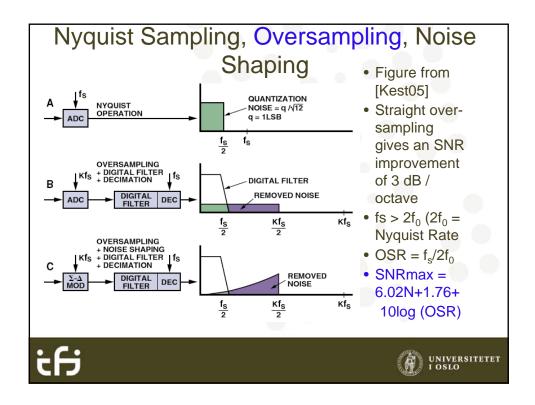

### 14.2 Oversampling with noise shaping

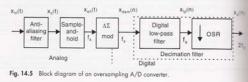

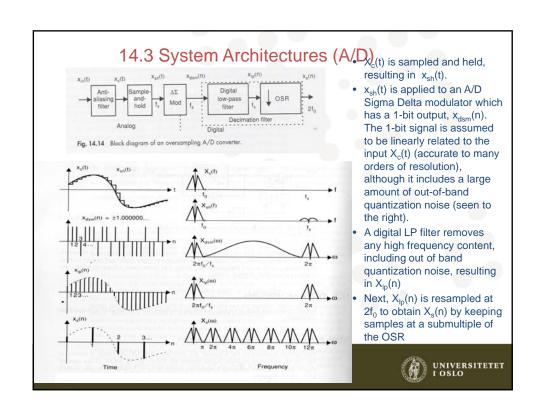

- The anti aliasing filter bandlimits the input signals less than f<sub>s</sub>/2.

- The continous time signal x<sub>c</sub>(t) is sampled by a S/H (not necessary with separate S/H in Switched Capacitor impl.)

- The Delta Sigma modulator converts the analog signal to a noise shaped low resolution digital signal

- The decimator converts the oversampled low resolution digital signal into a high resolution digital signal at a lower sampling rate usually equal to twice the desired bandwidth of the desired input signal (conceptually a low-pass filter followed by a downsampler).

14.2 Oversampling with noise shaping

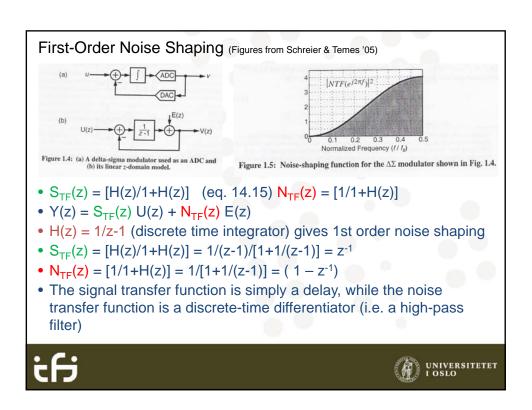

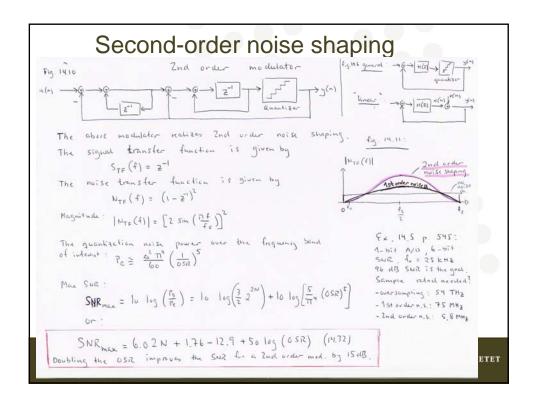

$$N_{TF}(f) = 1 - e^{-j2nf/f_{S}} = \left(e^{j\frac{nf/f_{S}}{f_{S}}} - e^{-j\frac{nf/f_{S}}{f_{S}}}\right) \cdot e^{-j\frac{nf/f_{S}}{f_{S}}} = \left(e^{j\frac{nf/f_{S}}{f_{S}}} - e^{-j\frac{nf/f_{S}}{f_{S}}}\right) \cdot e^{-j\frac{nf/f_{S}}{f_{S}}}$$

$$= Sin\left(\frac{nf}{f_{S}}\right) \cdot 2j \cdot e^{-j\frac{nf/f_{S}}{f_{S}}}$$

$$\left[N_{TF}(f)\right] = 2 Sin\left(\frac{nf}{f_{S}}\right) \cdot \left(high-pass''\right)$$

$$Quantization noise power over the frequency bend 0 to f_{e} is now given by

$$P_{e} = \int_{-f_{0}}^{\infty} 3e(f) \cdot \left|N_{TF}\right|^{2} df = \int_{-f_{0}}^{\infty} \left(\frac{\Delta^{2}}{i2}\right) \frac{1}{f_{S}} \left[2 sin\left(\frac{nf}{f_{S}}\right)^{2} df + (14.23)\right]$$

$$Meking the approximation that  $f_{e} < c f_{S} = c f_$$$$$

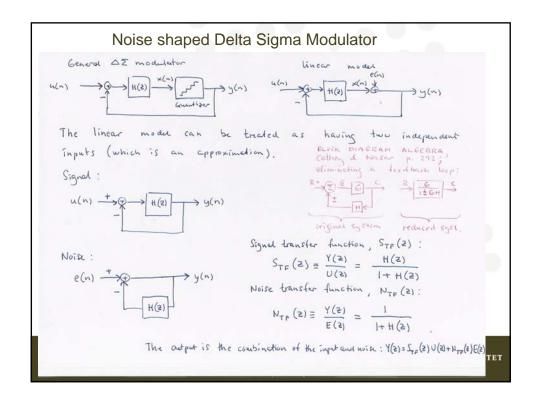

Quantization noise power for linearized model of a general

$$\Delta\Sigma$$

modulator

$$P_{e} = \int_{-f_{0}}^{f_{0}} S_{e}^{2}(f) \left| N_{TF}(f) \right|^{2} df = \int_{-f_{0}}^{f_{0}} \left( \frac{\Delta^{2}}{12} \right) \frac{1}{f_{0}} \left[ 2 \sin \left( \frac{\Pi f}{4s} \right) \right]^{2} df \quad (14.23)$$

Using the approximation that  $f_{0} < f_{0} = f_{$

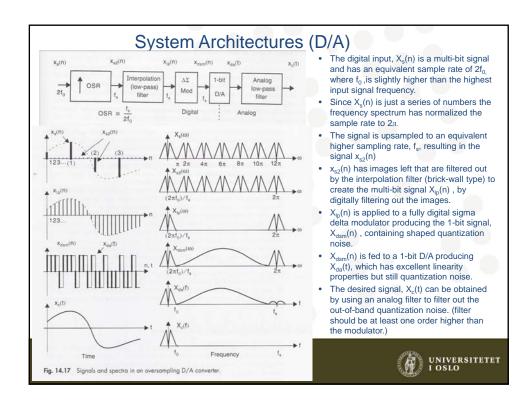

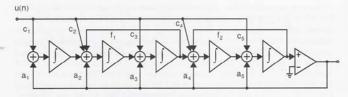

# 14.5 Higher-Order Modulators –Interpolative structure

Fig. 14.20 A block diagram of a fifth-order modulator.

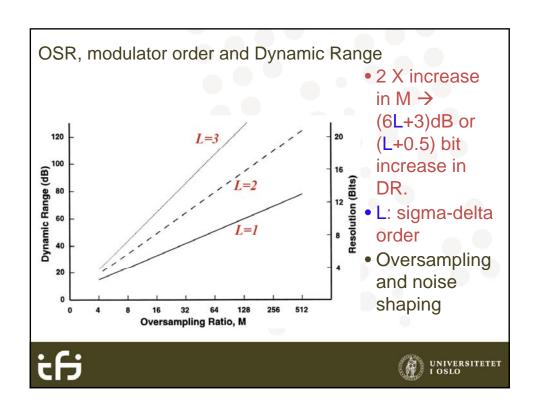

- Lth order noise shaping modulators improve SNR by 6L+3dB/octave.

- Typically a single high-order structure with feedback from the quantized signal.

- In figure 14.20 a single-bit D/A is used for feedback, providing excellent linearity.

- Unfortunately, modulators of order two or more can go unstable, especially when large input signals are present (and may not return to stability)

Guaranteed stability for an interpolative modulator is nontrivial.

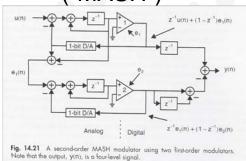

# Multi-Stage Noise Shaping architecture ("MASH")

- Overall higher order modulators are constructed using lower-order, more stable, ones → more stable overall system.

- Fig. 14.21: 2nd order using two first-order modulators.

- Higher order noise filtering can be achieved using lower-order modulators.

- Unfortunately sensitive to finite opamp gain and mismatch

# Among most relevant nonidealities: Finite DC gain Bandwidth, Slew rate Swing limitation Offset voltage Gain nonlinearity Flicker noise Sampling jitter Voltage dependent capacitors Switch on-resistance Offset voltage and settling time for comparators

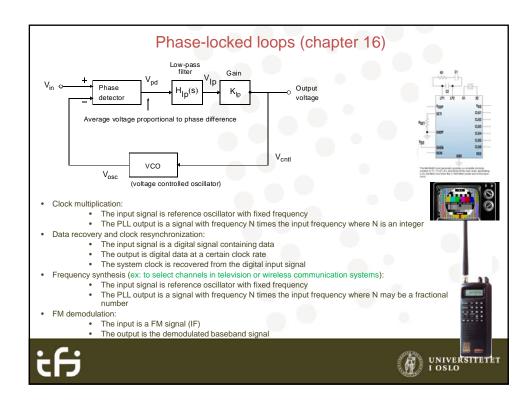

### Phase-locked loops (chapter 16)

- Phase-locked loop

- From Wikipedia, the free encyclopedia

- A phase-locked loop or phase lock loop (PLL) is a control system that generates a signal that has a fixed relation to the phase of a "reference" signal. A phase-locked loop circuit responds to both the frequency and the phase of the input signals, automatically raising or lowering the frequency of a controlled oscillator until it is matched to the reference in both frequency and phase. A phase-locked loop is an example of a control system using negative feedback.

- Phase-locked loops are widely used in <u>radio</u>, <u>telecommunications</u>, <u>computers</u> and other electronic applications. They may generate stable frequencies, recover a signal from a noisy communication channel, or distribute clock timing pulses in digital logic designs such as <u>microprocessors</u>. Since a single <u>integrated circuit</u> can provide a complete phase-locked-loop building block, the technique is widely used in modern electronic devices, with output frequencies from a fraction of a cycle per second up to many gigahertz.

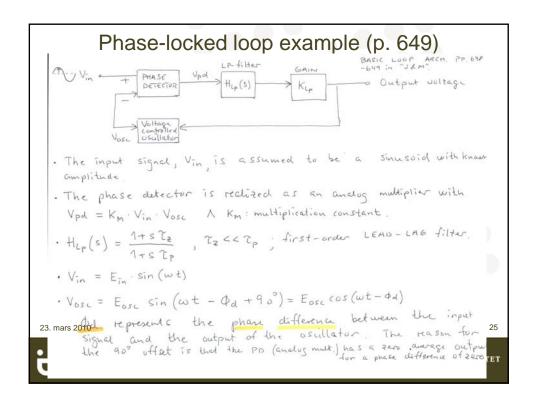

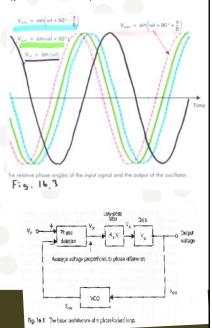

# Phase-Locked Loop, typical architecture

- The phase detector ("PD") normally has an output voltage with an average value proportional to the phase difference between the input signal and the output of the VCO ("Voltage Controlled Oscillator").

- The low-pass filter is used to extract the average value from the output of the PD.

- The average value is amplified by the Gain block and used to drive the VCO.

- The negative feedback of the loop results in the output of the VCO being <sup>23.</sup> "SYNCH ronized with the input signal.

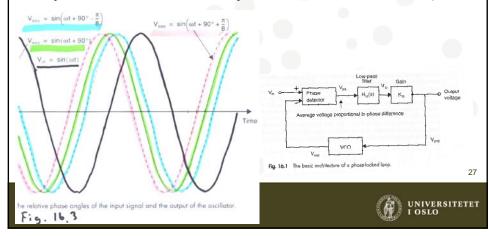

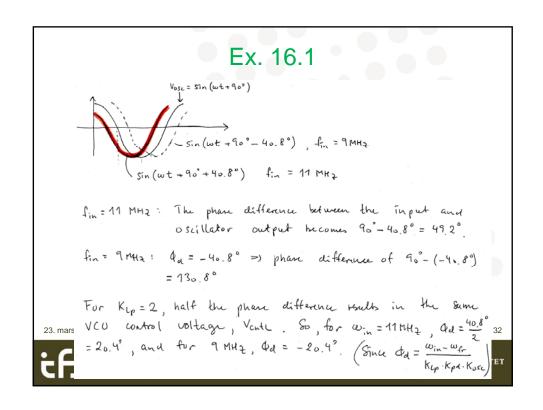

Examples of different waveforms, as a function of different  $\Phi_{d,}$  (J&M p 650-651 ,fig. 16.3)

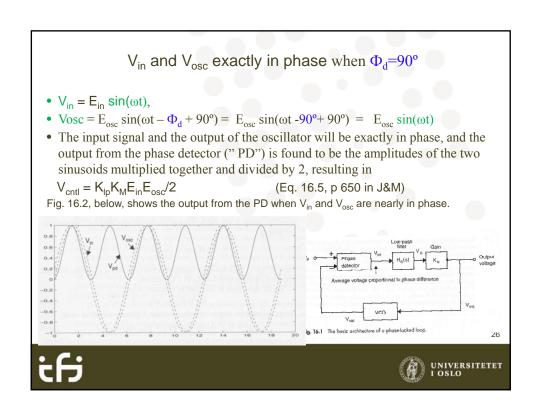

- $V_{osc} = E_{osc} sin(\omega t \Phi_d + 90^\circ) = E_{osc} cos(\omega t \Phi_d)$  (16.4)

- $\Phi_d > 0$  corresponds to waveforms that are more in phase.

- When the input signal and VCO output have a 90° phase diff. ( $\Phi_d = 0$ ), they are uncorrelated and the output of the LP-filter will be zero.)

Some relevant mathematical relationships from 16.1, pages 650-652 in "J&M"

- The output of the phase detector:

- Vpd =  $K_M V_{in} V_{osc} = K_M E_{in} E_{osc} \sin(\omega t) \cos(\omega t \Phi_d)$  (16.6)

- Using  $\sin(A)\cos(B) = (1/2)[\sin(A+B)+\sin(A-B)]$  we have  $Vpd = K_M V_{in} V_{osc}/2 [\sin(\Phi_d) + 2\sin(2\omega t - \Phi_d)]$ (16.8)

- The LP-filter removes the second term at twice the frequency of the input signal, so V<sub>entl</sub> is therefore given by

$$V_{cntl} = K_{lp}K_{M}(E_{in}E_{osc}/2)\sin(\Phi_{d})$$

(16.9)

• Since  $V_{cntl}$  is either a dc value or slowly varying, for small  $\Phi_d$  the following approximation for (16.9) may be used:

$$V_{cntl} \approx K_{lp} K_{M} (E_{in} E_{osc}/2) \Phi_{d} = K_{lp} K_{pd} \Phi_{d}$$

(16.10)

Thus, the output of the LP-filter is approximately proportional to the phase difference between the output of the oscillator and the input signal, assuming the 90 ofset bias is ignored. The approximation is used in analyzing the PLL to obtain a linear model. The constant of proportionality is called  $K_{pd}$  and is given by

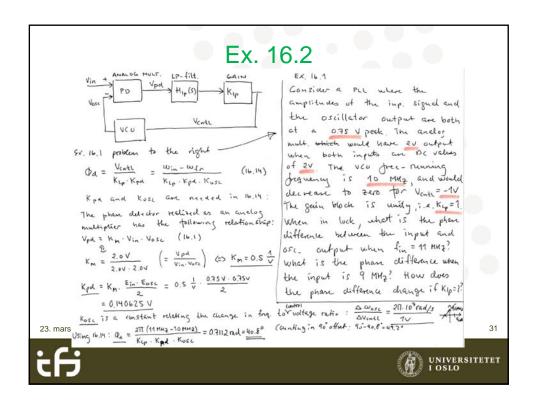

### More on PLL operation (p. 652-653)

- Assume that the VCO has a free-running frequency  $\omega_{\rm fr}$  when it's input is zero, and that the input signal is initially equal to  $\omega_{\rm fr}$ , and the system has  $\Phi_{\rm d}=0$  (in lock).

- NEXT, assume the input frequency slowly increases. Now, with  $\Phi_{\rm d} > 0$ , the two waveforms will become more in phase (See fig. 16.3). After a short time the output of the LP-filter will go positive. Since the two waveforms are at slightly different frequencies, the output of the LP-filter will slowly increase. Since the VCO frequency is proportional to  $V_{\rm cntl}$ , this increase will cause the VCO frequency to increase until it is the same of that of the input signal again, which will keep the two signals in synchronism (i.e.

locked). (The opposite would occur for a decrease in the input signal frequency.)

th

### More on PLL operation (p. 652-653)

• At a new input frequency,  $(\neq \omega_{fr})$  which does not equal the free-running frequency, we can find the new phase difference for the two locked signals by noting that the frequency of the oscillator's output signal is given by  $\omega_{rr} = K \cdot V \cdot r + \omega_{rr} \cdot (16.12)$

$\omega_{\text{osc}} = K_{\text{osc}} V_{\text{cntl}} + \omega_{\text{fr}} \qquad (16.12).$

$K_{osc}$  is a constant relating the change in frequency to control voltage ratio. The output voltage of the amplified LP-filter is now given by

$V_{cntl} = (\omega_{in}\omega_{fr})/K_{osc}$  (16.13)

where  $\omega_{in}$  is the frequency of the input signal, which is equal to the frequency of the oscillator's output. From (16.10):

$\Phi_{d} = V_{cntl}(K_{lp}K_{pd}) = (\omega_{in}-\omega_{fr})/K_{lp}K_{pd}K_{osc}$ (16.14)

23. mars 2010

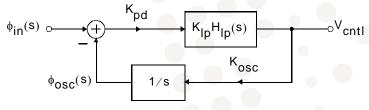

# Linear model of the PLL – when in lock

$$V_{\text{cntl}}(s) = K_{pd} K_{lp} H_{lp}(s) \left[\phi_{in}(s) - \phi_{osc}(s)\right]$$

$$\phi_{osc}(s) = \frac{K_{osc}V_{\text{cntl}}(s)}{s}$$

# PLL transfer functions

Combining equations from previous slide:

$$\frac{V_{\text{cntl}}(s)}{\phi_{in}(s)} = \frac{s K_{pd} K_{lp} H_{lp}(s)}{s + K_{pd} K_{lp} K_{\text{osc}} H_{lp}(s)}$$

- This is a highpass response from input phase to the control voltage.

- Rewriting gives:

$$\frac{\phi_{osc}(s)}{\phi_{in}(s)} = \frac{K_{pd}K_{lp}K_{osc}H_{lp}(s)}{s + K_{pd}K_{lp}K_{osc}H_{lp}(s)}$$

• This is a lowpass response from the input phase

# Additional litterature

- Walt Kester: Which ADC Architecture is right for your application?, Analog Dialogue, Analog Devices, 2005.

- Behzad Razavi: "Design of Analog CMOS Integrated Circuits", McGraw-Hill, reprint 2009.

- Jimmy J. Cathey, Syed A. Nasar: Basic Electrical Engineering, Schaum's Outlines, McGraw Hill 1997

- Richard Schreier, Gabor C. Temes: Understanding Delta-Sigma Data Converters, IEEE Press / Wiley Interscience, 2005

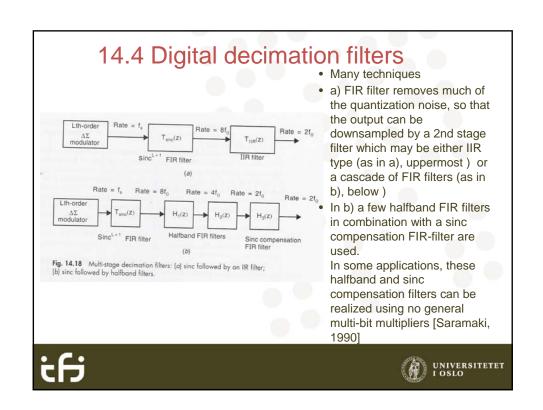

- Tapio Saramaki et. Al: Multiplier-Free Decimator Algorithms for Super-Resolution Oversampled Converters, IEEE International Symposium on Circuits and Systems, 1990.

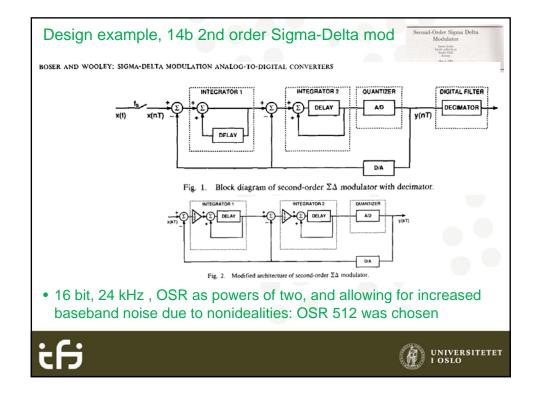

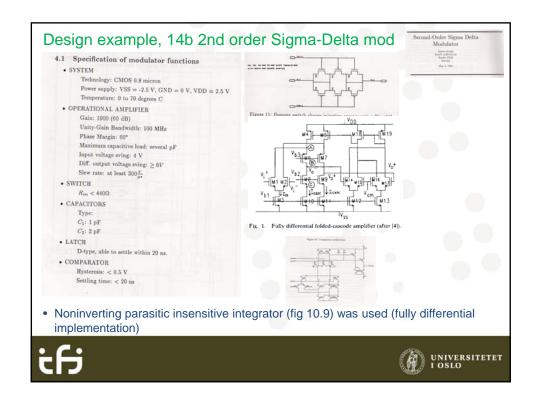

- Bernhard A. Boser, Bruce A. Wooley: The Design of Sigma-Delta Modulation Analog-to-Digital Converters, IEEE Journal of Solid-State Circuits, December 1988.

- Sudhir M. Mallya, Joseph H. Nevin: Design Procedures for a Fully Differential Folded-Cascode CMOS Operational Amplifier, IEEE Journal of Solid-State Circuits, December 1989.

- http://www.wikipedia.org (on PLLs)

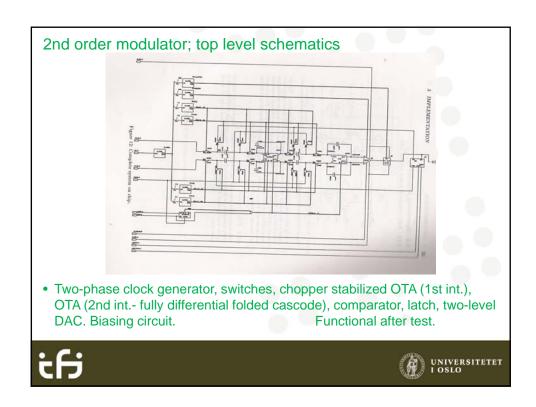

- Snorre Aunet: Second-Order Sigma Delta Modulator, Nordic VLSI, May 4, 1994.

# Next Time, 13/4-10:

- More from Chapter 16; PLLs

- About report writing

| 23.03.2010 | SA | Lille Aud. | Chapter 14;<br>Oversampling<br>Converters | preliminary <u>Slides</u> <u>Slides</u><br>two per page |

|------------|----|------------|-------------------------------------------|---------------------------------------------------------|

| 30.03.2010 |    |            |                                           | No teaching in week 13.                                 |

| 06.04.2010 |    |            |                                           | No teaching in week 14, due to Easter holidays.         |

| 13.04.2010 | SA |  |  | Later Slides.<br>per page. | Slides, two |

|------------|----|--|--|----------------------------|-------------|

|------------|----|--|--|----------------------------|-------------|