### Last time – and today, Tuesday 13th of April:

#### March the 23rd:

- 14.2 Oversampling with noise shaping

- 14.3 System Architectures

- 14.4 Digital Decimation Filters

- 14.5 Higher-Order Modulators

- (14.6 Bandpass Oversampling Converters)

- 14.7 Practical Considerations

- 14.8 Multi-bit oversampling converters

2nd order sigma delta design example

- 16.1 Basic Phase Locked Loop Architecture

### Today:

- 16.1Linearized small-signal analysis of general PLLs

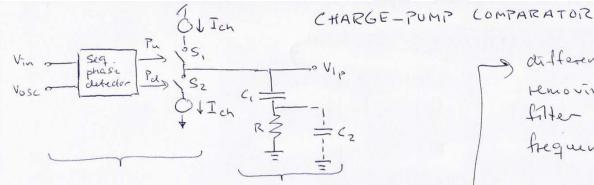

- 16.2 PLLs with charge-pump phase comparators

- 16.3 Voltage controlled oscillators

- 16.4 Computer Simulations of PLLs

About writing the report

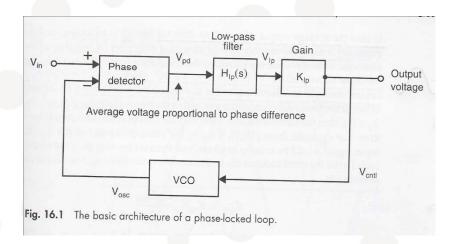

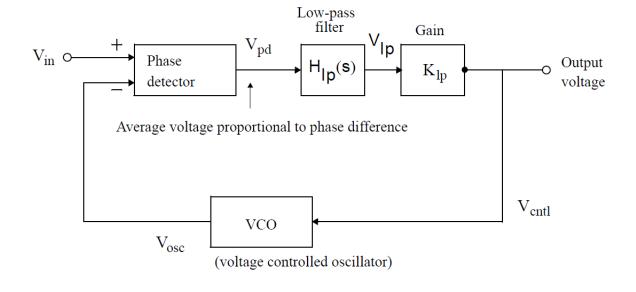

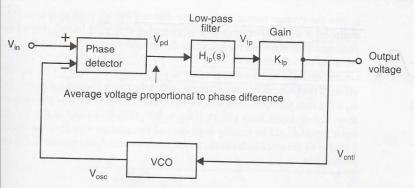

### **PLL Basic Architecture**

• In general, output may be  $V_{\text{entl}}$  or  $V_{\text{osc}}$

3 of 26

C D. Johns, K. Martin, 1997

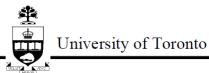

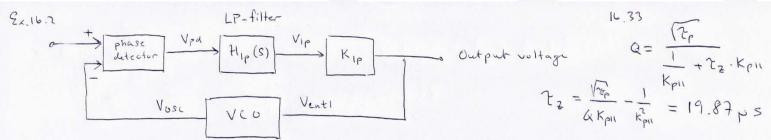

### PLL linear model applying to almost every PLL

$$V_{\text{cntl}}(s) = K_{pd} K_{lp} H_{lp}(s) [\phi_{in}(s) - \phi_{osc}(s)]$$

$$\phi_{osc}(s) = \frac{K_{osc} V_{\text{cntl}}(s)}{s}$$

$$H_{lp}(s) = \frac{1 + s\tau_z}{1 + s\tau_p}$$

• Combining above 2 equations ...

$$\frac{V_{\text{cntl}}(s)}{\phi_{in}(s)} = \frac{sK_{pd}K_{lp}H_{lp}(s)}{s + K_{pd}K_{lp}K_{\text{osc}}H_{lp}(s)}$$

- This is a highpass response from input phase to control voltage

- Can also be written as

$$\frac{\phi_{\text{osc}}(s)}{\phi_{\text{in}}(s)} = \frac{K_{\text{pd}}K_{\text{lp}}K_{\text{osc}}H_{\text{lp}}(s)}{s + K_{\text{pd}}K_{\text{lp}}K_{\text{osc}}H_{\text{lp}}(s)}$$

- This is a lowpass response from input phase to output phase

- Differences between PLLs are determined only by what is used for the LP-filter (H<sub>Ip</sub>(s)), the Phase Detector (K<sub>pd</sub>) or the oscillator (K<sub>osc</sub>).

12. april 2010

### More on the 2nd order PLL model

2nd order transfer functions are often written in the form:  $H(s) = \frac{N(s)}{D(s)}$

$$D(s) = 1 + \frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2}$$

wo : resonant frequency

Transient time for the complete loop:

12.: Q : Q-factor, damping factor

Good settling: Q = 0.5max. flat group dulay:  $Q = \frac{1}{\sqrt{3}} = 0.577$ max. flat amplitude resp:  $Q = \frac{1}{\sqrt{2}} = 0.737$

$$w_o = \frac{K_{\text{Pll}}}{\sqrt{\tau_p}} \quad (16.32)$$

Usually, when wo co wfr:

$$Q \cong \frac{1}{\omega_s \chi_z} = \frac{\sqrt{\chi_c}}{\chi_z \kappa_{pll}} \qquad (16.35)$$

When Q = 0.5:

$$\Upsilon_{z} = \frac{2\sqrt{r_{p}}}{\kappa_{pll}} = \frac{2}{\omega_{s}}.$$

### Capture range, lock range, false lock

- The maximum difference between the input signal's frequency and the oscillator's free-running frequency where lock can eventually be attained is defined as the capture range

- One lock is attained, as long as the input signal's frequency changes only slowly it will remain in lock over a range that is much larger than the capture range

- When a multiplier is used for the phase detector the loop may lock to harmonics (multiple of the frequency) of the input signal. This is called a false lock.

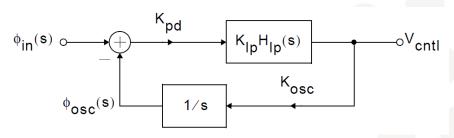

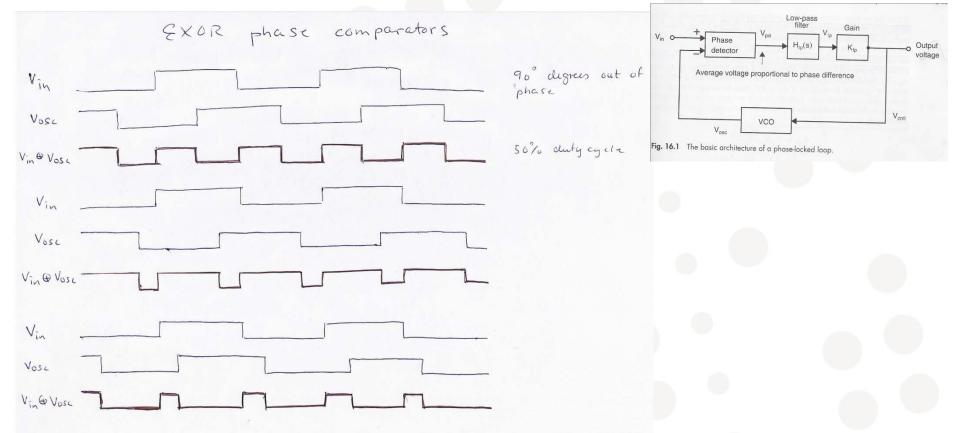

### Exclusive-OR Phase comparators

- When the waveforms are 90 degrees out of phase the output is a waveform at twice the frequency of the input signal and has a 50 percent duty cycle.

- If all waveforms are symmetric about 0 volts the average value extracted by the low-pass filter would be zero.

### **EXOR** phase comp

When the waveforms become more out of phase, the average value of the output signal is positive; whereas when they become more in phase, the average value of the output signal is negative

- · no false lock, attains lock quickly

- · Vin and Vose are exactly in phase. when the system is in lock.

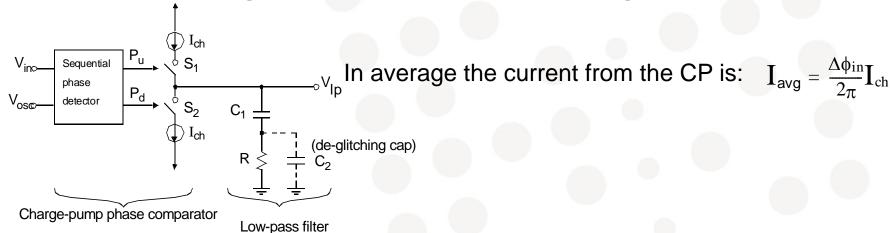

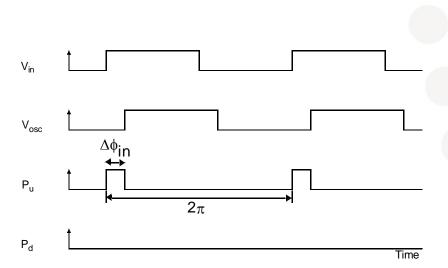

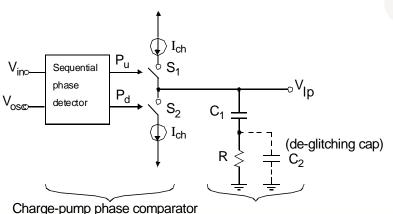

- · injects, leaves alone, or subtracts charge on the capacitor in the LP- filter, depending on Pu and Pd.

- . S, closed: Ich increases the control voltage into the VCO

- So closed: In flows out of the LP-fitter, decreasing the control voltage.

S, and Sz open: Steady State

- . Pu and Pd. are digital signals

- of IF Vingoes to 1 before Vose, then Pu will be 1 cluring the time that the signels are different. => injecting charge ELSE if Vose goes to 1 before Vin, Pa will be 1 during the time that the inputs are

so different => Sz will be closed, Hemoving charge from the loopfilter and decreasing the VCO frequency.

OBS & Notice that Pu only goes high at the leading edges and is insensitive to the falling edges.

Fig. 16.1 The basic architecture of a phase-locked loop.

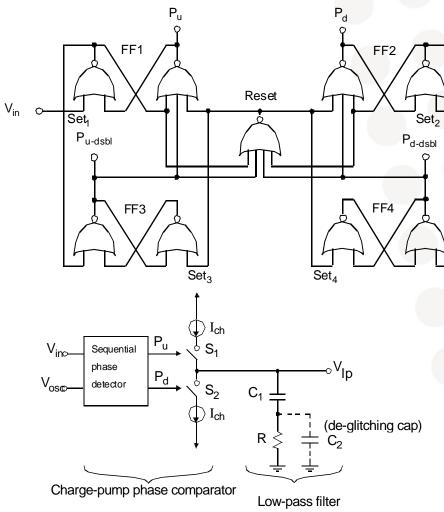

### Small-Signal Model of the Charge-Pump PLL

The transfer function from the loop filter is (C2 ignored):

$$H_{lp}(s) = \frac{V_{lp}(s)}{I_{avg}(s)} = R + \frac{1}{sC_1} = \frac{1 + sRC_1}{sC_1}$$

$$\frac{\phi_{osc}(s)}{\phi_{in}(s)} = \frac{(1 + sRC_1)}{1 + sRC_1 + \frac{s^2C_1}{K_{pd}K_{osc}}}$$

$$\omega_0 = \frac{1}{\tau_{\text{pll}}} = \sqrt{\frac{I_{\text{ch}} K_{\text{osc}}}{2\pi C_1}}$$

$$Q = \frac{1}{RC_1\omega_0} = \frac{1}{R} \sqrt{\frac{2\pi}{C_1 I_{\text{ch}} K_{\text{osc}}}}$$

### Ex. 16.4

Ex. 16.4 Kose = 211 x 50 Mrad/ Ich = 10 pA. Wfr = SOMHZ and the loop has a time constant of 100 cycles, or Zps. Vin > phase det. > Sec. I The Sign the components of the vose Pd OTen SR

$$\omega_6 = \frac{1}{2ps} = 500 \text{ krad/s}$$

$$C_{1} = \frac{\Gamma_{ch}}{2\pi} \cdot \frac{Kosc}{\omega_{o}^{2}}$$

$$= \frac{10\mu A}{2\pi} \cdot \frac{2\pi \times 50 \text{ M rad/s}}{(500 \text{ k rad/s})^{2}} = 2\pi F$$

Let

$$L_2 = \frac{C_2}{10} = 200 pF$$

Let  $Q = 0.4$

$$\alpha = \frac{1}{RC_{i}\omega_{o}} = \frac{1}{R} \sqrt{\frac{2\pi}{C_{i} \operatorname{Ich} K_{osc}}}$$

$$R = \frac{1}{G} \sqrt{\frac{2\pi}{2\pi F \cdot 10 \, \text{pA} \cdot \text{3}}} = \frac{2\pi}{2\pi K_{osc}}$$

$$R = \frac{1}{G} \sqrt{\frac{2\pi}{2\pi F \cdot 10 \, \text{pA} \cdot \text{3}}} = \frac{2\pi}{2\pi K_{osc}}$$

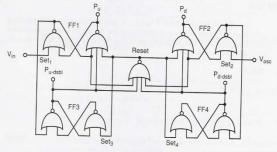

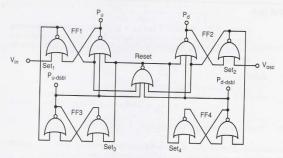

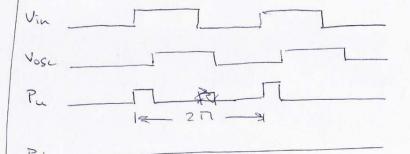

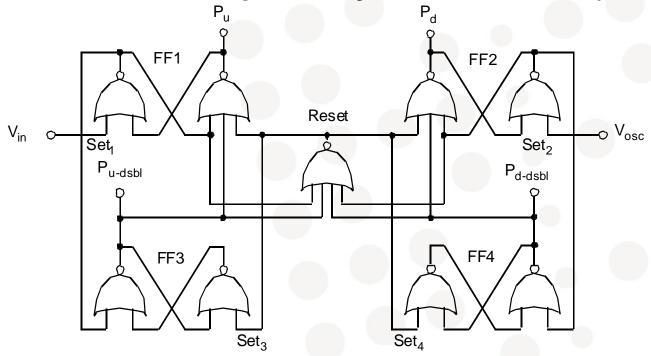

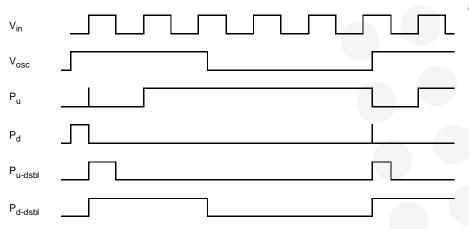

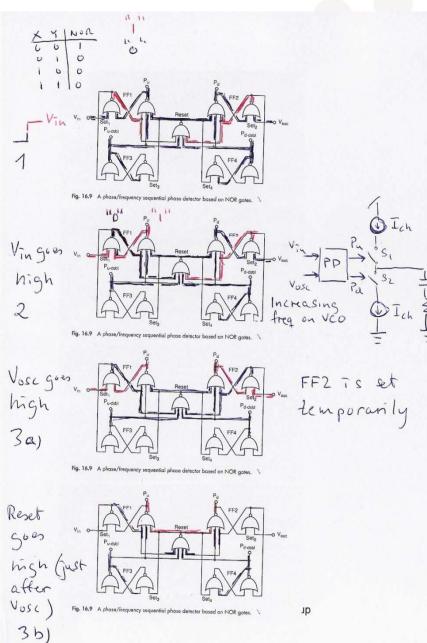

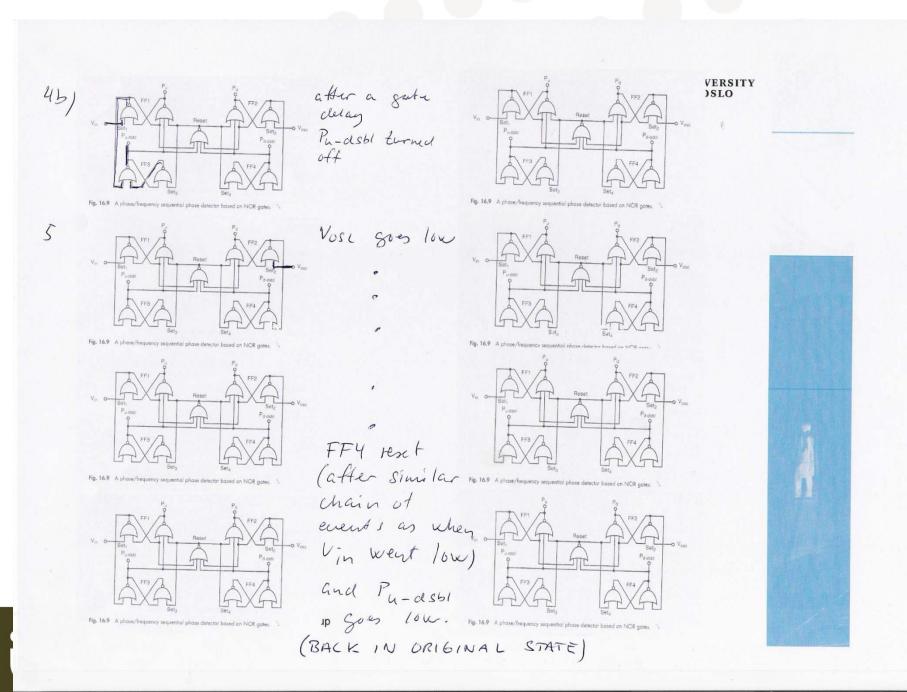

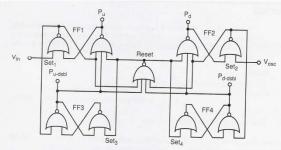

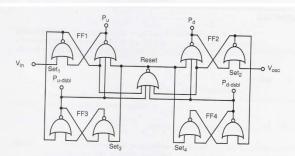

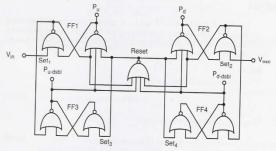

# Phase Frequency Detector (PFD)

- Most commonly used sequential phase detector is the Phase Frequency Detector (PFD).

- This circuit handles phase differences up to  $2\pi$ .

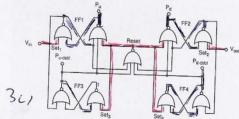

### Phase Frequency Detector (PFD)

- Assume P<sub>u</sub>, P<sub>d</sub>, P<sub>u-dsbl</sub>, P<sub>d-dsbl</sub>, Reset, V<sub>in</sub>, V<sub>osc</sub> are low

- V<sub>in</sub> goes high; FF1 set/ Pu goes high -> VCO frequency increases

- V<sub>osc</sub> goes high; FF2 set temporarily, reset goes high, causing P<sub>u</sub> and P<sub>d</sub> go low after some delay. Reset going high causes FF3 and FF4 to be set and P<sub>u-dsbl</sub> and P<sub>d-dsbl</sub> go high, which later causes reset to go low. FF1 and FF2 are kept in reset mode and P<sub>u</sub> and P<sub>d</sub> low.

- V<sub>in</sub> goes back to 0; FF3 reset and P<sub>u-dsbl</sub> is turned off.

- Similarly, when V<sub>osc</sub> goes low, FF4 is reset goes low, FF4 is reset and P<sub>d-dsbl</sub> goes low. (back to original state).

(The operation is very similar if V<sub>osc</sub> leads V<sub>in</sub>)

# PFD waveforms – when V<sub>in</sub> has a much higher frequency than Vosc

- Whenever a positive going edge of Vin occurs, Pu goes high causing the VCO frequency to increase, and stays high until both Vin and Vosc go to 1. Then reset goes high, setting both Pu-dsbl and Pd-dsbl, and causing Pu and Pd to go low. The next time Vin goes to o, FF1 is reset, which resets FF3, turning Pu-dsbl off.

- Most of the time (here) Pu is high, causing Vosc to quickly increase in frequency until lock is achieved.

- No false lock

- Only suitable for digital (non-sine) inputs

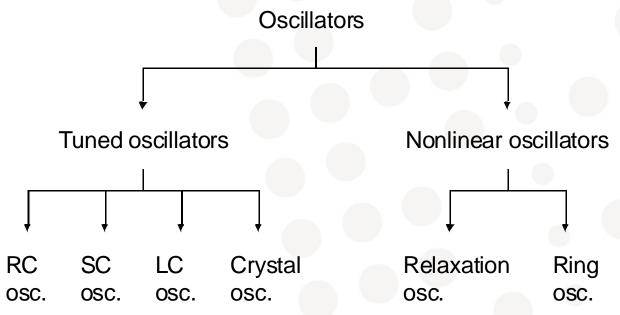

### Voltage controlled oscillators (VCO)

- Sinusoidal output oscillators usually realized some frequency selective or tuned circuit in feedback configuration, while squarewave output oscillators are usually realized using a nonlinear feedback config.

- The tuned oscillators offers better frequency stability, but limited tuning range.

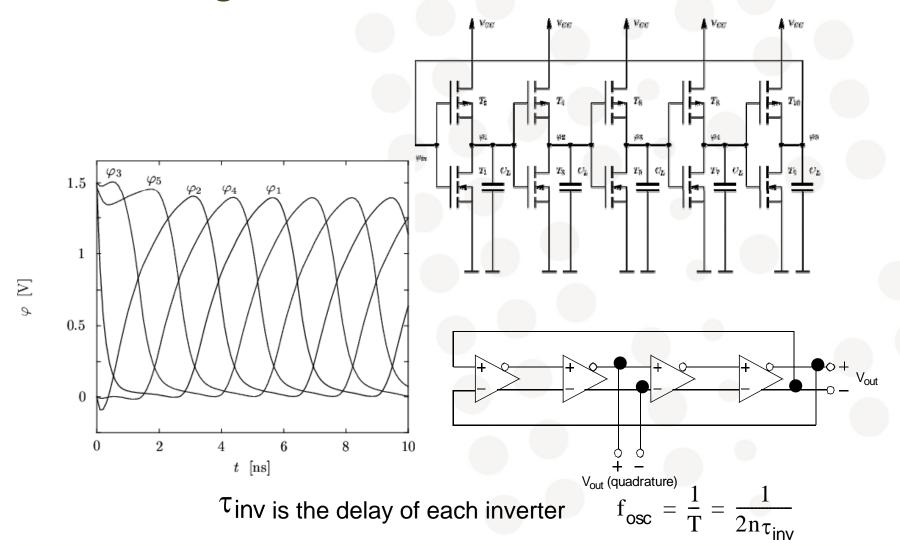

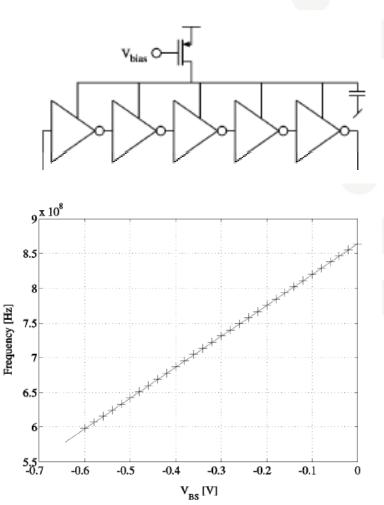

# Ring oscillators

# 0.2 V subthreshold VCO

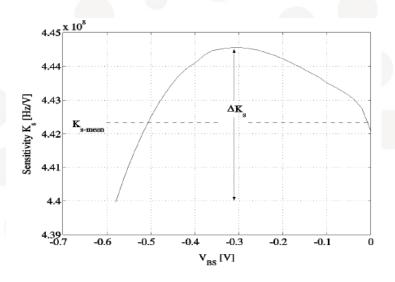

Figure 3. RVCO transfer function for a 5 stage RVCO simulated in Cadence

Figure 4. Sensitivity of the RVCO illustrates a nonlinearity of 0.5 %

#### Linearity of Bulk-Controlled Inverter Ring VCO in Weak and Strong Inversion

Ulrik Wismar\*, Dag Wisland\*\*, Pietro Andreani\*

\*Centre for Physical Electronics, Ørsted•DTU

Technical University of Denmark, DK-2800 Kgs. Lyngby, Denmark

\*\*Microelectronic Systems, Department of Informatics University of Oslo, N-0316 Oslo, Norway

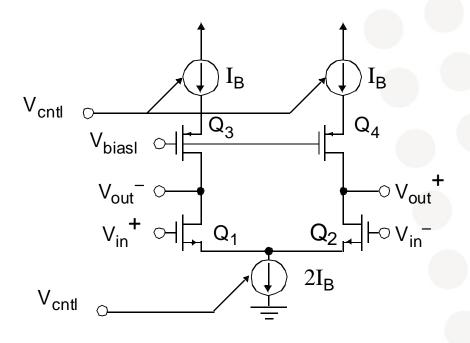

### Differential inverter

- Programmable delay

- Cascode transistors Q3,

Q4 to increase output impedance of programmable current sources for better PSRR

- I<sub>B</sub> = Kbias Vcntl (proportional)

- Tau proportional to C<sub>L</sub> / g<sub>m</sub>, f<sub>osc</sub> proportional to SQRT(V<sub>cntl</sub>); nonlinear

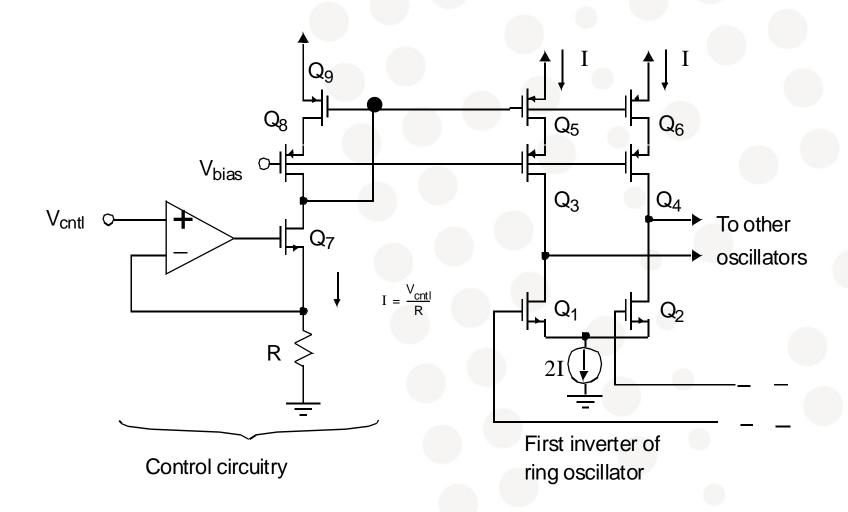

### Bias circuit

### Computer simulations of PLLs

- Nontrivial due to often very wide range of time constants present in PLLs.

- SPICE simulations only may be highly impractical and take too long time.

- Possible approach:

Simulate the individual components using SPICE over a few periods of the VCO's output waveform before simulating the complete system using simplified models where continous time components are replaced by approximately equivalent difference-equation models;

Simulink in Matlab (easy, don't need much expertise) or custom difference equations using for example C. (fast and may be modified for greater accuracy)

### Additional litterature

- Ulrik Wismar, Dag T. Wisland, Pietro Andreani: Linearity of Bulk-Controlled Inverter Ring VCO in weak and strong inversion, Proceedings of IEEE Norchip Conference, 2005.

- http://www.eecg.toronto.edu/~johns/nobots/Book/book.html

- <a href="http://www.iue.tuwien.ac.at/phd/grasser/node83.html">http://www.iue.tuwien.ac.at/phd/grasser/node83.html</a> (Ring osc.)

Remember: Grading is based on the contents of the report

### Some pointers

- http://www.idi.ntnu.no/~lasse/DM/SkriveTips.php

- Preface

- (Acknowledgement)

- 1 Introduction

- 2 Theoretical background

- (2.1 Various approaches to Nifty Gadgets)

- 2.2 Nifty Gadgets my way

- 3 My implementation of a Nifty Gadget

- 4 Nifty Gadget results5 Discussion

# Nifty Gadget / DAC chapter 3

- 3 My implementation of a Nifty Gadget

- Can you describe your implementation in detail?

Why did you use this technology?

How does the theory relate to your implementation?

- What are your underlying assumptions?

- What did you neglect and what simplifications

- have you made?

- What tools and methods did you use?

- Why use these tools and methods?

# Nifty Gadget / DAC chapter 4

- 4 Nifty Gadget results

- Did you actually build it?

How can you test it?

How did you test it?

Why did you test it this way?

Are the results satisfactory?

Why should you (not) test it more?

What compensations had to be made to interpret

the results?

Why did you succeed/fail?

# Nifty Gadget / DAC chapter 5

- 5 Discussion

- Are your results satisfactory?

Can they be improved?

Is there a need for improvement?

Are other approaches worth trying out?

Will some restriction be lifted?

Will you save the world with your Nifty Gadget?

# Guide to writing a thesis

Guide to Writing a Thesis

Page 1 of 4

Guide to Writing a Thesis

Page 2 of 4

#### Guide to Writing a Thesis

Department of Applied Electronics Last updated 1997-05-12

Original manuscript written by Sven Mattisson

#### The Design and Implementation of a Nifty Gadget

Tekla-Liz Book

April 32, 1992

Abstract

What is all this about?

Why should I read this thesis?

Is it any good?

What's new?

#### Preface

Have you done anything that doesn't have to do with your research? Have you published parts of this work before?

#### Acknowledgement

Who is your advisor?

Did anyone help you?

Who funded this work?

What's the name of your favorite pet?

#### 1 Introduction

What is the use of a Nifty Gadget? What is the problem? How can it be solved? What are the previous approaches? What is your approach? Why do it this way? Why do it this way? Why is this better? Is this a new approach? Why haven't anyone done it before? Or Why do you reiterate previous work!

#### 2 Theoretical background

What is the required background knowledge? Where can I find it?

#### 2.1 Various approaches to Nifty Gadgets

What is the relevant prior work? Where can I find it? Why should it be done differently? Has anyone attempted your approach previously? Where is that work reported?

#### 2.2 Nifty Gadgets my way

What is the outline of your way? Have you published it before?

#### 3 My implementation of a Nifty Gadget

Can you describe your implementation in detail?

Why did you use this technology?

How does the theory relate to your implementation?

What are your underlying assumptions?

What did you neglect and what simplifications have you made?

What tools and methods did you use?

Why use these tools and methods?

#### 4 Nifty Gadget results

Did you actually build it?

How can you test it?

How did you test it?

Why did you test it this way?

Are the results satisfactory?

Why should you (not) test it more?

What compensations had to be made to interpret the results?

Why did you succeed/fail?

#### 5 Discussion

Are your results satisfactory?

Can they be improved?

Is there a need for improvement?

Are other approaches worth trying out?

Will some restriction be lifted?

Will you save the world with your Nifty Gadget?

#### 6 References

What is the background reading list?

### Guide to writing a thesis

Guide to Writing a Thesis Page 3 of 4

Where is the related work? Where is the prior work? Where can I find important material?

#### Appendix A

Can you outline fatilary calculus or whatever complicated theory or results you are using that will obscure the text?

#### Appendix B

A thesis should discuss the following topics:

#### Introduction

Presentation of the problem or phenomenon to be addressed, the situation where the problem or phenomenon occurs, and references to earlier relevant research.

#### Common errors

Problem is not properly specified or formulated; insufficient references to earlier work.

#### Purpose

What can be gained by more knowledge about the problem or phenomenon.

#### Common errors

The purpose is not mentioned, not connected to earlier research, or not in line with what the actual contents of the thesis.

#### Problem/Hypothesis

Questions that need to be answered to reach the goal and/or hypothesis formulated be means of underlying theories.

#### Common errors

Missing problem description; deficiencies in the connections between questions; badly formulated hypothesis.

#### Method

Choice of an adequate method with respect to the purpose and problem/hypothesis.

#### Common error

An inappropriate method is used, for example due to lack of knowledge about different methods; erroneous use of chosen method.

#### Result

Answers to the forwarded questions by means of the achieved results.

#### Common errors

The results are not properly connected to the problem; blurry presentation; the results are inter-

Guide to Writing a Thesis

age 4 of 4

mixed with discussion.

#### Discussion

Discussion of the accuracy and relevance of the results; comparison with other researchers results

#### Common errors

Too far reaching conclusions; guesswork not supported by the data; introduction of a new problem and a discussion around this.

#### Conclusion

Consequences of the achieved results, for example for new research, theory and applications.

#### Common errors

The conclusions are too far reaching with respect to the achieved results; the conclusions do not correspond with the purpose.

Home Page for the Department of Applied Electronics

Assume (unrealistic) no celay in wires-just

A gate delay after teset goes migh, Pu and Pd go low.

3d) After another delay Pu-dsb1 and Pd-dsb1 So high

Cause Reset go low after another gate delay (guarantee Pu and

Fig. 16.9 A phase/frequency sequential phase detector based on NOR gates.

Chy Vin Soes low Some ovoice FF1 goes lo

### Ex. 16.2

Assume the same conditions as in example 16.1. Design a LP-filter for the loop so that the loop time constant is approximately 10 periods at 10 MHz  $Q = \frac{1}{2}$

Equation 16.34:

$$K_{PII} = \sqrt{K_{pd} \cdot K_{1p} \cdot K_{0SC}}$$

=  $\sqrt{0.1406 \frac{V}{pad} \cdot 1 \cdot 6.28 \cdot 10^{7} \frac{pad}{Vs}}$

=  $\sqrt{8829680 \left[\frac{1}{s}\right]} = 2972 s^{-1/2}$

Having a loop time constant of 100 periods:  $\omega_0 = \frac{1}{7} = \frac{10^7}{100} s^{-1} = \frac{10}{100} s^{-1}$   $\kappa_{\text{pii}} = \frac{1}{100} s^{-1} = \frac{1}{100} s^{-1}$

16.32:

$$w_0 = \frac{\kappa_{p11}}{\sqrt{\gamma_p}} \Leftrightarrow \gamma_p = \left(\frac{\kappa_{p11}}{w_0}\right)^2 = 0.883 \text{ ms}$$

The pole is located at

$$f_p = \frac{\omega_p}{2\pi} = \frac{1}{2\pi r_p}$$

$$= \frac{1}{2\pi \cdot 6,000883} = 180 \text{ Hz}$$

Fig. 16.9 A phase/frequency sequential phase detector based on NOD ----