# Course Script INF 5110: Compiler construction

INF5110, spring 2022

Martin Steffen

## Contents

| 10 | Code | e generation                                                                                                                    | 1  |

|----|------|---------------------------------------------------------------------------------------------------------------------------------|----|

|    | 10.1 | Introduction                                                                                                                    | 1  |

|    |      | 10.1.1 General overview and issues for code generation                                                                          | 1  |

|    |      | 10.1.2 Code generation                                                                                                          | 9  |

|    | 10.2 | 2AC and costs of instructions                                                                                                   | 11 |

|    |      | 10.2.1 Cost model                                                                                                               | 13 |

|    | 10.3 | Basic blocks and control-flow graphs                                                                                            | 18 |

|    |      | 10.3.1 From 3AC to CFG: "partitioning algorithm"                                                                                | 19 |

|    |      | 10.3.2 Levels of analysis                                                                                                       | 22 |

|    |      | 10.3.3 Loops in control-flow graphs                                                                                             | 23 |

|    |      | 10.3.4 Data flow analysis in general                                                                                            | 27 |

|    | 10.4 | Liveness analysis (general)                                                                                                     | 29 |

|    |      | 10.4.1 Definitions and uses of variables                                                                                        | 33 |

|    |      | 10.4.2 Def-use or use-def analysis $\ldots \ldots \ldots$ | 34 |

|    |      | 10.4.3 Calculation of def/uses (or liveness $\dots$ ) $\dots \dots \dots \dots \dots \dots \dots$                               | 35 |

|    | 10.5 | Local liveness: dead or alive                                                                                                   | 35 |

|    | 10.6 | Local liveness <sup>++</sup> : Dependence graph                                                                                 | 39 |

|    | 10.7 | Global analysis                                                                                                                 | 48 |

|    |      | 10.7.1 Basic blocks and live-in and live-out                                                                                    | 52 |

|    |      | 10.7.2 Block local info for global liveness/data flow analysis                                                                  | 54 |

|    |      | 10.7.3 Global DFA as iterative "completion algorithm"                                                                           | 55 |

|    |      | 10.7.4 Iterative algo                                                                                                           | 55 |

|    |      | 10.7.5 Precomputing the block-local "liveness effects"                                                                          | 57 |

|    | 10.8 | Code generation algorithm                                                                                                       | 58 |

|    |      | 10.8.1 A simple code generation algorithm                                                                                       | 61 |

## Chapter **10** Code generation

#### Learning Targets of this Chapter

- 1. 2AC

- 2. cost model

- 3. register allocation

- 4. control-flow graph

- 5. local liveness analysis (data flow analysis)

- 6. "global" liveness analysis

#### Contents

| 10.1 | Introduction                                    | 1  |

|------|-------------------------------------------------|----|

| 10.2 | 2AC and costs of instructions                   | 11 |

| 10.3 | Basic blocks and control-                       |    |

|      | flow graphs $\ldots \ldots \ldots \ldots$       | 18 |

| 10.4 | Liveness analysis (general)                     | 29 |

| 10.5 | Local liveness: dead or alive .                 | 35 |

| 10.6 | Local liveness <sup>++</sup> : Depen-           |    |

|      | dence graph $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 39 |

| 10.7 | Global analysis                                 | 48 |

| 10.8 | Code generation algorithm                       | 58 |

#### 10.1 Introduction

#### 10.1.1 General overview and issues for code generation

This chapter does the last step, the "real" code generation. Much of the material is based on the (old) dragon book [2]. There is also a new edition [1]. The book is a classic in compiler construction. The principles on which the code generation are discussed are still fine. Technically, the code generation is done for two-adddress machine code, i.e., the code generation will go **from 3AIC to 2AC**, i.e., to an architecture with 2A instruction set, instructions with a 2-address format. For *intermediate* code, the two-address format (which we did not cover), is typically not used. If one does not use a "stack-oriented" virtual machine architecture, 3AIC is more convenient, especially when it comes to analysis (on the intermediate code level).

For hardware architectures, 2AC and 3AC have different strengths and weaknesses, it's also a question of the technological state-of-the-art. There are both RISC and CISC-style designs based on 2AC as well as 3AC. Also whether the processor uses 32-bit or 64-bit instructions plays a role: 32-bit instructions may simply be too small to accomodate for 3 addresses. These questions, how to design an instruction set that fits to the current state or generation of chip or processor technology for some specific application domain

What

is it about? belongs to the field of *computer architecture*. We assume a instruction set as given, and base the code generation on a 2AC instruction set, following Aho et al. [2]. There is also a new edition of the dragon book [1], where the corresponding chapter has been "ported" to cover code generation for 3AC in the new version, vs. the 2AC generation of the older book. The principles don't change much. One core problem is register allocation, and the general issues discussed in that chapter would not change, if one would do it for a 2A instruction set.

#### **Register allocation**

Of course, details would change. The register allocation we will do is, on the one hand, actually pretty simple. Simple in the sense that the code generator does not make a huge effort of optimization. One focus will be on code generation of "straight-line intermediate code", i.e. code *inside* one node of a control-flow graph. Those code-blocks are also known as **basic blocks**. Anyway, the register allocation method walks through one basic block, keeping track on which variable and which temporary currently contains which value, resp. keeping track for values, in which variables and/or register they reside. This bookkeeping is done via so-called **register descriptors** and **address descriptors**. As said, the allocation is conceptually simple:

It focuses on not-very agressive allocation inside one basic block.

The presentation also ignores the more complex addressing modes we discussed in the previous chapter. Still, the details will look, well, already detailed and thus complicated. Those details would, obviously change, if we would use a 3AC instruction set, but the notions of address and register descriptors would remain. Also the way, the code is generated, walking through the instructions of the basic block, could remain. The way it's done is "analogous" on a very high level to what had been called *static simulation* in the previous chapter. "Mentally" the code generator goes line by line through the 3AIC, and keeps track of where is what (using address and register descriptors). That information useful to make use of register, i.e., generating instructions that, when executed, reuse registers, etc.

That also includes making "decisions" which registers to reuse. We don't go much into that one (like asking: if a register is "full", contains a variable, is it profitable to swap out the value?). By swapping, I mean, saving back the value to main memory, and loading another value to the register. If the new value is more "popular" in the future, being needed more often etc, and the old value maybe less, then it is a good idea to swap them out, in case all registers are filled already. If there is still registers free, the simple strategy will not bother to store anything back (inside one basic block), it would simply load variables to registers as long as there is still space for it.

#### Optimization (and "super-optimization"), local and global aspects

Focusing on straightline code, we are dealing with a finite problem (similar to the setting when translating p-code to 3AIC in the previous chapter), so there is no issue with nontermination and undecidability. One could try therefore to make an "absolutely optimal" translation of the 3AIC. The chapter will discuss some measures how to estimate the quality of the code in the form of a simple **cost model** in Section 10.2. One could use that cost model or other, more refined ones, to define what optimal means, and then produce optimal code for that. Optimizations that are ambitious in that way are sometimes called **super-optimization** [5] and compiler phases that do that are super-optimizers. Super-optimization may not only target register usage or cost-models like the one used here, it's a general (but slighty weird) terminology for transforming code into one which genuinely and demonstrably optimal (according to a given criterion). In general, that's of course fundamentally impossible, but for straight-line code it can be done.

The code generation here does *not* do that. Actually, super-optimization is not often attempted outside this lecture, as well. One reason should be clear: it's costly. For long pieces of staight-line code (i.e., big basic blocks) it may take too much time. There is also the effect of decreasing marginal utility. A relatively modest and simple "optimization" may lead to initially drastic improvement, compared to not doing anything at all. However, to get the last 10% of speed-up or improvement pushes up the effort disproportionally.

A related reason is: super-optimization can be achieved anyway only for parts of the code (like straightline code and basic blocks). One can push the boundaries there, as long as it remains a finite problem. For instance, allowing branching (but leaving out loops). That will make the problem more complicated and targets larger chunk of code, which drives up the effort, as well, but still remaining a finite problem. Symbolic execution is an established terminology and technique addressing also conditionals, but typically not loops. It also can be seen as some form of "static simulation".

Generally, even if we are target larger chunks of code or are more aggressive in the goals of optimization, there are boundaries of what can be done. If we stick to our setting, where we currently generate code *per basic block*, super-optimization may be costly but doable. But it would be **only locally optimal**, per *one block*. Especially when having a code, where local blocks are small, that would have the positive effect that locally superoptimized code may be done without too much effort. But what good would that do, if the non-local quality is bad? Focusing all optimization effort onto the local blocks and ignoring the global situation may be a an unbalanced use of resources. It may be better to do a decent (but not super-optimal) local optimization that, with a low-effort approach achieves already drastic improvements, and *also* invests in a simple global analysis and optimization, to also reap there low-effort but good initial gains.

That's also the route the lecture takes: now we are doing a simple register allocation, without much optimization or strategy to find the best register usage (and we discuss also one global aspect of program, across the boundaries of one elementary block. That global aspect will be **live variable analysis**. It willwill come later (in Section 10.7), because first we discuss local live variable analysis which is used for the local code generation. We can remark already here, that live variable analysis can be done locally and globally; the generation just uses live variable information for its task, whether that information is local or global. So the code generation is, in that way, *independent* form whether one invests on local or on global live variable analysis. It's just produces better code, i.e., makes better use of registers, when being based on better information (like using live variable information coming from a global live variable analysis). Indeed, the code generation

would produce semantically *correct* code, without *any* live variable analysis! In that way, the analysis and the code generation are separate problems (but not independent, as the register allocation in the code generation makes use of the information from live variable analysis).

Concerning the 'd'egree of locality" of the code generation. The algorithm later will work super-locally, insofar that it generates 2AC and makes decisions on registers line by line: every line of 3AIC is translated onto 2 (or sometimes one) line of 2AC. There is no attempt afterwards to go through the 2AC again, getting some more global perspective and them optimize it further, for instance rearranging the lines, or obtaining a register usage better that the one that had been arranged for by the line-by-line code generation. The code generation steps through the 3AC line-by-line but is not completely local, it does some book-keeping about registers used, i.e., allocated in the past. And, not to forget, the code generator has access to liveness information, which is information about the *future* use of registers. In the previous chapter, the **macro expansion** was really line-by-line local, where 3AIC was translated to 1AIC (i.e., p-code): each 3AIC line was expanded into some lines of p-case in a completely "context-free" manner, focusing on each individual, line independent from in which context the line is used. That simplistic expansion ignored the *past*, i.e., what happened before, and it ignored the future, i.e., what will happen afterwards. The code generation here takes care for both aspects, in a simple manner.

What has happened in the past is kept tracked by the **register and address descriptors.** Aspects of the future are taken care of by the **liveness** analysis.

Depending on whether one does as block-local liveness analysis or a global analysis just changed how "far into the future" the analysis looks. As far as the past in concerned: that one is (in our presentation) just block-local. The book-keeping with the register and address descriptor starts fresh with each block, there is here *no* memory of what potentially had happened in some earlier block.

#### Live variable analysis

Now, what is live variable analysis anyway, if we mention it here already, and what role does it play here?

Being alive means a simple thing for a variable: it means the variable "will" be used in the future. One could dually also say, a variable is dead, if that is not the case.

Only that one normally talks about variables being live, not so much about their death. "Death analysis" would not sound appealing.... At any rate, it's important information, especially for register allocation: if it so happens that the value of a variable is stored in a register and if one figures additionally out, that the variable is dead (i.e., not used in the future), the register may be used otherwise. What that involves, we elaborate on further below, in first approximation we can think that the register is simply "free" and can just be used when needed otherwise. Now, the "definition" for a variable of being live is a bit *unprecise*, and we wrote that the variable "will be used in the future" using quotation marks around "will". What's the problem? The problem is that the future may be unknown, and in general it's impossible to know the exact future. There can be different reasons for that. One is, depending how which language one targets for the analysis, fundamental principles like undecidablity may prevent the future behavior from exactly be known. There can be actually another reason, namely if one analyzes not a global program but only a fragment (maybe one basic block, one loop body, one procedure body). That means, the program fragment being analyzed is "open" insofar its behavior may depend on data coming from outside. In particular, the program fragment's behavior depends on that outside data or "input", when conditionals or conditional jumps are used. Even if the possible input is finite, maybe just a single bit, i.e., a single input of "boolean type", that may influence the behavior. One behavior where, at a given point a variable will be used, and another behavior, where that variable will not be used. In one future behavior, the variable is live, in the other future, it is dead. Without knowing whether the input is true of false, one cannot say that the variable "will" be used or not, it simply depends. This obstacle is a different one than the principle undecidability of general programs, which applies to *closed* programs already. For finite possible inputs (and without loops) the problem is still finite: an analysis can just "statically simulate" all runs one by one for each input, and for each individual behavior it is exactly known at each point, whether a variable will be used or not, assuming that the program is deterministic. But overall, without the input known, the program behavior is unknown.

Coming back to the "definition" of liveness. The long discussion hopefully clarified, that in a general setting, when analyzing a (piece of a) program it cannot be about whether a variable *will* be used. The question is whether the variable *may* be used.

We want to use the liveness information in particular to see if one can consider a register as free again. If there *exists a possible future* where the variable **may** be used, then the code generator cannot risk reusing the register.

That means, the notion of (static) liveness is a question of a condition that "may-inthe-future" apply. There are other interesting conditions of that sort. Some would be characterized by "must" instead of "may". And some may refer to the past, not the future. That would lead to the area of **data-flow analysis** (or more ambitiously, abstract interpretation). We won't go deep there, we stick to live-variable analysis (for the purpose of code generation). However, if one understands live variable analysis, especially the *global* live variable analysis covered later, one has understood core principles of many other flavors of data flow analysis (may or must, forward or backward).

Talking about conditions applying to the "past", perhaps we should defuse a possible misconception. Liveness of a variable refers to the future, and we said, there are reasons why one cannot know the future. Everyone knows, it's hard to do predictions, in particular those concerning the future ... So one may come to believe that analyzing the past would not face the same problems. When running a (closed) program that may be true: we cannot know the future, but we can record the past ("logging"), so the past is known. But here we are still inside the compiler, doing *static* analysis and we may deal with *open* program fragments. For concretness sake, let's use some particular question for illustration:

"undefined variables" (or nil-pointer analysis). That refers to some condition in the past, at some point, a variable is not initialized, perhaps containing a nil-pointer, and the reason is that there was not point in the past run where the variable were initialized. Statically, a compiler warning about "uninitalized variables" typically means, the variable is potentially uninitalized ("may"), namely there may *exist* a run, where there is no initialization of a variable. Or dually, a variable is properly initialized at some point, when *for all* pasts that lead to that point the variable has been initialized. But for open programs (and/or working with abstractions), there may statically be more than one possible past and we cannot be sure which one will concretely be taken. Maybe indeed all or some of them will be taken at run time, when the code fragment being under scrutiny is executed more than once. That is the case when the analyzed code is part of a loop, or correspond to a function body called variously with different arguments. In summary, the discinction between "may" and "must" applies also to statically analysizing properties concerning the past.

#### Reusing and "freeing" a register

We said that the liveness status of a variable is very important for register usage. That's understable: a variable being dead does not need to occupy precious register space, and the register can be "freed". We promised in the previous paragaph that we would elaborate on that a bit, as it involves some fine points that we will see in the algo later, which may not be immediately obvious from reading the code.

First of all, as far as the hardware platform is concerned, there is no such thing as a full, non-free or empty or free register. A register is just some fast and small piece of specific memory in hardware in some physical state, which corresponds to a bit pattern or binary representation. The latter one is a simplification or abstraction, insofar the registers may be in some "intermediate, instable" state in (very short) periods of time between "ticks" of the hardware clock. So, the binary illusion is an abstraction maintained typically with the help of a clock, and compilers rely on that: registers contain bit strings or words consisting of bits. But it's not the case that 0000 "means" empty, for course. But when is a register empty then? As said, as far as the hardware is concered, the hardware executes for instance the 2AC we are now about to generate, fullness and emptyness of registers simply does not exists. It only consists conceptually inside the compiler and code generator, which has to keep track of the status and "picturing" registers as full and empty. If the code generator wants to reuse a register (in that it generates a command that loads the relevant piece of data into the chosen register) the generator prefers to use an "empty" one, for instance one that so far has not been used at all. Initially, it will rate all registers as empty (though certainly some bit pattern is contained in them in electric form, so to say). Now in case a register contains the value for a variable, but the variable is known to be dead, doesn't that qualify for the register being free? So isn't it as easy as the following?

A register is free if it contains dead data (or "no data" insfoar as the register has not been used before)?

Sure enough, that's indeed also why liveness analysis is so crucial for register allocation. However, one has to keep in mind another aspect. Just because the value of a register is connected to a variable that is dead does not mean one can "forget" about it and, by reusing the register, overwrite it. So, why not, isn't that the definition of being dead? In a way, yes. But there are two aspects of why that's not enough. One is, that the content of a variable is kept in two copies, one in main memory and one in the register. And it may well be the case that the one in main memory "is out of sync". After all, the code generator loaded the variable to register to do faster manipulations on the "variable", therefore it is a good sign, so to say, that it's out of sync. Keeping main memory and registers always 100% in sync is meaningless; then we would be better off without registers at all. Still, if the variable is really dead, what does this inconsistency matter? That's the second point we need to consider: the concrete code generator later will make a "local" life analysis, only. So it can only knows what's going on locally and whether in the current block the variable is life or dead (respectively, all variables are "assumed" to be live at the end of a block). That's different from temporaries, that are assumed to be dead at the end of the block. That means, "one" has to store the value back to main memory. Actually, "one" needs to store that value back, if "one" suspects the values disagrees, if there is an inconsistency between them. Who is the "one" that needs to store them value back? Of course that's the code generator, that has to generate, in case of need, a corresponding store command, and it has to consult the register and address descriptors to make the right decision. After "synchronizing" the register with the main memory, the register can be considered as "free".

#### Local liveness analysis here

That was a slightly panoramic view about topics we will touch upon in this chapter, but really only slightly panoramic, since register allocation in general is a complex and much addressed problem. But the chapter will be more focused and concrete: code generation from 3AIC to 2AC, making use of liveness analysis which is mainly done *locally, per basic block.* We so far discussed live variable analysis and problems broader than we actually need for what is called *local* analysis here (local in the sense per basic block local). For basic blocks, which is straight-line code, there is neither looping (via jumps) nor is there branching (which would lead to "don't-know" non-determinism in the way described). That's the reason why techniques similar to what has been earlier called "static simulation" will be used. The live variable analyzer steps through the code line by line, and that may be called simulation (the terms simulation or static simulation are, however, not too widely used in that context).

There are two aspects worth noting in that context. One is, when talking about "simulation" it's not that the analysis procedure does *exactly* what the program will do. Since we are doing local analysis of only a *fragement* of a program, a basic block, we don't know the concrete values, that's not easily done (one could do it symbolically, though). But we don't need to pre-calculate the outcome, as we are not interested in what the program exactly does, we are interested in one particular aspect of the program, namely the question of the liveness-status of variables. In other words, we can get away with by working with an *abstraction* of the actual program behavior. In the setting here, for local liveness, even given the fact that the basic block is "open", that allows *exact* analysis, in particular we know exactly whether the variable *is* live or *is not*. So the "may" aspect we discussed above is irrelevant, locally. The fact that we don't use the exact values of the variables (coming potentially from "outside" the basic block under consideration) does not influence the question of liveness, it's independent from concrete values. If we would have conditionals, that would change, because values would influence the control-flow. So, in that way it's not a "static simulation" of actual behavior, it's more simulation stepping through the progam but working with an abstract representation of the involved data. As said, the concrete values can be abstracted away, in this case without loosing precision.

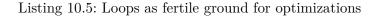

There is a second aspect we would like to mention in connection with calling the analysis some form of "static simulation". Actually, the live analysis that comes before the code generation, steps through the program in a **backward** manner. In that sense, the term "simulation" may be dubious (actually, the term static simulation is not widely used anyway, as mentioned earlier). But actually, in a more general setting of general data flow analysis, there are many useful backward analyses (live variable analysis being one prominent example) as well as many useful forward analyses (undefined variable analysis would be one).

Therefore, in our setting of code generation: the code generation will "step" though the 3AIC in a *forward* manner, generating 2AIC, keeping track of book-keeping information known as register descriptors and address destriptors. In that process, the code generation makes use of information whether a variable *is* locally live or *is not* locally live (or on whether a variable *may* be globally live or not when having global liveness info at hand). That means, prior to the code generation, there is a liveness analysis phase, which works *backwardly*.

**Side remark 10.1.1** (Exactness of local liveness analysis (some finer points)). To avoid saying something incorrect when interpreted literally, let's qualify the claim from above that stipulated: for straight-line 3AIC, *exact* liveness calculation is possible (and that what we will do). That's pretty close to the truth...

However, we look at the code generation ignoring **complicating factors**, like more complex addressing modes, and "pointers". We stated above: liveness status of a variable does not depend on the actual value in the variable, and that's the reason why exact calculation can be done. Unfortunately, in the presence of pointers, aliasing enter the picture, and the actual content of the pointer variable plays a role. Similar complications for other more complex addressing modes. We don't cover those complications though. We focus on the most basic 3AIC instructions, but when dealing with a more advanced addressing modes (as done in realistic settings), the exact future liveness status would be known, not even for straight-line code. [2] covers also that, but it's left-out from the slides and the pensum.

There is another fine point. The assumption that in straight-line code, we know what each line is executed **exactly once** is actually not true! In case our instruction set would contain operations like division, there may be division-by-zero exceptions raised by the (floating point) hardware. Similarly, there may be overflows or underflows by other hardware-triggered errors. Whether or not such an exception occurs **depends** on the concete data. So, it's not strictly true that we know whether a variable **is live or is not**. It may be, that an exception derails the control flow, and, from the point of the exception, the code execution in that block stops (something else may continue to happen, but at least not in this block). One may say: well, if such a low-level error occurs, probably trashing the program, who cares if the live variable analysis was not predicting the exact future 100%?

That's a standpoint, but a better one is: the analysis actually did not do anything incorrect. The liveness analysis is a "may" analysis, and that even applies to straight-line code. The analysis says a variable in that block may be used in the future, but in the unlikely event of some intervening catastrophe, it actually may not be used. And that's fine: considering a variable live, when in fact it turns out not to be the case

```

means to err on the safe side.

```

Inacceptable would would be the opposite case: an exception would trick the code generator to rate variables as dead, when, in an exception, they are not. But fortunately that's not the case, so all is fine.  $\hfill\square$

#### 10.1.2 Code generation

In this section we work with 2AC as machine code (as from the older, classical "dragon book"). An alternative would be 3AC also on code level (not just for intermediate code); details would change, but the principles could be comparable. Note: the message of the chapter is *not*: in the last translation and code generation step, one has to find a way to translate 3-address code two 2-address code. If one assumed machine code in a 3-address format, code generation would face similar problems. The core of the code generation is the (here rather simple) treatment of *registers*. The code generation and register allocation presented here is rather straightforward; it may look "detailed" and "complicated", but it's not very complex in that the optimization puts very much computational effort into the code generation. One optimization done is is based on liveness analysis. An occurrence of a variable is "dead", if the variable will not be read in the future (unless it's first overwritten). The opposite concept is that the occurrence of a variable is live. It should be obvious that this is essential for making good decisions for register allocation. The general problem there is: we have typically less registers than variables and temps. So the compiler must make a selection: which data should be in a register and which not not?

A scheme like "the first variables in, say, alphabetical order, should be in registers as long as there is space, the others not" is not worth being called optimization... Firstcome-first-serve like "if I need a variable, I load it to a registers, if there is still some free, otherwise not" is not much better. Basically, what is missing is taking into account information when a variable is no longer used (when no longer live), thereby figuring out, at which point a register can be considered *free again*. Note that we are not talking about run-time, we are talking about code generation, i.e., compile time. The code generator must generate instructions that loads variables to registers it has figured out to be free (again). The code generator therefore needs to keep track over the free and occupied registers; more precisely, it needs to keep track of which variable is contained in which register, resp. which register contains which variable. Actually, in the code generation later, it can even happen that one register contains the values of *more* than one variable (in case two variables at some point are know to contain the same value). Based on such a book-keeping the code generation must also make decisions like the following: if a value needs to be read from main memory and is intended to be in a register but all of them are full, which register should be "purged". As far as the last question is concerned, the lecture will not drill deep. We will concentrate on liveness analysis and we will do that in two stages: a block-local one and a global one in a later section. the local one concentrates on one basic block, i.e., one block of straight-line code. That makes the code generation kind of like what had been called "static simulation" before. In particular, the liveness information is *precise* (inside the block): the code generator knows at each point which variables are live (i.e., will be used in the rest of the block) and which not (but remember the remarks at the beginning of the chapter, spelling out in which way that this may not be a 100% true statement). When going to a *global* liveness analysis, that precision is no longer doable, and one goes for an approximative approach. The treatment there is *typical* for data flow analysis. There are *many* data flow analyses, for different purposes, but we only have a look at liveness analysis with the purpose of optimizing register allocation.

The **goals** of code generation is to produce **efficient** code. Small code size is also desirable, but less important. But first of all, the most important goal is, of course **correct** code!

When not said otherwise: efficiency refers in the following to efficiency (or quality) of the *generated* code. Fastness of compilation, or with a limited memory footprint may be important, as well (likewise may the code size of the compiler itself be an issue, as opposed to the size of the generated code). Obviously, there are trade-offs to be made. But note: even if we compile *for* a memory-restricted platform, it does not mean that we have to compile *on* that platform and therefore need a "small" compiler. One can, of course, do cross-compilation.

Correctness this is non-negotiable and a "binary" goal, the code generation is either correct or is not. Of course, compilers are complex, and bugs exists (and if found hopefully repaired) but no self-respecting compiler writer would describe a compiler with a some known cases where the generated code does something erroneous as one that offers an "almost correct" compilation. Optimization is different, it's an important goal, and correct compilers can be more or less optimial. Often there are also *conflicting* goals. We also mentions that optimization can be (and is) done in different stages of a compiler (and in different ways). But later stages, like code generation: *prime arena* for achieving *efficiency*. As also mention earlier, **optimal code** undecidable anyhow, and even if desidable (perhaps restricting oneself for straighline code, it may be *untractable*)<sup>1</sup>.

Besides that, one should also not forget that there are trade-offs, one has to agree on a measure of how "good" the procuded code is. Later we will introduce a (simple) *cost-model* for that. Even if one agrees on a measure, the word optimization is not meant as producing an *optimal* piece of code in the conventional sense of being optimial. Its interpreted as techniques to achieve "good code" (without hope for *optimal* code).

<sup>&</sup>lt;sup>1</sup>The word "untractable" refers to computational complexity; untractable are those for which there is no *efficient* algorithm to solve them. Tractable refers conventionally to *polynomial time* efficiency. Note that it does not say how "bad" the polynomial is, so being tractable in that sense still might not mean practically useful. For non-tractable problems, it's often guaranteed that they don't scale.

Due to the importance of optimization at code generation time, often time to bring out the "heavy artillery". So far, all techniques (parsing, lexing, even sometimes type checking) are computationally "easy" or made easy. Sure, one could invest in a parser that is computationally not easy, like defining a syntax that is ambiguous and handle that with a parser not only with unbounded look-ahead, but even using back-tracking. But what for? But at the later stages like code generation and optimization, even taking the platform into accound: that's the time when and *investment* in aggressive, computationally complex and advanced techniques may be worth it. And indeed many **many** different techniques are being used.

Concerning type checking, the situation is a bit different from parsing. Type checking (in particular in the way we presented it) can be simple. But that's not always the case. Type inference, aka type reconstruction, is typically computationally heavy, at least in the worst case and in languages not too simple. There are indeed technically advanced type systems around (including undecidable ones, like the one for C++...). Nonetheless, it's often a valuable goal not to spend too much time in type checking and furthermore, as far as later optimization is concerned one could give the user the option how much time he is willing to invest and consequently, how agressive the optimization is done. For our coverage of type systems in the lecture and the oblig: that one is rather simple and elementary, and poses no problems wrt. efficiency.

### 10.2 2AC and costs of instructions

Here we look at the instruction set of the 2AC and a cost model for it. Well, actually only a *small subset* of an instruction set. In particular, we look at it from the perspective of a *cost model*. Later, we want to at least get a feeling that the code we are generating is "good" but then we need a feeling what the cost is of the generated code, i.e., the cost of instructions.

#### Two-address code

When talking about 2AC, it's actually not a concrete instruction set of a concrete platform. Concrete chips have complicated inststruction sets, so it's more that we focus on a (very small) subset of what could be an instruction set of a 2A platform. Now, isn't that another "intermediate code"? We will see that the code now (independent from the fact that its 2AC) is more low-level than before. In that way, it could be a real instruction set of some hardware. The intermediate code from before could not. One could tell the same story we are doing here, translating from 3AIC to 2AC also by doing a translation from 3AIC to 3AC. Still that would pose equivalent problems (register allocation, cost model, etc.), but the presentation here happens to make use of a 2AC.

The not too many op-code we cover are "typical" **two-address op-codes**, but not a instruction set of a *concrete* machine, it's one illustrative choice.

The **2-address instructions format** looks as follows

OP source dest

(10.1)

What is called *dest* for destation here, it's not just the destination for a binary instruction, it's *also* a source for binary operations. The format describes the most general form of instruction (and that's what we will focus on), but also instructions with less arguments may be supported. Also instructions, where the *dest* is really just the destination, not *also* as source, an in the general case. Note the *order* of arguments here (esp. for minus). It order is not really per se important, nor is it a law of nature that the *src* must be mentioned first. But to be able to read later code snippet of generated code and to understand the code generator, one has to keep that order in mind.

As said, it's not the number of allowed arguments which is the crucial difference between 3AIC and 2AC, and reducing 3 arguments into to is not the crucial challenge for this chapter. The important difference is that

restrictions on source and target

- register or memory cell

- source: can additionally be a constant

```

ADD a b // b := b + a

SUB a b // b := b - a

MUL a b // b := b * a

GOTO i // unconditional jump

```

• further opcodes for conditional jumps, procedure calls ....

**Remark 10.2.1** (3A machine code). Following the presentation from [2], we base the presentation on 2AIC. Note, machine code is **not** lower-level or closer to HW because it has one argument less than 3AIC. Note, in the corresponding chapter, the new Dragon book [1] uses **3-address-machine code**, where the first edition [2] used 2AC.

Instead of the instruction format from equation 10.1, 3AC instructions could look as follows:

OP source1 source2 dest

(10.2)

That resembles 3AIC instruction. The fact that the corresponding command would have been written like dest = source1 OP source2 is more a syntactic issue or an issue of readability. Of course, being basically at HW level now, the *actual* format of instructions is no longer a syntactical issue, it has become a "*physical*" issue. Instructions a sequence of words, loaded by the processor on the chip over some bus, the single bits traveling as electrons over parallel lines of conductivity, so the format of the instruction (10.2) also reflects the design of the underlying hardware. And that will load the bits for the operator OP **first** etc, so the sequence of words in the format also reflects the way the bits are arranged in memory and the order in which they are handled by the hardware. See also Figure 10.1 for our 2AC.

Of course, if one programs in assembler code, the assembler editor may hide this and arrange the display for the programmer in a visually different way (perhaps using infix). At any rate, the order of how the individual instructions are written "notationally" is also not the main distinguishing point between intermediate code and actual code.

But what's then in general the *difference* of typical 2 (or 3) address machine code to 3A *intermediate* code? Apart from a more restricted instruction set, the main restriction is often a **restriction** of the **operands**. Hardware may for instance impose one or more of the following restrictions.

- only one of the arguments is allowed to be a memory access

- no *fancy addressing* modes (indirect, indexed ... see later) for memory cells, only for registers.

- not "too much" memory-register traffic back and forth per machine instruction.

For instance

$$\& \mathbf{x} = \& \mathbf{y} + \mathbf{z}$$

may be 3A-intermediate code, but not 3A-machine code. Perhaps the machine code can do things corresponding to  $\star z$  only on registers and cannot have two operations like & in one instructions.

As we said, the code generation could analogously be done for 3AC instead of 2AC. But what's the difference then between 3AIC and 3AC, would the translation not be trivial? Not quite, there is a gap between intermediate code and code using the instruction set. The most important difference is the use of registers. Related to that, 3AC instructions typically impose restrictions on the operands of the instructions. In the purest form, one may allow instructions only of the form r1 := r2 + r3 (here addition as an example), where all arguments, sources and target, must all be in registers. That would result in a pure load-store architecture: before doing any operation at all, the code generator must issue appropriate load-commands, and the result needs to be stored back explicitly. That obviously leads at least to longer machine code, measured in number of instructions (but perhaps the instructions themselvelse may be represented shorter). Analogous restrictions may concern the indirect addressing modes. Instruction sets with a load-store design are often used in RISC architectures.

#### 10.2.1 Cost model

To speak about optimization, we need some well-fined measure of the quality of the produced code. That's the cost model. We are interested here in the execution time. The cost model reflects the fact that not all instructions take the same time. It's a quite rough model, it's also not concerned with actually execution time. It's just an rough estimation capturing the fact that some instruction takes more time than others. There is another reason why such a cost model cannot be exact. That's because there are factors outside the code generators control, for instance the effect of *caching*. As for **cost-factors**. One is the "**size**" of the instruction, which is the base cost. On top of that comes the influence of different **address modes** as *additional costs* (see later). I.e. there are differrent (additional) costs for register access vs. main memory access vs. constants. Or also direct vs. indirect vs indexed access,

How does the size of the instruction influences the time? It's here not about code size, but one need to keep in mind: Instructions need to be **loaded** into the processo. I.e., longer instructions may need longer, perhaps it takes 2 or more machine cycles to load needed information into the processor.

The cost model (like the one here) is intended to model relevant aspects of the code, that influence the efficiency, in a proper and useful manner. The goal is not a 100% realistic representation of the timings of the processor. It will be based on assigning rule-of-thumb numerical costs to different instructions. Actually, the cost model captures not much more than the following very simple and obvious fact:

Accessing a register is "very much" faster than accessing main memory.

But the model does not use realistic figures (maybe by consulting the specs of the machine or doing measurements). Indeed, "main memory" access may not have a uniform access cost (in terms of access time). There are factors outside the control of the code generation, which have to do with the memory hierarchy. The code is generated as if there are only two levels: registers and main memory. But, of course, that's not realistic: there is caching (actually a whole hierarchy of caches may be used). Furthermore, data may even be stored in the background memory, being swapped in and out under the control of an operating system. Being not under the control of the code generator, those are stochastic influences. The compiler is not completely helpless facing caches and other memory hierarchy effects. Based on assumptions how caching and paging typically works, the code generator could try to generate code that has good characteristics concerning "locality" of data. Locality means that in general it's a good idea to store data items "than belong together" in close vicinity, and not sprinkle them randomly across the address space (whatever "belonging together" means). That's because the designer of the code generator knows that this suites chaching or swapping algorithms, that perhaps swap out cache lines, banks of adjacent addresses, whole memory pages etc. As far as caches is concerned, that's simply a rational hardware design. But one can also turn the argument around: hardware designers know, that it's "natural" that data structures coming from a high-level data structure of a structured programming language (and which contain conceptually data "that belongs together) will be generated in a way being "localized". Even if the compiler writer has never thought of efficiency and memory hierarchies, it's simply natural to place different fields of a record side by side. Also for more complex, dynamic data structures, such principles are often observed: the nodes of a tree are all placed into the same area and not randomly. More tricky maybe the the presence of a garbage collector, that could mess that up, if done mindlessness. But also the garbage collector can maken an effort to preserve locality. So, in a way, it all hangs together: well-designed memory placement will be rewarded by standard ways managing the memory hierarchy, and well-designed memory management will run standard memory layout by compilers faster. It's almost a situation of co-evolution.

But all that is more a topic for how the compiler arranges memory (beyond the general principles we discussed in connection with memory layout and the run-time environments). Here we are looking more focused on the code generation and trying to attribute a round-about costs **on individual instructions** (so questions of locality cannot be considered, as they are about the global arrangement, neither are questions of caching, etc., as one individual instruction and the instruction set is not aware of caching, let alone the influence of the operating system.

So, how can we express the very rough above observation "registers are very much fast than memory accesses"? That's easy, register access costs "nothing", it will have a zero costs. Main memory accesses will have cost of 1. Mathematically it means, memory access is infinitely most costly than registers, but as said, it's a model that may be use to generate efficient code, not as a realistic prediction of actual running time in the physical world. Also, the cost of 0 vs. the cost of 1, it's about time *additional* to the load and execution time to the operation. So doing ADD r1 r2, and addition involving 2 registers, is not infinitely fast, it costs 1 (say, one load cycle), only the register accesses don't add to the costs, their access and carrying out the addition are done within one single load cycle. Even if we had realistic figures from somewhere (via profiling and measuring average execution times under typical conditions or similar), the use would be limited: as stressed a few times, genuine and absolute optimal performance is (and cannot be) the goal (super-optimization aside). The goal is getting good or excellent performance with a decent amount of effort. We are content to use the cost model as a rough guideline (for the code generator) on decisions like

when translating one line of 3AIC, shall I use a register right now or rather not?

We will see that this is the way the code generator will work. One might not even call it "optimization", at least not in the sense the first some code is generated which afterwards is improved (optimized). The code generator takes the cost model into account on-thefly, while spitting out the code. In all trueness, it does not even consult the cost model (by invoking a function, comparing different alternatives for the next lines, and then choosing the best). It simply compiles line after line, and the decisions are plausible, and one convince oneself of the plausibility by looking at the cost model. Actually, one can convince oneself of the plausibility even without looking at the cost model, just knowing that registers should be preferred when possible. And that simple fact is one of two important pieces of common knowledge the cost model captures.

What's the second piece then? The other piece is that executing one command costs also something. So, each "line" costs 1. In that sense, the 0-costs of register access is realistic, insofar registers access is typically done in one processor cycle, i.e., in the same time slice than the loading and executing the instruction as a whole. So, in that sense, register accesses really don't cost anything additional. Other accesses incur additional costs, and since we don't aim at absolute realism, all the non-register accesses costs 1.

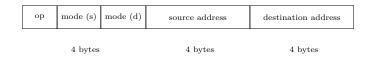

After all that background information, let's get more concrete. Figure 10.1 describes the **instruction format** in terms of bytes and their layout

- indirect: useful for elements in "records" with known off-set

- indexed: useful for slots in arrays

Figure 10.1: Instruction format

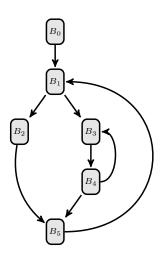

| mode              | abbr.            | address           | added cost |                 |

|-------------------|------------------|-------------------|------------|-----------------|

| absolute          | Μ                | М                 | 1          |                 |

| register          | $\mathbf{R}$     | $\mathbf{R}$      | 0          |                 |

| indexed           | c(R)             | c + cont(R)       | 1          |                 |

| indirect register | $^{*}\mathrm{R}$ | cont(R)           | 0          |                 |

| indirect indexed  | *c(R)            | cont(c + cont(R)) | 1          |                 |

| literal           | #M               | the value $M$     | 1          | only for source |

|                   |                  |                   |            |                 |

In the most general case, for our 2AC and for instructions with 2 arguments, an instruction is split into 3 parts each 4 bytes or 4 octets long. 4 bytes are also called one **word** in that architecture. The first word represents the op-code including information how to interpret the following two words, namely the source and the destination address; as mentioned, the destination address is also the address of a source, in a binary operation. The content of the source and destination arguments can be interpreted differently, that called their **mode** in the corresponding op-code. The mode of the two instruction arguments can be specified independently and the various modes are summarized in Table 10.1 (in the right-hand column).

We see that there are no real restictions when and when not memory access are allowed and when registers. Earlier we mentioned something like "load-store" architectures, where binary operations may only work on registers, or other restrictions. That is not the case here.

**Remark 10.2.2** (Instruction format, HW architecture and comparison to byte code formats). The format here corresponds to a 32-bit architecture, which is a popular format (actually, it's pretty old, there had been 32-bit machines early on, likewise also 64-bit (not micro-processors at that time). There are 16-bit microprocessors (in the past), and there are 64-bit processors as well. Of course, having 4 bytes for the op-code does not mean all codes are actually used for actual instructions (that would be way too many). But we have to keep in mind (or at least in the back of our mind, as that's no longer the concern of a compiler writer): the instructions need to be handled by the given hardware with a given size of the "bus", there is no longer the freedom and flexibility of software. In particular, it's not "byte code" (more like 4-bytes code...) And actually, it's nice to think of a binary code as to represent "addition" or "jump", but the 0 and 1's in the code actually are connected to hardware, the slots in the 32-bit word are "wired up" connecting them to logical gates that open and close and trigger other bits/electrons to flow from here to there that ultimatly result in another bit pattern that can be interpreted as that an addition has happened (on our level of abstraction). So the actual bit-codes for the logical machine instructions are are "sparcely" distributed, and some bit-pattern are not simply unused ("undefined") but would open and close the "logic gates" of the chip in a weird, meaningless manner. As said, all that is not the concern of a compiler writer, who can see an add-code as addition, but it's interesting that the story does not end there, there are complex layers of abstraction below that and also, that we are leaving the world of "anything goes" of software: the compiler writer can design any form of intermediate representations in intermediate codes and translate between them etc. But below that, things get more restricted by the physics and the laws of nature.

We can also compare that to **byte codes**, for instance the one for the mandatory assignment. Byte codes are called like that because the first part of an instruction, the opcode, is byte-size. Unlike the instruction set here, where the opcode part 4 bytes. But otherwise, the byte code from the mandatory assignments resembles the instruction set here to some extent. The byte code is, on the one hand, a p-code-style instruction set that works with a stack; that's of course not the case here. Hovever, the byte code operations sometimes also expect (additional) arguments which are not on the stack but kept in follow-up data. The size of the data there it is not 4 bytes, but the size of a *short* (a short or short integer is typically 2 bytes, also for the mandatory assignment). Another difference is, of course, the byte code is intermediate code, the 2AC represents actual instructions. That's also the reason why the instructions here take 4 bytes to represent the opcodes, as explained above.

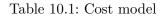

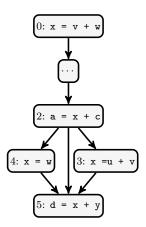

*Example* 10.2.3 (Cost model example a := b + c). The following examples are not breathtakingly interesting. They show different possible translations and their costs. The first two Listings 10.1 and 10.2 show two equivalent ways of translating the given assignment, one operating directly on the main memory, one partly loading the arguments to a register and then using that. Both versions have the same cost, in our cost model (despite the fact that the first program executes 3 commands and the second only 2).

The other two examples from Listing 10.3 and 10.4 represent the same command, but under a different assumption, namely: the arguments are already loaded in some registers. In Listing 10.3 it's assumed that R0, R1, and R2 contain **addresses** for a, b, and c. In Listing 10.4 in contrast, it's R1 and R2 contain **values** for b, and c. Either way, that drives down the costs. But that should be pretty clear, that's why one has registers, after all.

We also see that it to profit from the use of registers, the code generator needs to know which variables are stored in the registers already. That will be done later by so-called *address descriptors* and *register destriptors*.

Also, especially the second example shows, that sometime the generated code is a bit strange: Since we have only 2AC, one argument is source, the other one is source *and* destination. That means, 2AC like addition "destroy" one argument. That means, in general we need to temporarily copy that argument somewhere else, otherwise it gets lost. In the second example, since a is updated anyway, the first step uses a for that temporary copy of b. That's a **general pattern** of this form of code.

## 10.3 Basic blocks and control-flow graphs

In the introductory overview of this chapter and elsewhere, we have mentioned the concepts of basic blocks and control-flow graphs already. The notion of control flow graph is used, in this lecture, at the level of IC (maybe 3AIC), resp. also machine code. The notion of CFG makes also sense on highler levels of abstractions, i.e., one can do a control-flow graph also for abstract syntax. In our setting, there would be not much difference between to control-flow graphs from intermediate code and machine code. Both representations make use of jumps and conditional jumps and labels (resp. addresses), and that determines the edges of the graph.

In this section, we work with 3AIC, generated from some AST probably with higher-level control-flow constructs like two-armed conditionals and loops. Now we "reconstruct" a more high-level representation of the code by figuring out the CFG (at that level). It is not uncommon extract a CFG first,<sup>2</sup> and *use* the CFG assisting in the (intermediate) code generation. In such a settings, the control-flow graphs are and explicit data structure, as another intermediate representation.

Anyway, the general concept of CFG works analogously at different levels, same for basic blocks, at least when working with a standard procedural language.

**Basic blocks** are largest possible sequence of straight-line code. A **control-flow graph** is basically **graph** with basic blocks as nodes and jumps, resp. conditional jumps and fall-throughs as **edges**.

The characterization of control-flow graph does not cover procedure calls. In its basic form, a control-flow graph represents the control flow of the body of *one* procedure. One basic block, corresponding to a node in the control-flow graph, is (a largest possible) sequence of instructions **jumps in or out**. It's also the elementary unit of code analysis/optimization. It's menable to analysis techniques like static simulation/symbolic evaluation and abstract interpretation<sup>3</sup>

$<sup>^{2}</sup>$ See also the exam 2016.

<sup>&</sup>lt;sup>3</sup>Those techniques can also be used across basic blocks, but then they become more costly and challenging and (more) approximative.

When saying, a CFG is "basically" a graph, we mean that, apart from some fundamentals which makes them graphs, details may vary. In particular, it may well be the case in a compiler, that cfg's are some accessible intermediate representation, i.e., a specific concrete data structure, with concrete choices for representation. For example, we present here control-flow graphs as *directed* graphs: nodes are connected to other nodes via edges (depicted as arrows), which represent potential successors in terms of the control flow of the program. Concretely, the data structure may additionally (for reasons of efficiency) also represent arrows from successor nodes to predecessor nodes, similar to the way, that linked lists may be implemented in a doubly-linked fashion. Such a representation would be useful when dealing with data flow analyses that work "backwards". As a matter of fact: the one data flow analysis we cover in this lecture (live variable analysis) is of that "backward" kind. Other bells and whistles may be part of the concrete representation, like dedicated start and end nodes. For the purpose of the lecture, when don't go into much concrete details, for us, cfg's are: nodes (corresponding to basic blocks) and edges. This general setting is the most conventional view of cfg's.

#### 10.3.1 From 3AC to CFG: "partitioning algorithm"

As said, control-flow graphs are reconstructed here from a linear representation, said 3AIC. Actually, the fact that we use 3AIC as starting point for the extraction of the graph is not really important. It would also work the same way for our p-code, or any comparable linear instruction formal. All what's needed is that the code supports jumps and conditional jumps and label, and that's characteristic from linear intermediate codes and also machine code. Actually, even if the code does not officially have labels, as for instance in plain machine code and addresses as jump targets, one can do the same with addresses instead of symbolic labels (or the graph extraction at the same time also introduces symbolc labels for the relevant adresses, which at the same time serve as name of the control flow graph.

The CFG is determined by something that is called here **partitioning algorithm**. That's a big name for something pretty simple. We have learned in the context of *minimization* of DFAs the so-called partitioning refinement approach, which is a clever thing. The partitioning here is really not fancy at all. The task is to find in the linear code largest stretches of straight-line code, which will be the nodes of the CFG. Those blockes are **demarkated by labels and gotos** (and of course the overall beginning and end of the code.) There is only one small addition to that: an unused label, i.e., a label not used as target of some jump, does not demarkate the border between to blocks, obviously. An unused label might as well be not there, anyway.

The construction is often described making use of the concept of a **leader** of a basic block. That's a fancy name for the first line of a basic block.

If the code contains a statement **GOTO** i, then line labelled i is a leader. Instruction *after* a **GOTO** or a conditional goto is a leader. And the instruction sequence from (and including) one leader to (but excluding) the next leader or to the end of code is the code of one **basic block**.

In case the labels are not "before" a line, but as pseudo instructions occupying a line themselves, the leader would be the first real instruction in the basic block. Either way, it's the same thing, pseudo instructions are not really there anyway, they as are just used to give a name to real instructions.

An example for a partitioning of a piece of code is illustrated in Listing 10.2. The red lines show the demarcations between the code of the basic blocks. The lines at the same time correspond to what we called *leaders*: the leaders are the lines *following* the the red lines and they indicate the first line of a basic block. Threre is one exception, that's the red line at the end of the program. That one, obviously, does not correspond to a leader or the beginning of some bacic block. It demarcates, however, the end of the last basic block. Note also that the line labelled  $L_2$  is *not* a leader. The reason is that in the sketched program, this label is not used as jump target, unconditional or otherwise.

Figure 10.2: Partitioning (illustration)

It may be worth thinking about what would happen if we considered  $L_2$  a header nonetheless. In that case, the basic blocks would no longer be the *largest* sequences of straight-line code not jumped into. In this example, we would end up with 6 basic blocks instead of 5.

That should, however, not affect the correctness of the generated code. As mentioned, basic blocks are the elementary level of optimizations and code generation. Cutting the basic blocks smaller than necessary will lead to smaller stretches of code targeted by local analysis. An example would be the local liveness analysis covered later. If one uses liveness analysis only on the local level, i.e., only inside basic blocks, then the smaller than necessary basic blocks would lead to a less precise analysis. Liveness analysis (like others) can be precise within basic block, but typically resorts to approximation more globally, like doing analysis for a whole control-flow graph. In Section 10.7, we will look into that kind of global analysis. But when doing only a local one, the analysis ignores what happens outside the current basic block, and thus, to play it safe and assumes variables at the end of a basic block potentially used later. It assumes a variable at the end of a block to be *live*, though a global analysis may reveal that it is not. This safe overapproximation is typical for many forms of analyses, in particular data flow analyses, but also type checking. As a consequence, unnessessarily small blocks of straight-line code lead loss of precision, an overapproximation still safe safe but needlessly approximative.

Indirectly therefore, also register allocation is affected by a too finegrained block structure. As long as the lifeness approximation is correct or safe, the register allocator will lead to correct code as well, though presumably slower code compared to more presise (but correct) liveness information.

This describes what happens to liveness analysis and register allocation if the straight-line code blocks are needlessly small, if one assumes local analysis only. The situation for other kinds of analyses would be similar.

What would happen using small straight-line blocks if one employed a global analysis? In this case, one typically would *not* loose precision. The global analysis anyway looks at the whole control-flow graph. Unlike for local liveness analysis, to stick with this form of analysis, a global analysis will not of course *assume* that a variable at the end of a basic block is live, just to be safe. It will investigate to figure out if the variable may be used in the future or if it's sure it's dead. That's what the global analysis is good for, after all.

Does it mean, if one is doing a global analysis anyway, the size of the blocks of straight-line code does not matter? In a way yes. As said, one will not loose precision by being to finegrained. In an extremal case, one could use every instruction line as one elementary block. Why would one still work with the largest possible stretches of straigh-line code, i.e., with basic blocks of the form introduced?

The reason is mostly that the global analysis can be done if not more precisely, but more efficiently. Global analysis typically involves the analysis of loops or cycles, something that, by definition, is not needed for straight-line code. The analysis of cycles in the control-flow graph entails that one does analysis steps *repeatedly* for nodes participating in a cycle. If one has a large basic block as part of a cycle, one can analyse relevant information (for instance concerning the liveness status of variables) one in summarized form. For instance, let's assume the first usage of a variable, say x in a given basic block is that it's assigned to like in a line of the form x := e, where e does not refer to x. That means, x actually is dead at the beginning of said basic block. A local analysis of the block will find that out, and one can use the information in summarizing corresponding information for the basic block for all variables. Resp. one could do that summary information for all basic block, which form the nodes of the control flow graph. What good would that do? The local analysis, needed for the summary information steps through the lines of the basic block. As we will see (resp., one single pass through the lines is enought). Actually, it should be even intuitively clear, that one pass should be enough to see locally, for each variable, if it's used or not. Anyway, the basic block, as said, may be part of a cycle in the graph, and this need repeatedly be treated. But with the summary information precomputed by local analyses, one at least need to step through the individual ones over and over again, to (re-)discover the liveness status of the involved variables, like rediscovering that x is dead at the entrance of the basic; that information is remembered in the symmatry. In this way, working with basic block may not increase precision of the analysis and thereby increase the quality of the produced code, but the analysis itself may become faster.

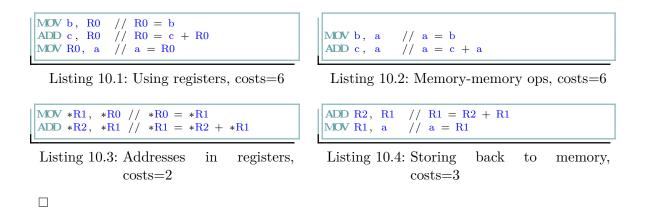

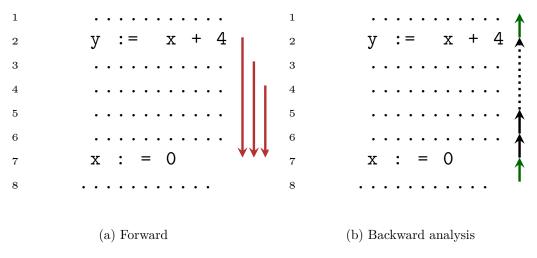

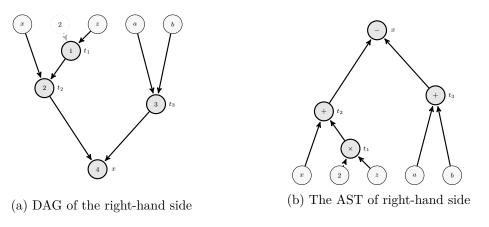

Let's have a look at some more concrete example. Listing ?? shows 3AIC for the faculty function from the previous chapter, and Figure 10.3 shows the corresponding control-flow graph. The code contains 5 basic block and thus the illustration of the control-flow graph 5 nodes. The first line in each node is the corresponding header. Unlike in the schematic example from Figure 10.2, all labels in the code are jump targets. Typically,

the (intermediate) code generator would not generate labels not being used as jump-target, though they are not "harmful"; the partitioning algo does not treat them as leaders and the label instructions from the 3AC are *pseudo-intructions*, i.e., the don't correspond ultimately lead actual machine-code instructions.

*Example* 10.3.1 (Control-flow graph of the faculty function). Let's use as example the 3AIC for the faculty function (see Listing 10.3.1). We had encountered the example already for intermediate code generation.

```

read x

t1 = x > 0

if_false t1 goto L1

fact = 1

label L2

t2 = fact * x

fact = t2

t3 = x - 1

x = t3

t4 = x == 0

if_false t4 goto L2

write fact

label L1

halt

```

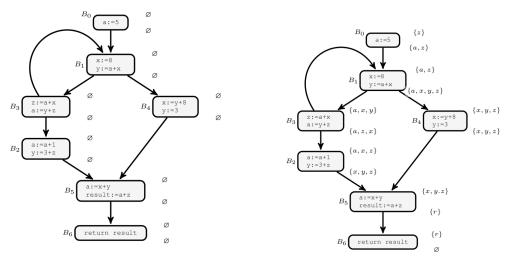

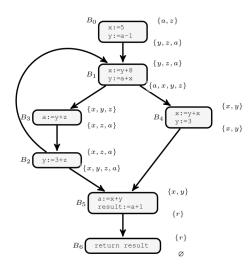

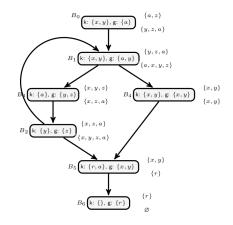

The corresponding CFG is shown in Figure 10.3.

Figure 10.3: Control-flow graph (faculty)

We see that go s and conditional go to never *inside* a block, but not every block ends in a go to or starts with a label. So it's not that labels and blocks are in exact correspondence (and in the picture, the blocks are named  $b_i$ ).

#### 10.3.2 Levels of analysis

Figure 10.3 contains the control-flow graph of the faculty procedured, resp. the graph for a main procedure of a program that realizes the faculty function. Note that the program does not do procedure calls; the faculty is calculated using a while-look in the source language and not the recursive faculty solution, one often finds. Anyway, the control-flow graph and the analysis one can do on that graph is **intra-procedural**. That refers to notions and analysis "inside" one procedure. The opposite of intra-procedural analysis is **inter-procedural**. Inter-procedural analyses and the corresponding optimizations are harder, resp. require more effort than *intra*procedural. In this lecture, we don't cover inter-procedural considerations. Except that call sequences and parameter passing has to do of course with relating different procedures and in that case deal with inter-procedural aspects. But that was in connection with the run-time environments, not what to do now in connection with analysis, register allocation, or optimization. So, in this lecture resp. this chapter, "local" refers to inside one basic block, "global" refers to across many blocks (but inside one procedure). Later, we have a short look at global liveness analysis. As mentioned, we don't cover analyses across procedures, in the terminology used here, they would be even "more global". Actually, in the more general literature, global program analysis would typically refer to analysis spanning more than one procedure. Indeed, one should avoid talking about local analysis without further qualifications; it's better to speak of block-local analysis, procedure-local, method-local, or thread-local, to make clear which level of locality is addressed. We are doing block-local analysis resp. procedure-local analysis (the latter we will also call "global").

In general, the more global, the more *costly* the analysis and especially the corresponding optimizations (if done at all).

These three levels are the conventional hierarchy of analyses. But there might be further distinctions, for example. in concurrent programs, one can distinguish between a thread-local (and inter-procedural) analysis and a global analysis, that takes multiple threads into account. Techniques to analyse programs in the presence of concurrency can become much more challenging and also, concurrency analysis requires other techniques that the notion of control-flow graphs resp. further techniques on top of that. Control-flow graph are an inherently sequential concept, capturing the structure of sequential control-constructs like conditionals and loops on the source-language levels. We don't look into analysis in the presence of parallism or concurrency.

Remark 10.3.2 (Procedure calls).

#### 10.3.3 Loops in control-flow graphs

Next we comment on so-called loops in control-flow graph, without going into much detail. Loops in programs are a are thankful places for optimizations. That's sometimes called *loop optimization*. That's not necessarily specific analysis or optimizations working only for loops. For instance, liveness analysis and corresponding register allocation strategies are conceptually not different control-flow graphs containing loops or not. But a good or aggreessive analysis and register allocation for loops, specially for smalls ones that are taken very often during execution may greatly improve the performance.

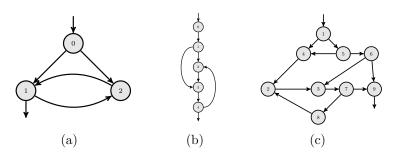

Programming language looping constructs —while-loop, for-loop etc—- leads to cycles in the graph. However, **not all cycles in a cfg are loops.** In other words, the concept of loops in control flow graphs is **not** identical with **cycles** in a graph.

All **loops** are graph **cycles** but not vice versa.

Intuitively, loops are cycles originating from source-level looping constructs, like while. Gotos, on the other hand, may lead to non-loop cycles in the CFG.

Why does one even bother to make that distinction? Actually, sometimes one does not. For instance, later we will look into global liveness analysis, a form of data flow analysis. For that we sketch an algorithms, that works for general control flow graphs, with loops or cycles (and also for control-flow graphs without cycles ...). We won't show in detail how to tune the data flow analysis algorithm for efficiency. for instance relying on particular graph traversal strategies.

But that's the point: loops as a restricted form of cycles would allow particular traversal strategies that perform better, but that can't be applied on general cycles. Of course, with no cycles at all and the control-flow graph as directed acyclic graph, even better strategies are possible. As a matter of fact, the *local* liveness analysis we look at first deals with basic blocks, i.e., straight-line code, and that is *even more* restricted than just being acyclic. And thus the liveness analysis become even more simple and efficient.