## Neuromorphic Electronics

### Lecture Notes

Fall Term 2010

Department of Informatics

University of Oslo

read by

Philipp D. Häfliger

## Abstract

This is the script for an introductory course in neuromorphic electronic circuits. These are circuits inspired by the nervous system that either help verifying neuro-physiological models, or that are useful components in artificial perception/action systems. Research also aims at using them in implants. These circuits are computational devices and intelligent sensors that are very differently organized than digital processors. Their storage and processing capacity is distributed. They are asynchronous and use no clock signal. They are often purely analog and operate time continuous. They are adaptive or can even learn on a basic level instead of being programmed. A short introduction into the area of brain research is also included in the course.

The students will learn to exploit mechanisms employed by the nervous system for compact energy efficient analog integrated circuits. They will get insight into a multidisciplinary research area. The students will learn to analyze analog CMOS circuits and acquire basic knowledge in brain research methods.

The script is not really a book yet and many of the explanations are brief and not very detailed. The script is intended as supportive material for the course and may be quite unsatisfying to read without attending the lectures. The students are strongly encouraged to add their own notes to these pages.

## Contents

| $\mathbf{A}$ | bstra | $\operatorname{ct}$                              |   |

|--------------|-------|--------------------------------------------------|---|

| 1            | Intr  | oduction                                         |   |

|              | 1.1   | Neuromorphic Circuits at Present                 |   |

| 2            | Neu   | rophysiology in a Nutshell                       |   |

|              | 2.1   | Methods                                          |   |

|              |       | 2.1.1 Psychophysical Experiments                 |   |

|              |       | 2.1.2 EEG                                        |   |

|              |       | 2.1.3 fMRI and PET                               |   |

|              |       | 2.1.4 Extracellular Electrodes                   |   |

|              |       | 2.1.5 Intracellular Electrodes                   |   |

|              |       | 2.1.6 Fluorescent Tracers and Imaging            |   |

|              |       | 2.1.7 Briefly Mentioned: Methods in Neuroanatomy |   |

|              | 2.2   | Knowledge                                        |   |

|              |       | 2.2.1 Brain Anatomy                              |   |

|              |       | 2.2.2 Cortical Regions                           |   |

|              |       | 2.2.3 Organization within Cortical Regions       |   |

|              |       | 2.2.4 Microcolumns and Cortical Layers           |   |

|              |       | 2.2.5 Neurons and Synapses                       |   |

| 0            | ъ     | ' A 1 CMOS                                       |   |

| 3            |       | ic Analog CMOS                                   | 2 |

|              | 3.1   | Field Effect Transistors                         | • |

|              |       | 3.1.1 Basic Formulae                             |   |

|              |       | 3.1.2 Early effect                               |   |

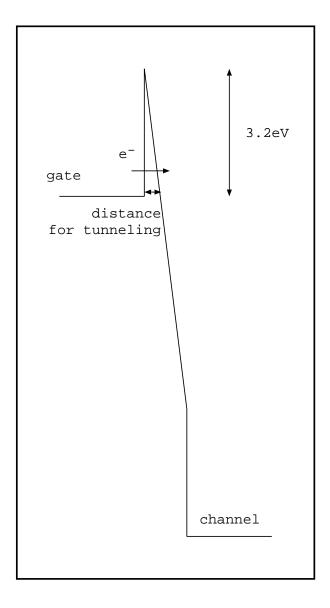

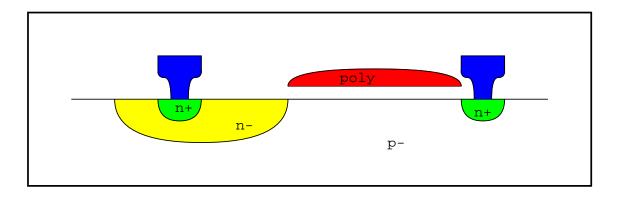

|              | 0.0   | 3.1.3 Gate leakage                               | : |

|              | 3.2   | Capacitors                                       | : |

|              | 3.3   | Current Mirror                                   |   |

|              | 3.4   | Differential Pair                                |   |

|              | 3.5   | Transconductance Amplifier                       |   |

|              | 3.6   | Follower                                         | ; |

|              | 3.7   | Resistor                                         | ; |

|              | 3.8   | Resistive Nets                                   |   |

|              | 3.9   | The Winner Take All Circuit                      | , |

| 4            | Rea   | l and Silicon Neurons                            | 4 |

|              | 4.1   | Real Neurons                                     |   |

|              | 4.2   | aVLSI Models of Neurons                          |   |

|              |       | 4.2.1 Simple Electrical Nodes as Neurons         |   |

|              |       | 4.2.2 Perceptrons (Mc Culloch Pitts neurons)     |   |

|              |       | 4.2.2 Integrate and Fire Neurons                 |   |

iv CONTENTS

|   |       | 4.2.4   | Compartemental Neuronal Models (Silicon Neurons)     | 2 |

|---|-------|---------|------------------------------------------------------|---|

| 5 | Cod   | ling in | the Nervous System 5'                                | 7 |

|   | 5.1   | The ac  | etion potential                                      | 7 |

|   | 5.2   |         | in Experiments                                       | 7 |

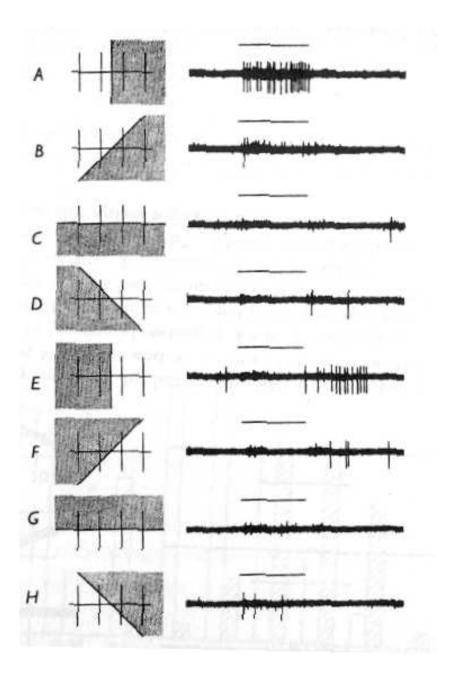

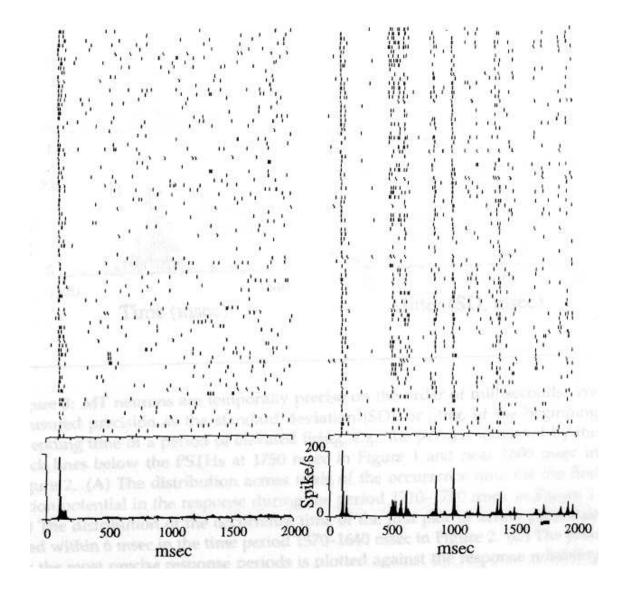

|   |       | 5.2.1   | Classical experiments based on observing spike rates | 7 |

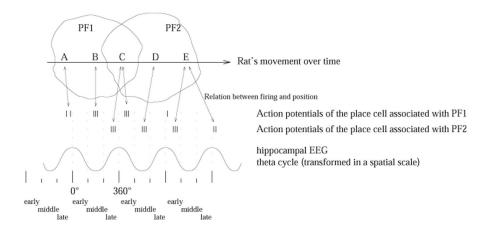

|   |       | 5.2.2   | Classical Experiments observing temporal spike codes | 0 |

|   | 5.3   | Candio  | late Codes                                           | 3 |

| 6 | Neu   | ıromor  | phic Communication: the AER Protocol 6'              | 7 |

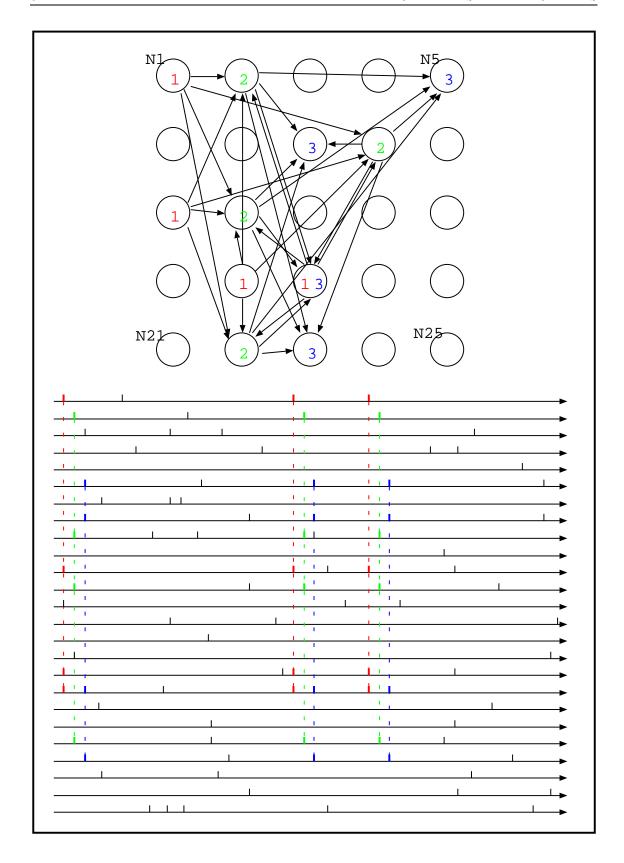

|   | 6.1   |         | asic Idea of Address Event Representation (AER) 6    |   |

|   | 6.2   |         | on Handling                                          | 9 |

|   |       | 6.2.1   | Full Arbitration                                     | 9 |

|   |       | 6.2.2   | Collision Discarding                                 | 3 |

|   |       | 6.2.3   | Aging versus Loss Trade Off                          |   |

| 7 | Ret   | inomoi  | rphic Circuits 7'                                    | 7 |

| • | 7.1   |         | etina                                                |   |

|   | 7.2   |         | Sphoto sensors                                       |   |

|   | • • • | 7.2.1   | Photo diodes                                         |   |

|   |       | 7.2.2   | Photo transistors                                    |   |

|   |       | 7.2.3   | Photo gates                                          |   |

|   | 7.3   |         | Current Amplification                                |   |

|   |       | 7.3.1   | Linear by Early effect                               |   |

|   |       | 7.3.2   | Logarithmic by gate to source voltage                |   |

|   |       | 7.3.3   | Common source amplification                          |   |

|   |       | 7.3.4   | Source follower                                      |   |

|   | 7.4   |         | Out Strategies                                       |   |

|   |       | 7.4.1   | Addressing and scanning                              |   |

|   |       | 7.4.2   | Charge coupled devices (CCD)                         |   |

|   |       | 7.4.3   | Address event representation                         |   |

|   | 7.5   | Silicon | retinae                                              |   |

|   |       | 7.5.1   | Adaptive photo cell                                  |   |

|   |       | 7.5.2   | Spatial contrast retina                              |   |

|   |       | 7.5.3   | Temporal contrast retina                             |   |

|   | 7.6   | Furthe  | r Image Processing                                   |   |

|   |       | 7.6.1   | Motion                                               |   |

|   |       | 7.6.2   | Feature maps                                         |   |

| 8 | Coc   | hleom   | orphic Circuits 11:                                  | 1 |

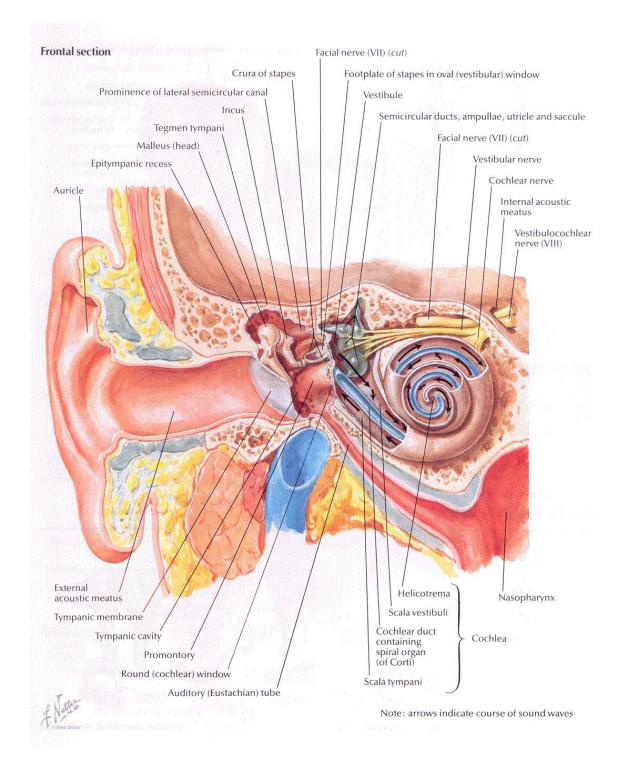

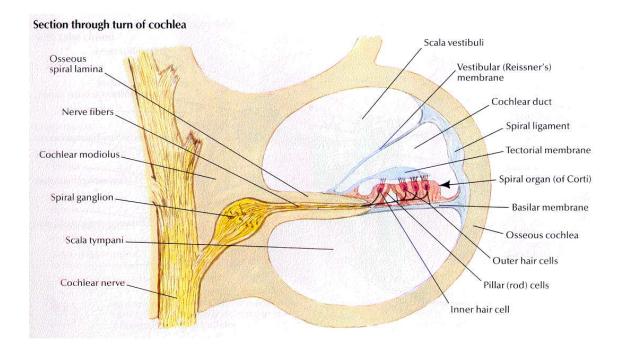

| G | 8.1   |         | ochlea                                               |   |

|   | 8.2   |         | Cochlea                                              |   |

|   |       |         |                                                      | _ |

| 9 |       |         | phic Learning 11                                     |   |

|   | 9.1   |         | Learning Algorithms                                  |   |

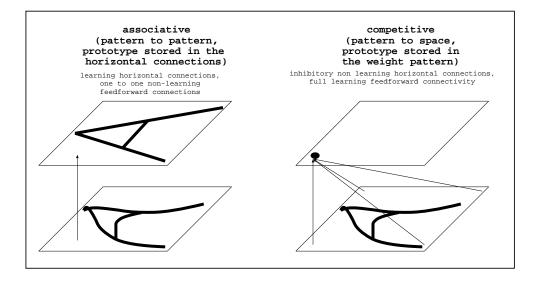

|   |       | 9.1.1   | An overview of classes of learning algorithms        |   |

|   |       | 9.1.2   | Supervised Learning                                  |   |

|   |       | 9.1.3   | Reinforcement learning                               |   |

|   | 0.0   | 9.1.4   | Unsupervised learning                                |   |

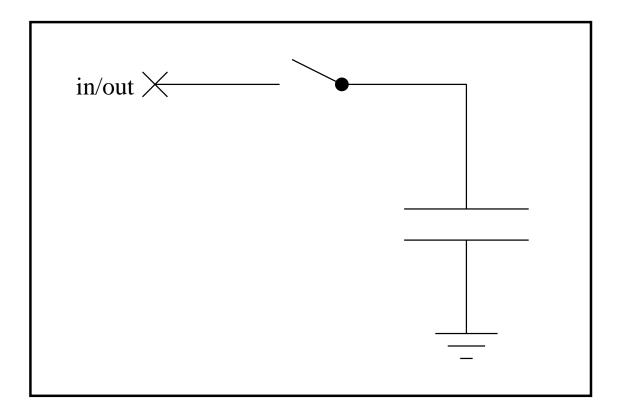

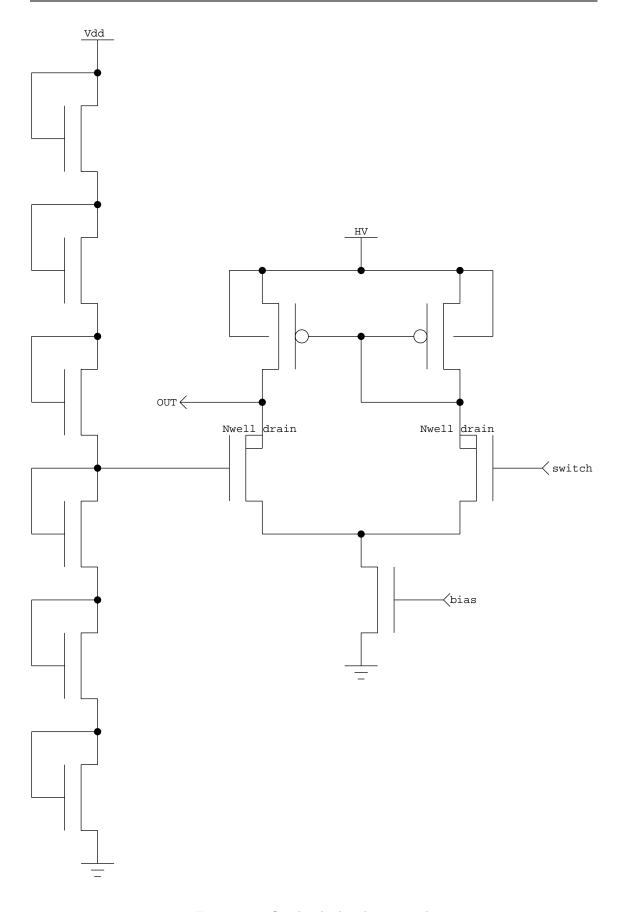

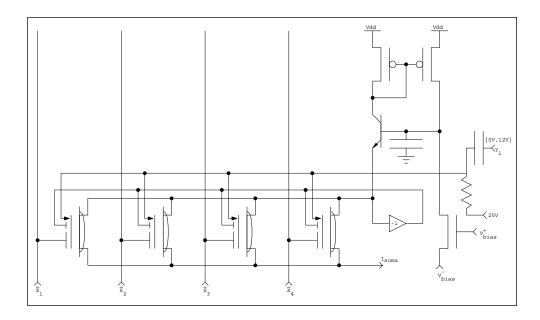

|   | 9.2   | -       | gue Storage                                          |   |

|   |       | 9.2.1   | Dynamic Analogue Storage                             |   |

|   |       | 9.2.2   | Static Analogue Storage                              |   |

|   |       | 9.2.3   | Non-Volatile Analogue Storage                        | 4 |

CONTENTS

|              | 9.3 | Neuromorphic Learning Circuits               |     |

|--------------|-----|----------------------------------------------|-----|

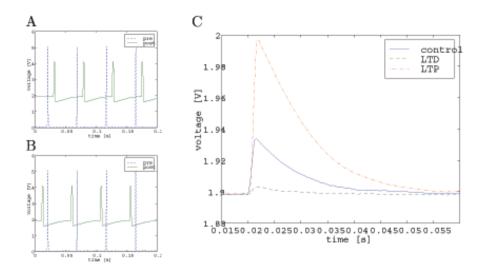

|              |     | 9.3.1 Hebbian learning circuits              | 137 |

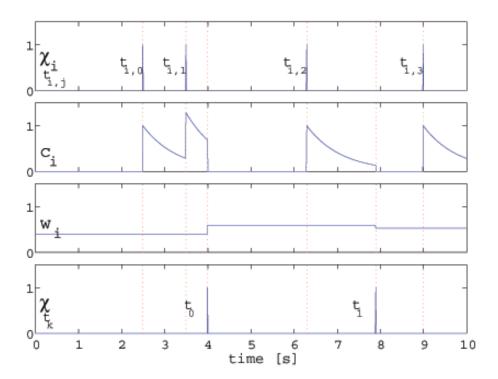

|              |     | 9.3.2 A spike based learning circuit         | 141 |

| $\mathbf{A}$ | Que | estions Catalogue                            | 145 |

|              | A.1 | Introduction                                 | 145 |

|              | A.2 | Neurophysiology                              | 145 |

|              | A.3 | Basic Analogue CMOS                          | 145 |

|              | A.4 | Real and Silicon Neurons                     | 146 |

|              | A.5 | Coding in the Nervous System                 | 146 |

|              | A.6 | Neuromorphic Communication: the AER Protocol | 146 |

|              | A.7 | Retinomorphic Circuits                       | 147 |

|              | A.8 | Cochleomorphic Circuits                      | 147 |

|              | A.9 | Neuromorphic Learning                        | 147 |

vi CONTENTS

# List of Figures

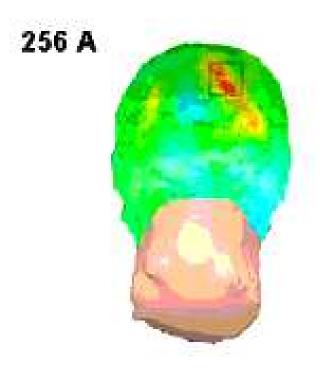

| 2.1  | EEG array based reconstruction of brain activity | 1 |

|------|--------------------------------------------------|---|

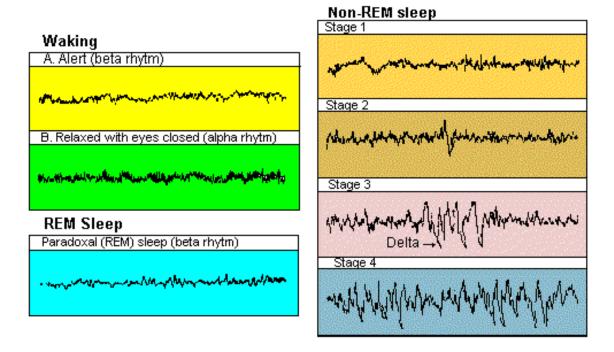

| 2.2  | EEG of sleep stages                              | 5 |

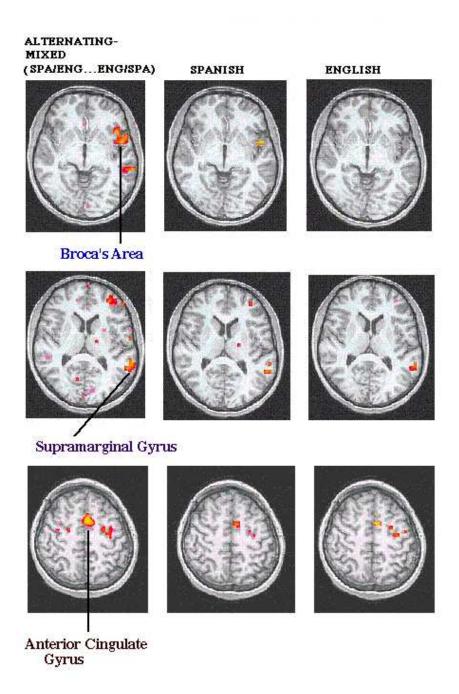

| 2.3  | fMRI in bilingual task                           | 3 |

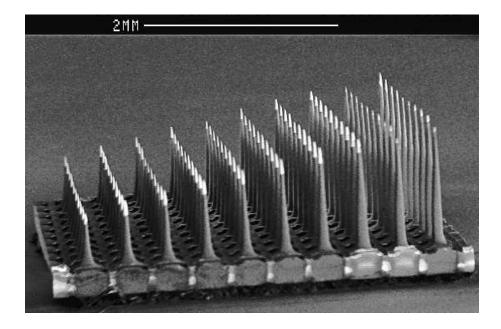

| 2.4  | The Utah electrode array                         | 7 |

| 2.5  | Patch clamp electrodes                           | 3 |

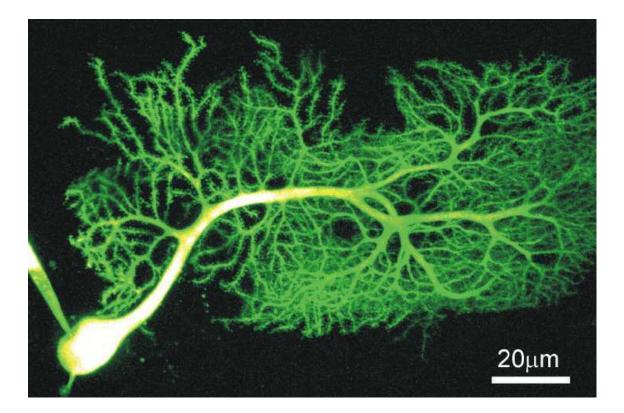

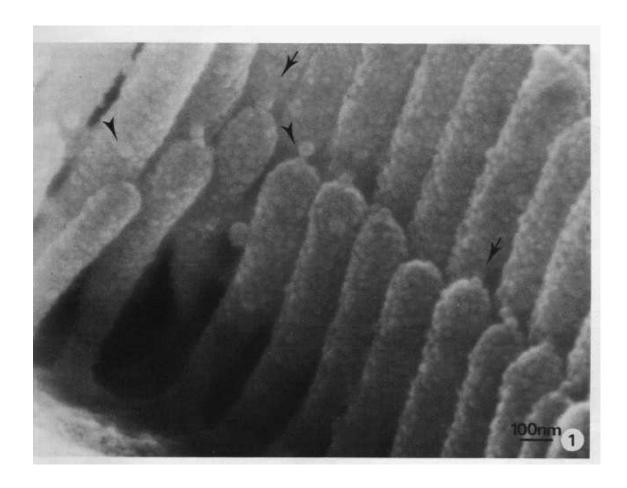

| 2.6  | Fluorescent tracers in Purkinje cell             | ) |

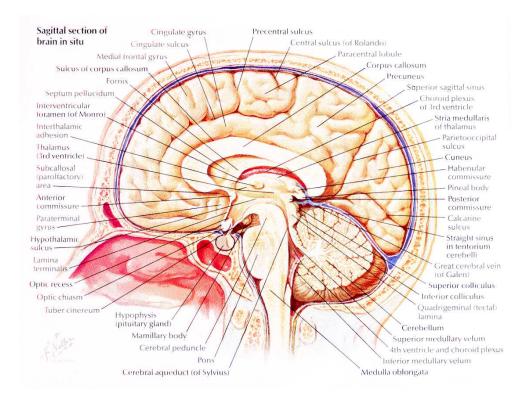

| 2.7  | Brain Cross section illustration                 | ) |

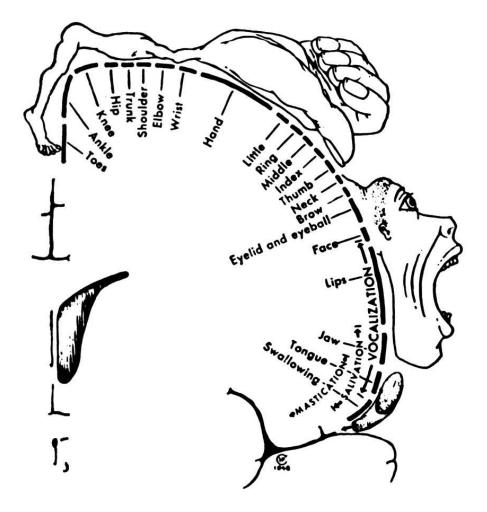

| 2.8  | Motor-cortex homunculus                          | 1 |

| 2.9  | Brain research by Garry Larson                   | 2 |

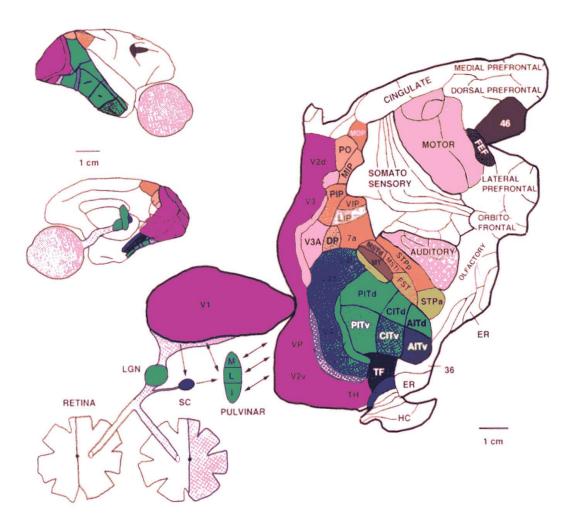

| 2.10 | Cortical regions in a cat                        | 3 |

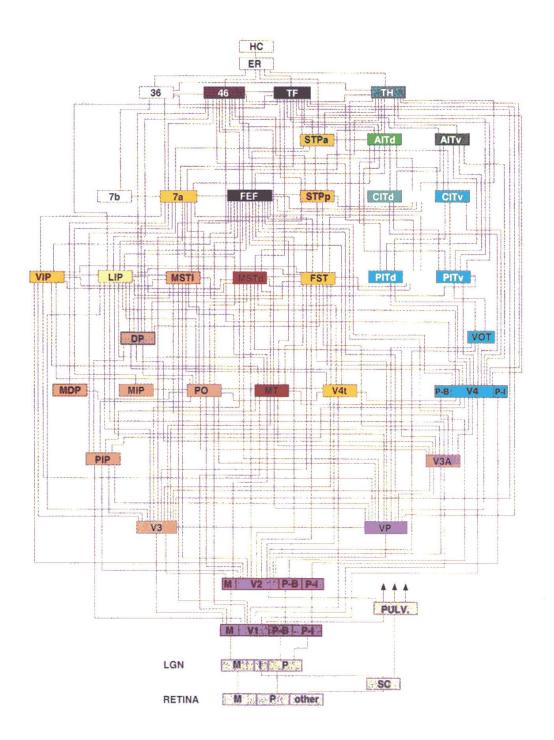

| 2.11 | Cortical regions hierarchy                       | 1 |

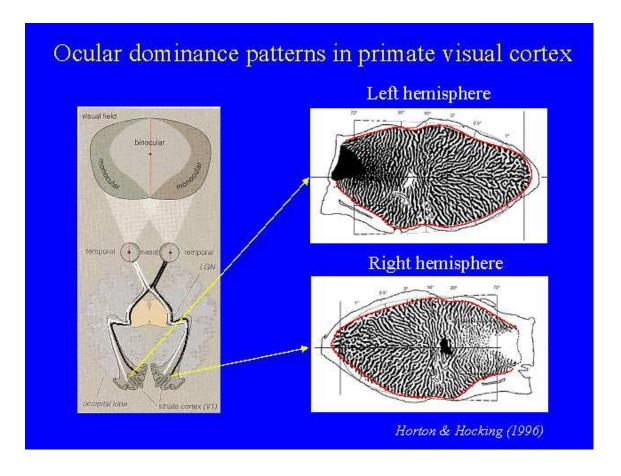

| 2.12 | ocular dominance patterns on V1                  | 5 |

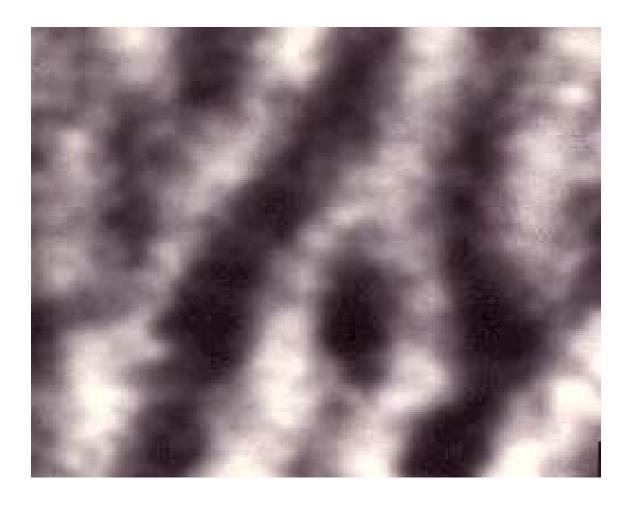

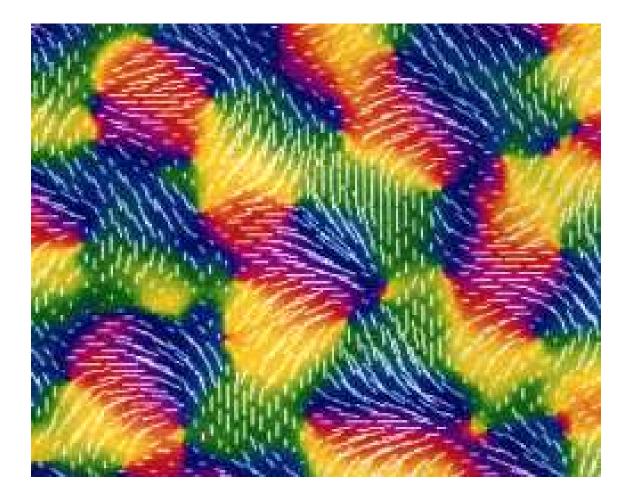

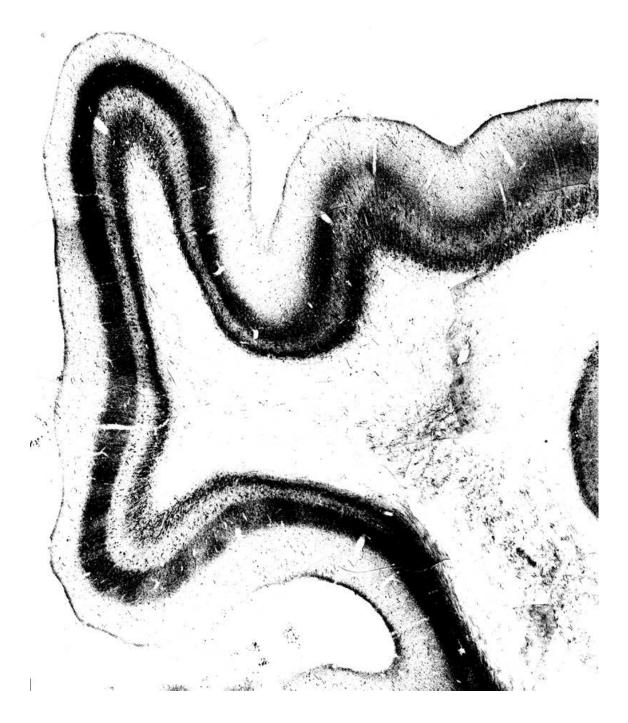

| 2.13 | ocular dominance patterns close-up               | 3 |

| 2.14 | Orientation selectivity patterns                 | 7 |

| 2.15 | Cortical layers staining illustration 1          | ) |

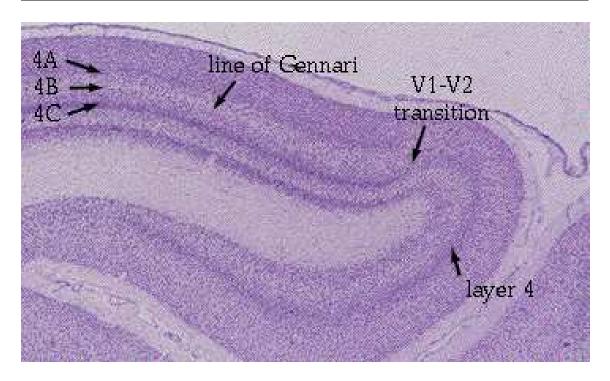

| 2.16 | Cortical layers staining illustration 2          | ) |

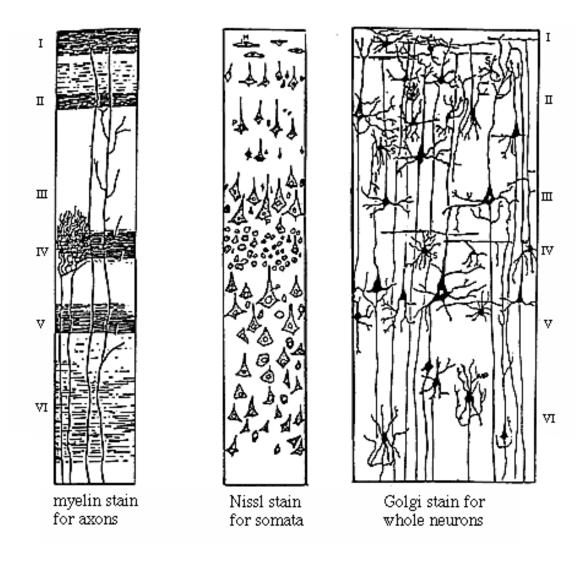

| 2.17 | Cortical layers staining techniques              | 1 |

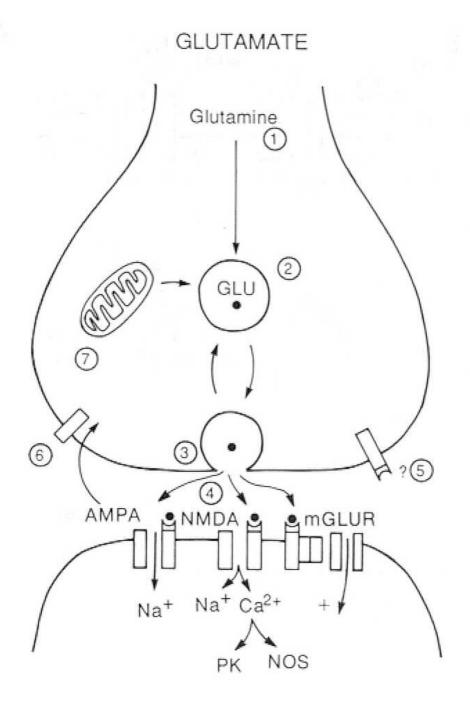

| 2.18 | Schematic synapse                                | 2 |

|      |                                                  |   |

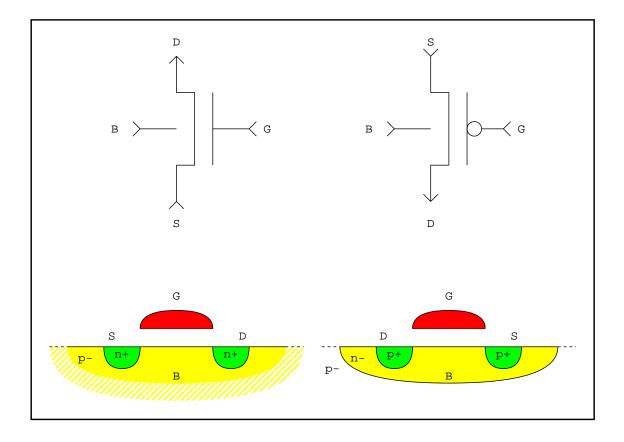

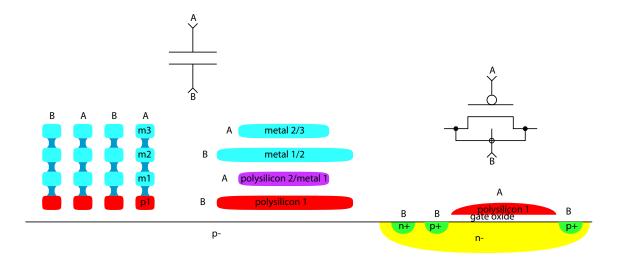

| 3.1  | FETs 24                                          |   |

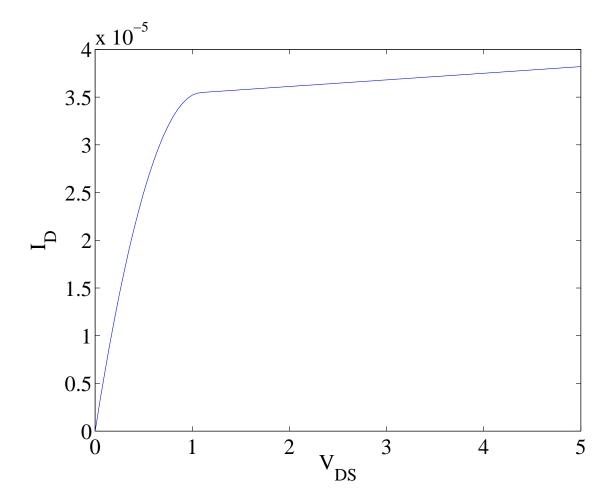

| 3.2  | $I_{DS}$ vs. $V_DS$                              | - |

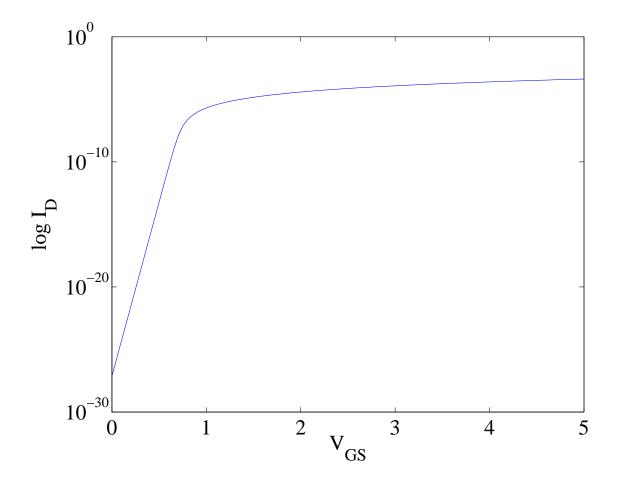

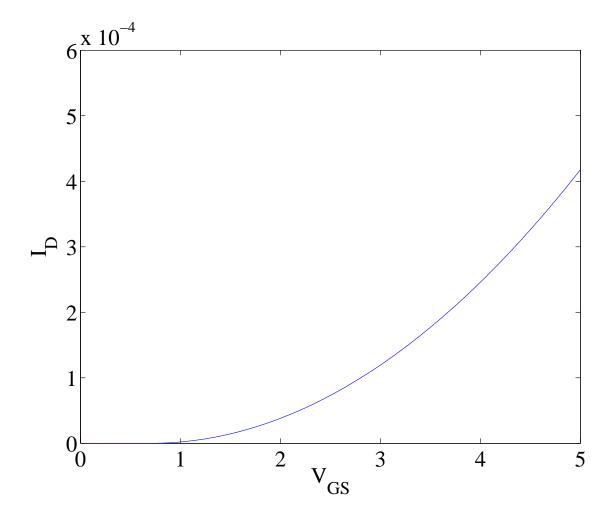

| 3.3  | $I_{DS}$ vs. $V_G$                               |   |

| 3.4  | $I_{DS}$ vs. $V_G$                               |   |

| 3.5  | Capacitances in CMOS                             |   |

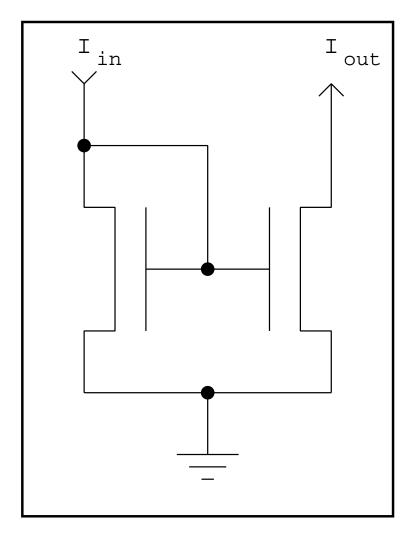

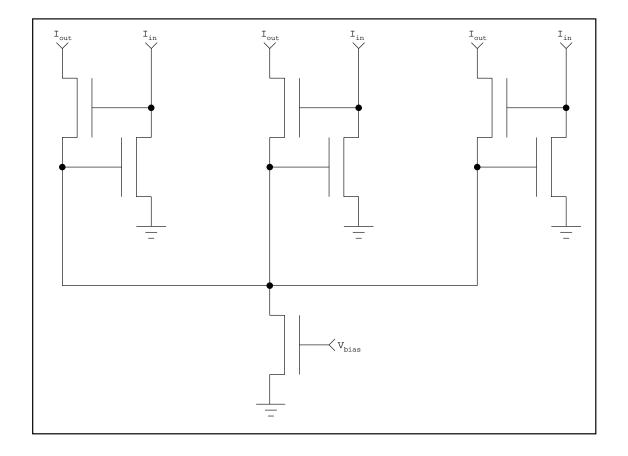

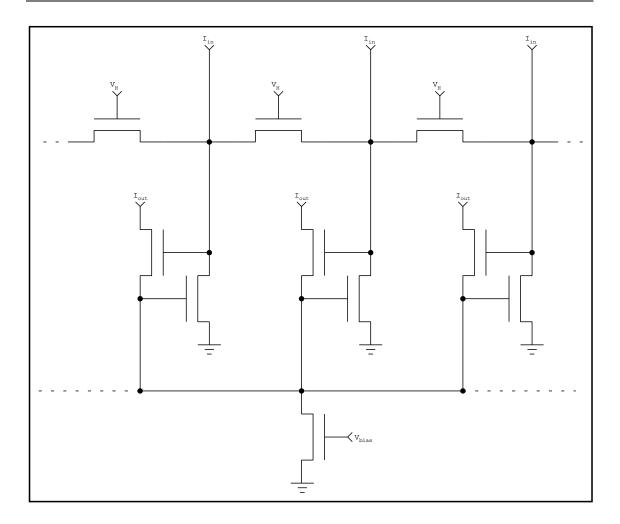

| 3.6  | Current mirror                                   |   |

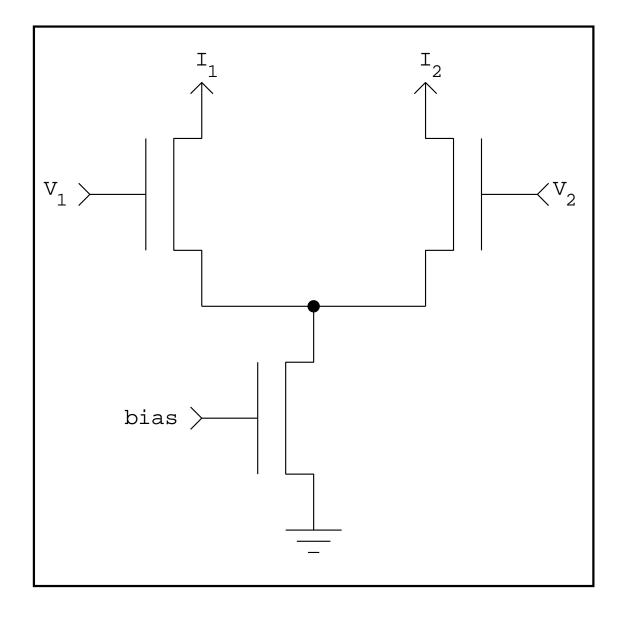

| 3.7  | Differential pair                                |   |

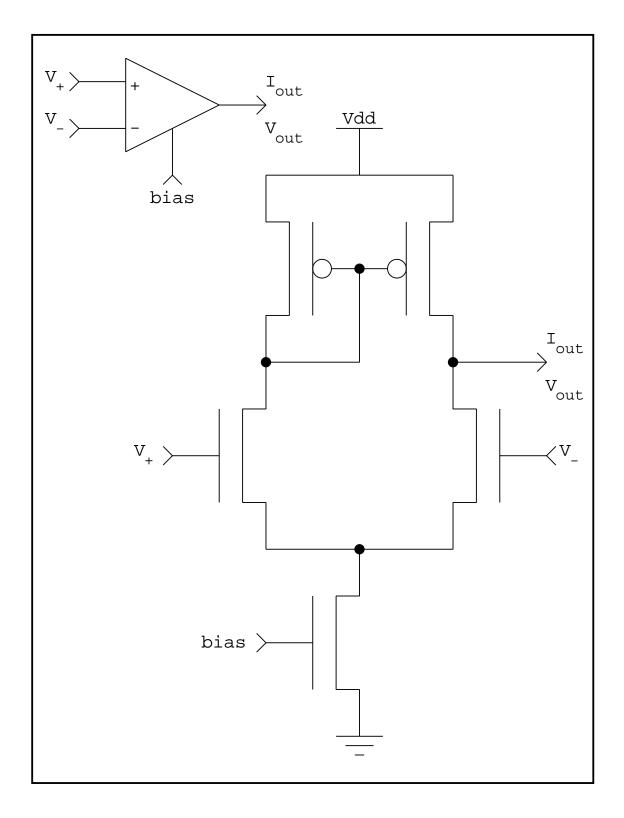

| 3.8  | Transconductance amplifier                       |   |

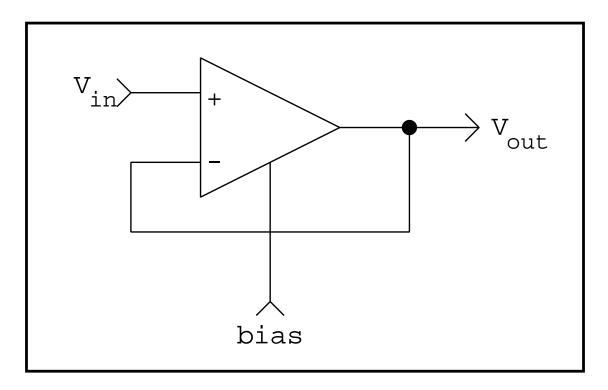

| 3.9  | Follower                                         |   |

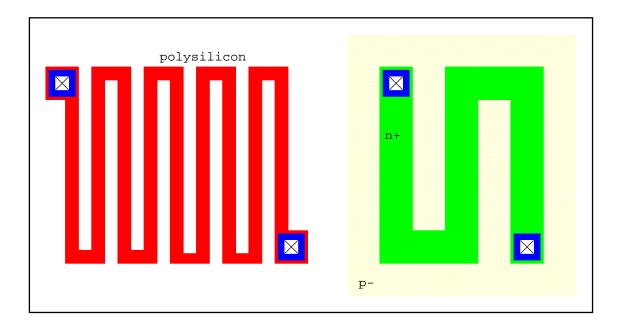

|      | Resistors in CMOS                                |   |

|      | Resistive net                                    |   |

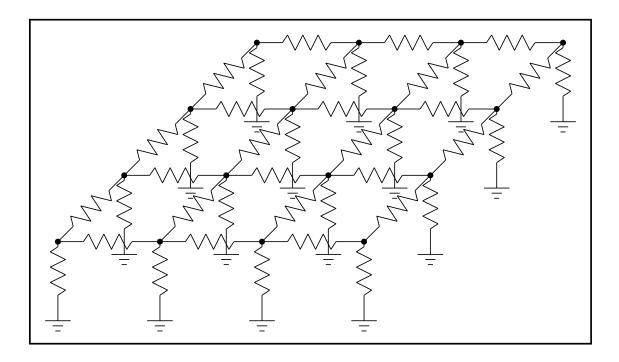

|      | Diffuser net                                     |   |

|      | WTA principle                                    |   |

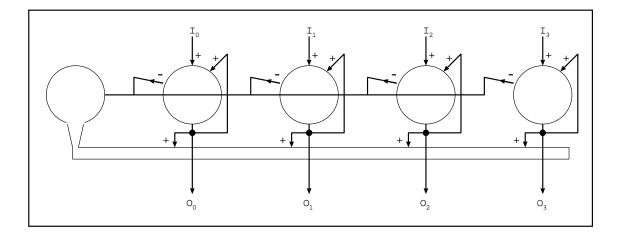

|      | CMOS WTA                                         |   |

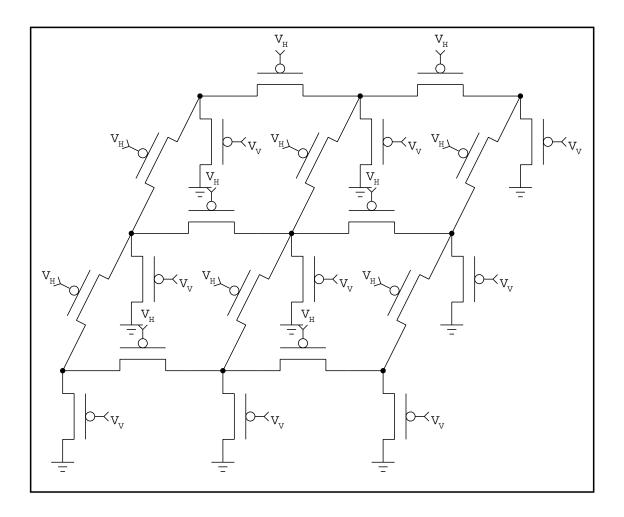

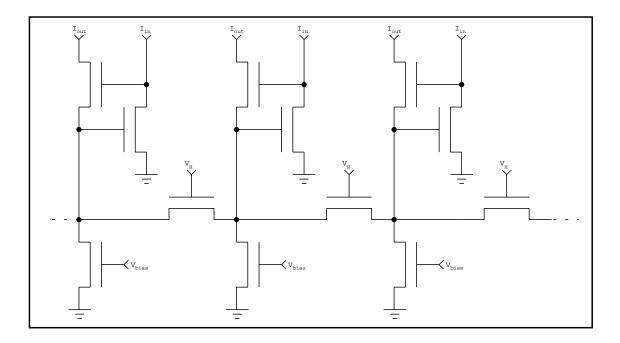

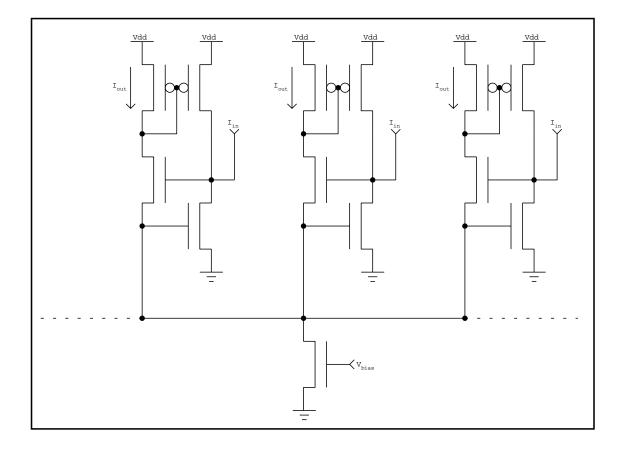

|      | WTA with spatial smoothing                       |   |

|      | local WTA                                        | ) |

| 3.17 | WTA with hysteresis                              | Ĺ |

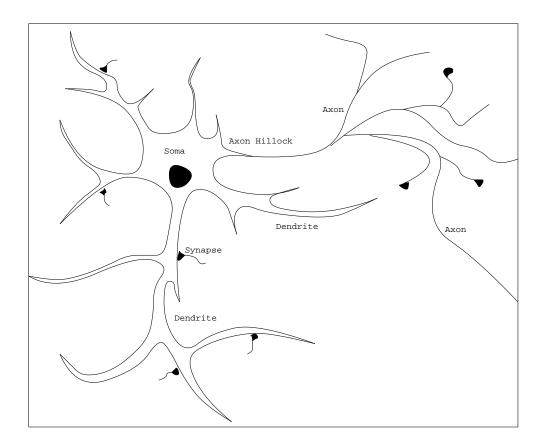

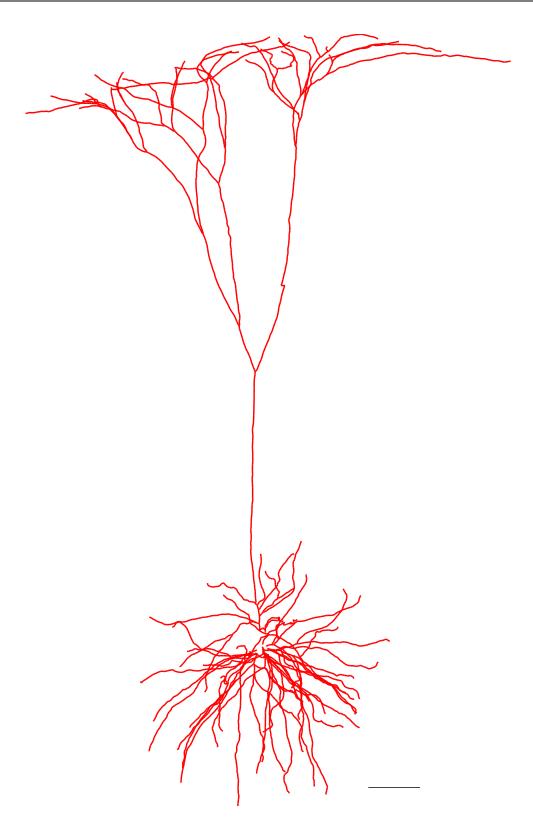

| 4.1  | Anatomical Parts of a Neuron                     | 1 |

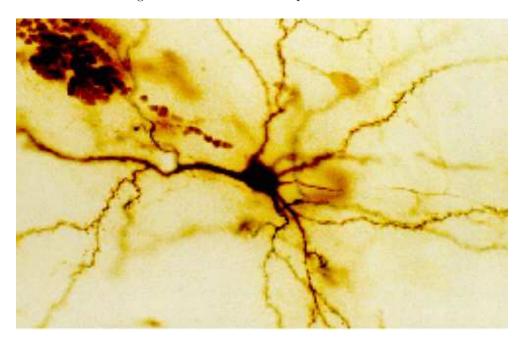

| 4.1  | Light Microscope Neuron                          |   |

| 4.2  | 3D Reconstruction of Pyramidal Call              |   |

viii LIST OF FIGURES

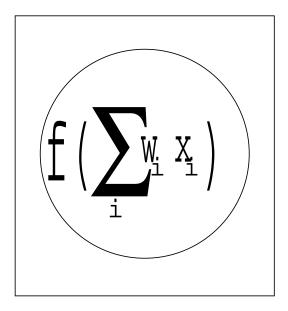

| Perceptron Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

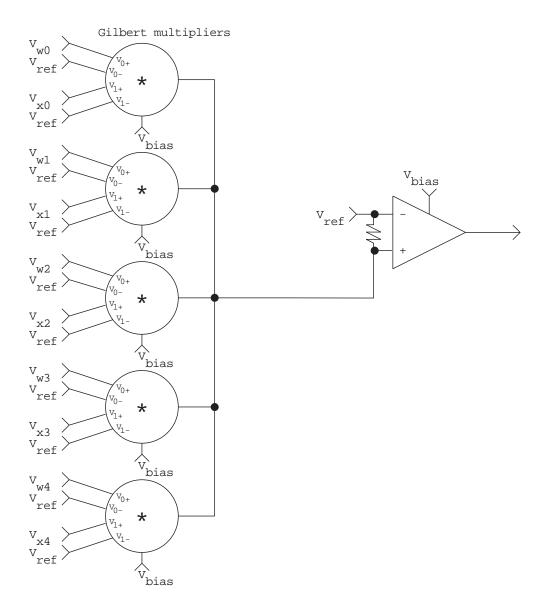

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

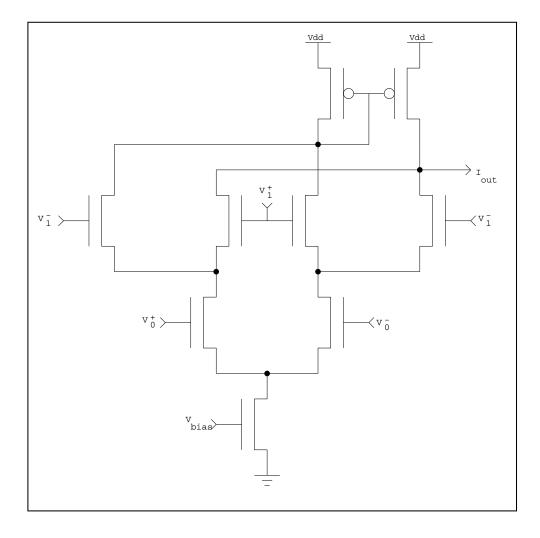

| Gilbert Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

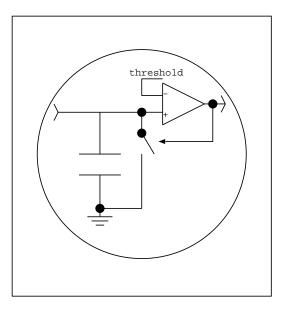

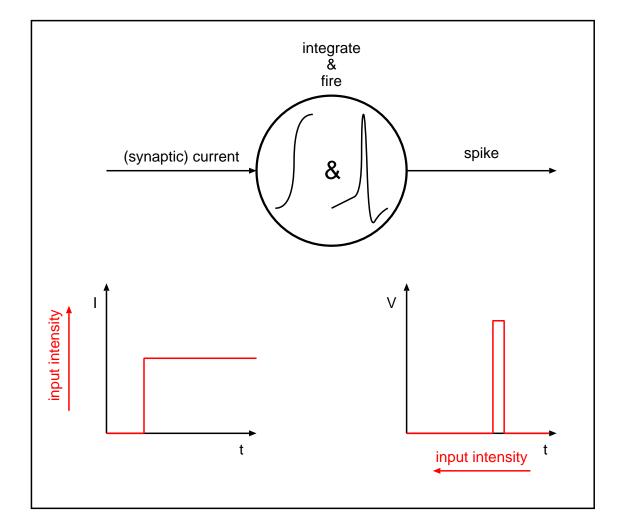

| Adaptive Integrate-and-Fire Neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

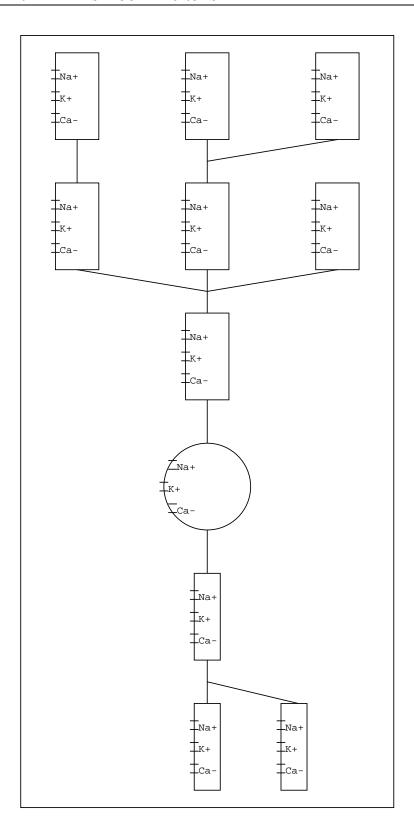

| Compartemental Neuron Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

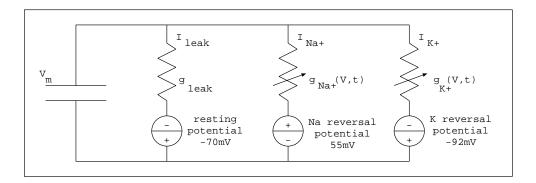

| The Hudgkin Huxley Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

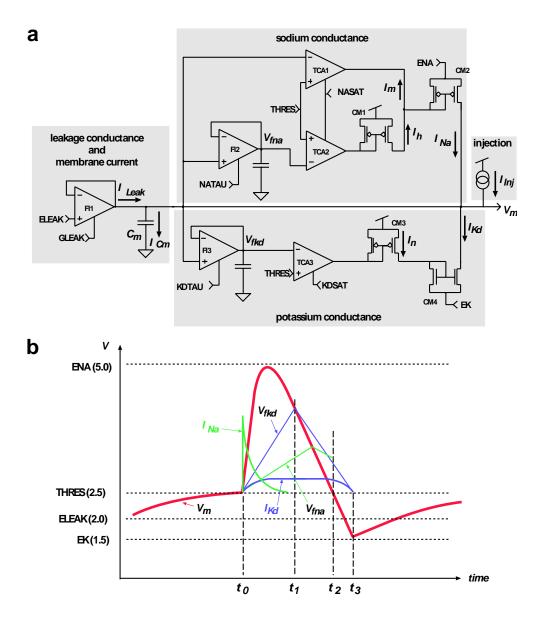

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

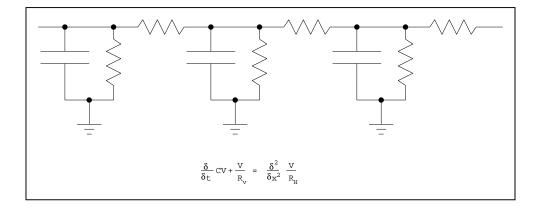

| Cable Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>F</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

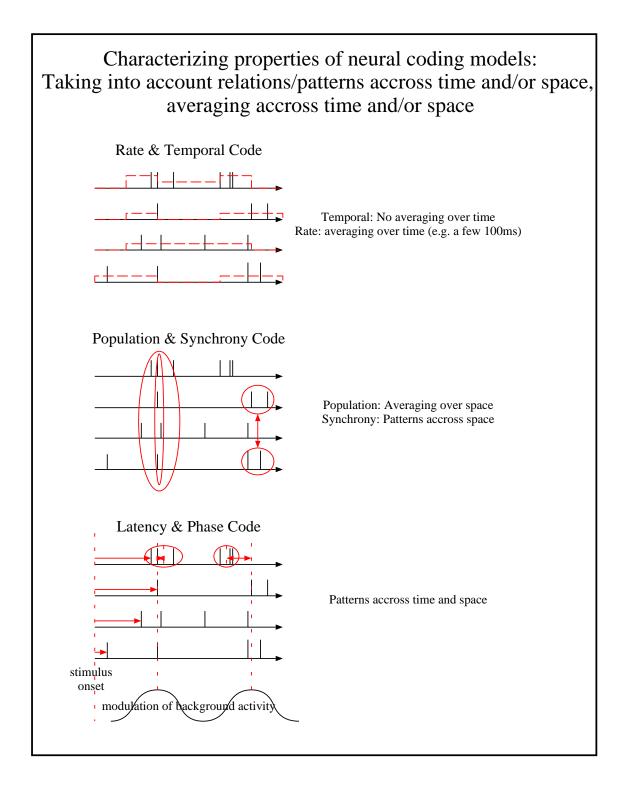

| Latency coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

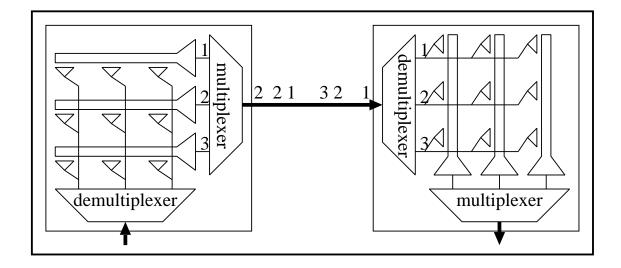

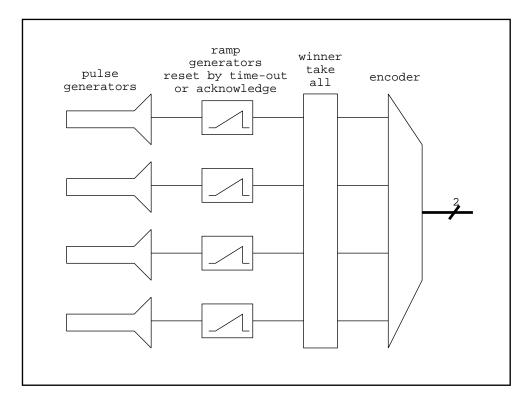

| Address Event Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

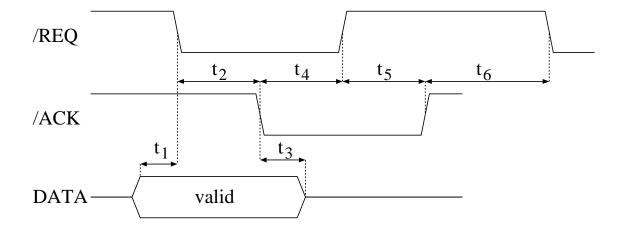

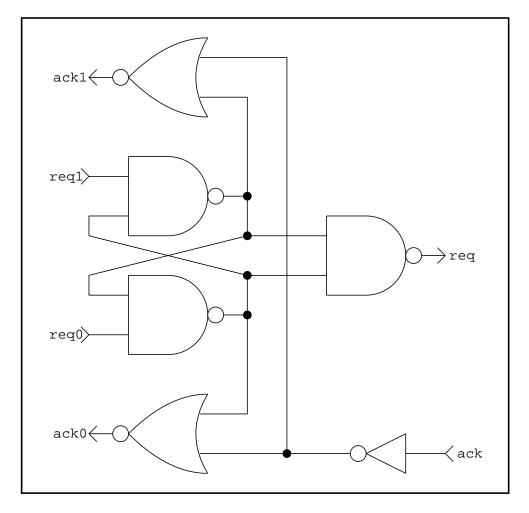

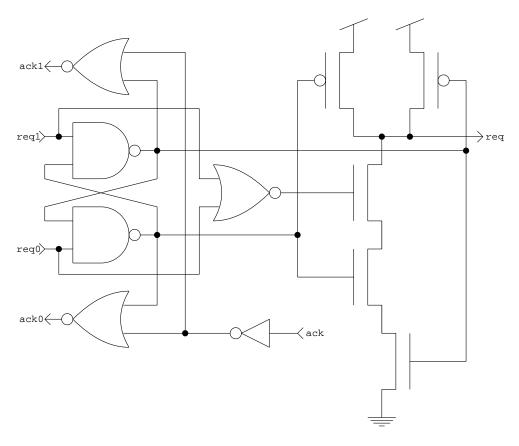

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

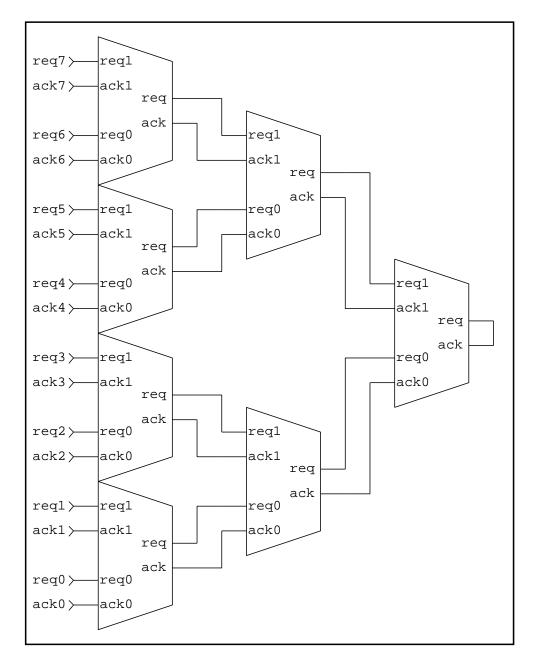

| Dipagra arbitan trae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70<br>71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

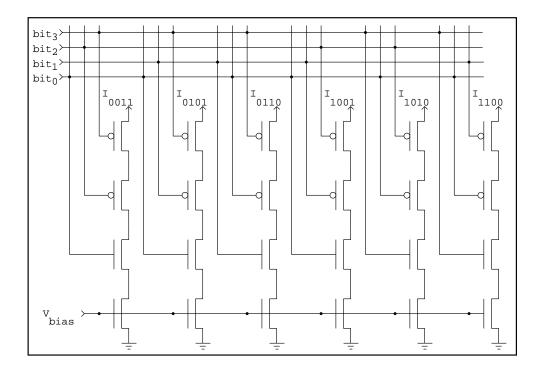

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Aging versus loss trade on Alit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

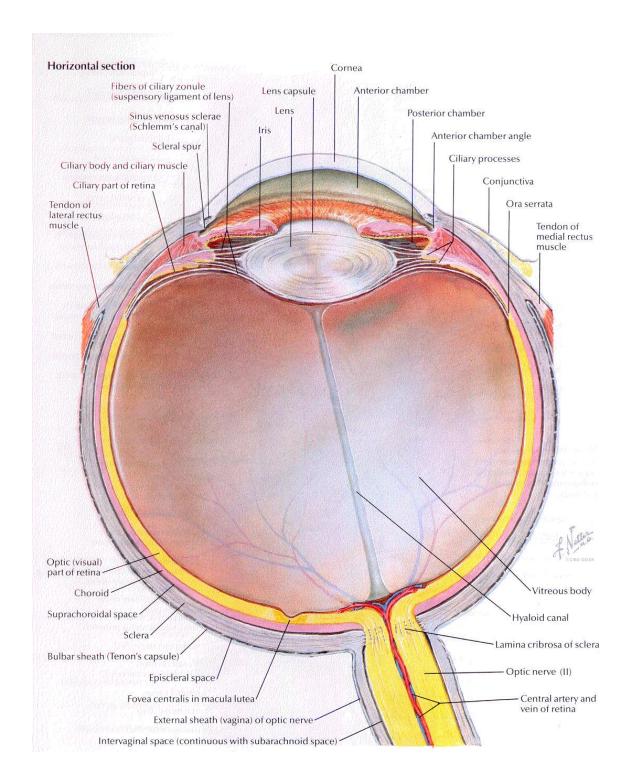

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

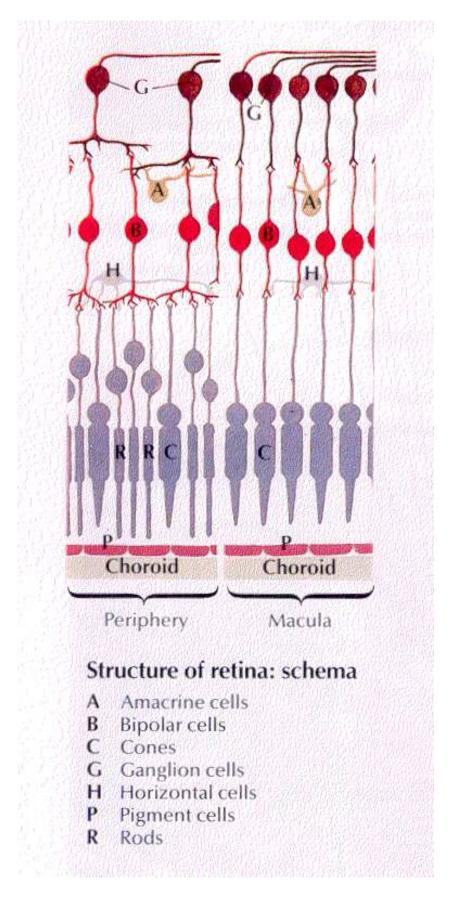

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

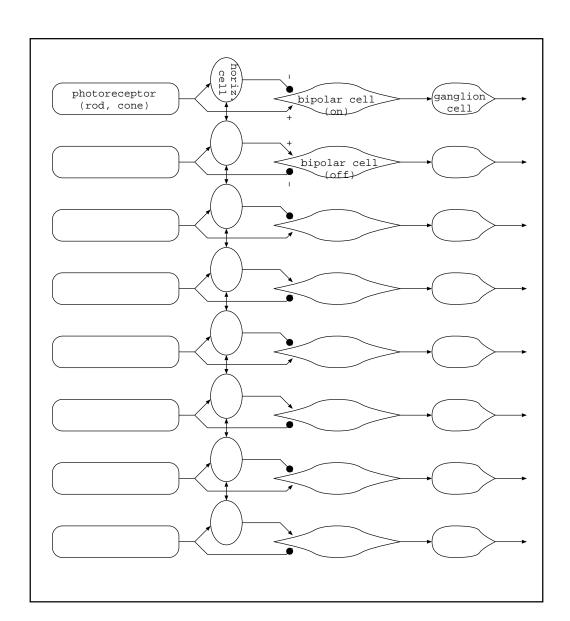

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

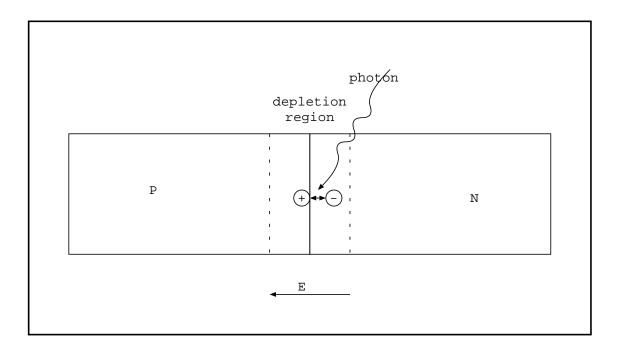

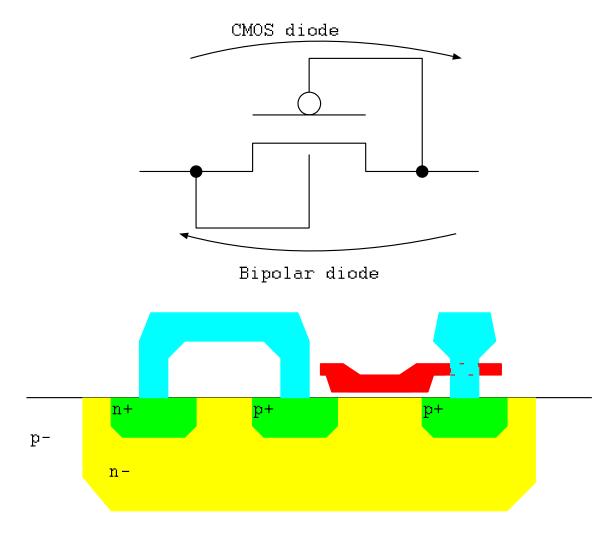

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

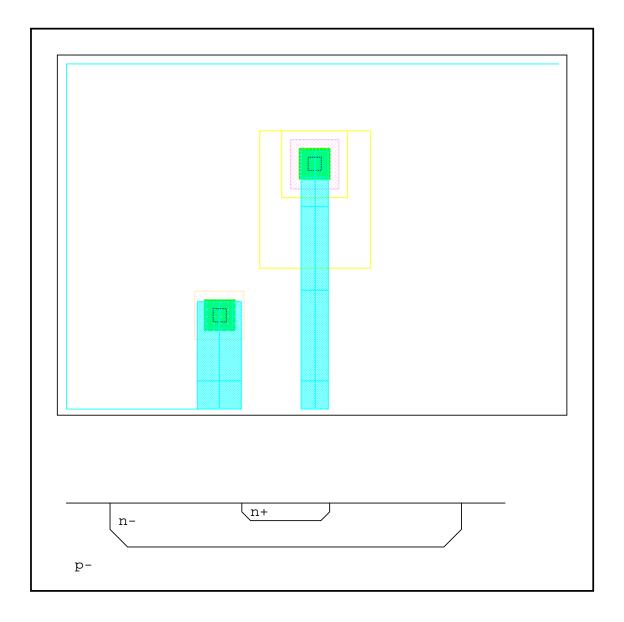

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

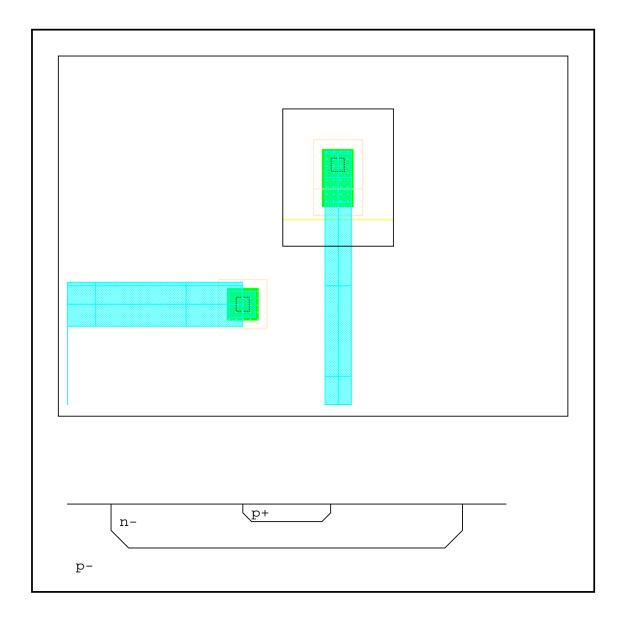

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83<br>84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83<br>84<br>85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

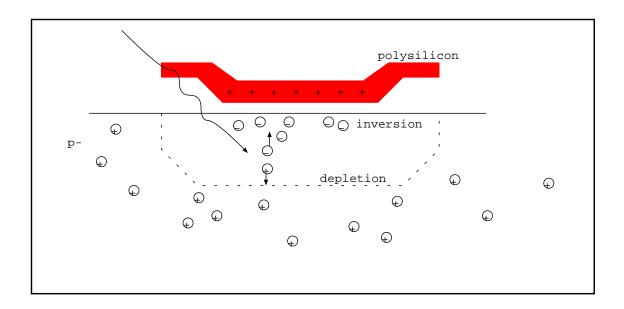

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>85<br>86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Eyball cross section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>85<br>86<br>87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

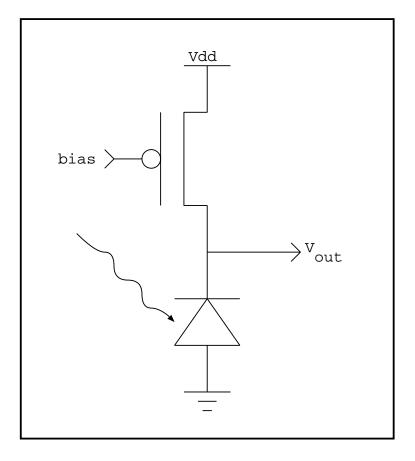

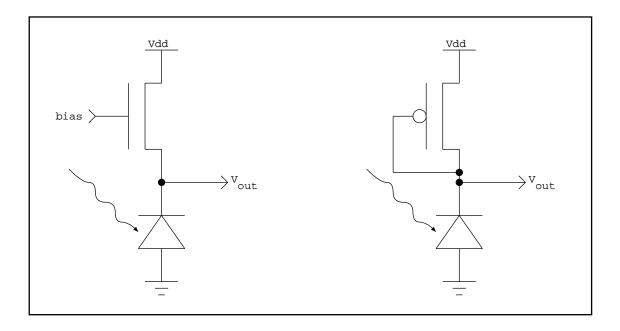

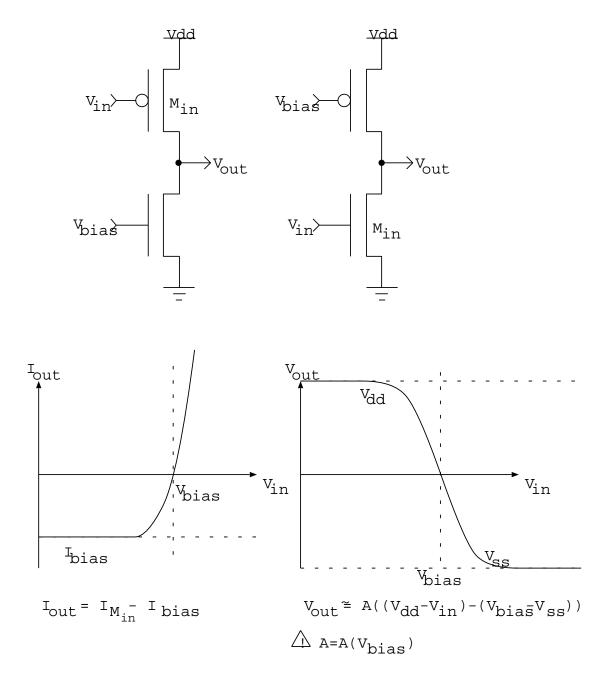

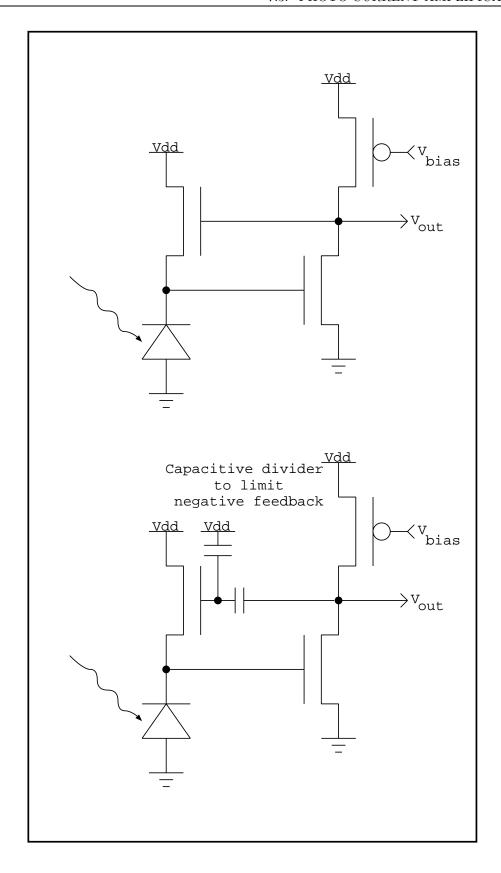

| Eyball cross section .  Detailed retinal cells .  Schematic retinal cells .  Photo diode .  Photo diode layout .  PNP photo transistor .  Photo gate .  Amplification by drain resistance .  Logarithmic amplification .  Two transistor inverting amplifier .  Negative feedback .                                                                                                                                                                                                                                                                                                    | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>85<br>86<br>87<br>88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

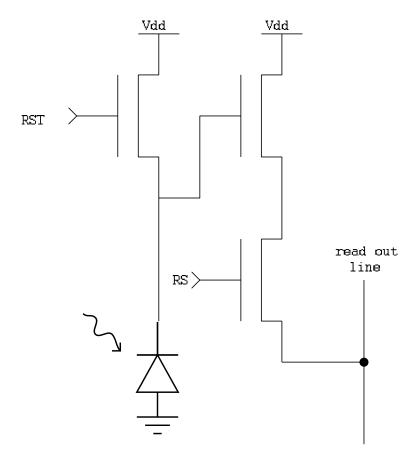

| Eyball cross section .  Detailed retinal cells .  Schematic retinal cells .  Photo diode .  Photo diode layout .  PNP photo transistor .  Photo gate .  Amplification by drain resistance .  Logarithmic amplification .  Two transistor inverting amplifier .  Negative feedback .  Active pixel .                                                                                                                                                                                                                                                                                    | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>85<br>86<br>87<br>88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Eyball cross section .  Detailed retinal cells .  Schematic retinal cells .  Photo diode .  Photo diode layout .  PNP photo transistor .  Photo gate .  Amplification by drain resistance .  Logarithmic amplification .  Two transistor inverting amplifier .  Negative feedback .  Active pixel .  CCD .                                                                                                                                                                                                                                                                             | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Eyball cross section .  Detailed retinal cells .  Schematic retinal cells .  Photo diode .  Photo diode layout .  PNP photo transistor .  Photo gate .  Amplification by drain resistance .  Logarithmic amplification .  Two transistor inverting amplifier .  Negative feedback .  Active pixel .  CCD .  AER photo pixel .                                                                                                                                                                                                                                                          | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

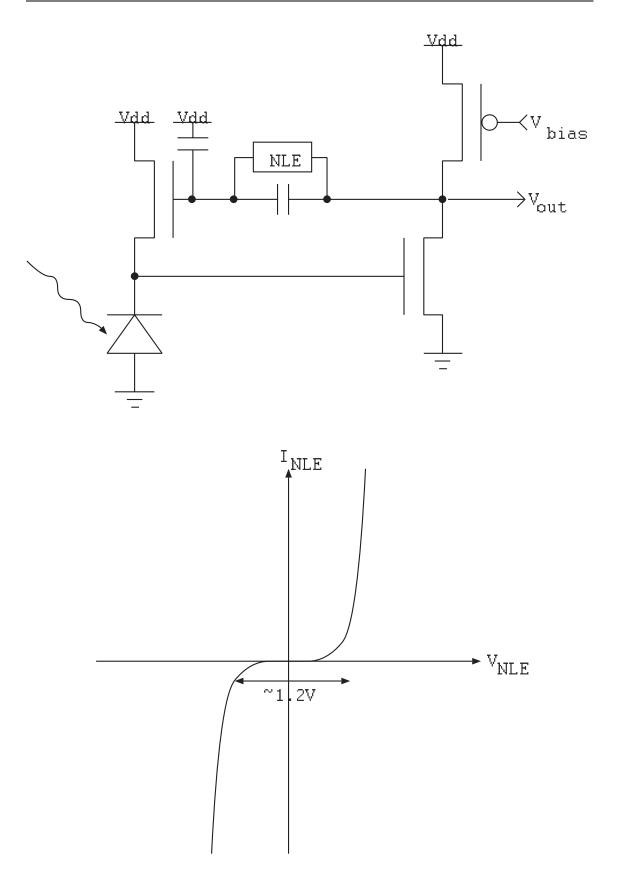

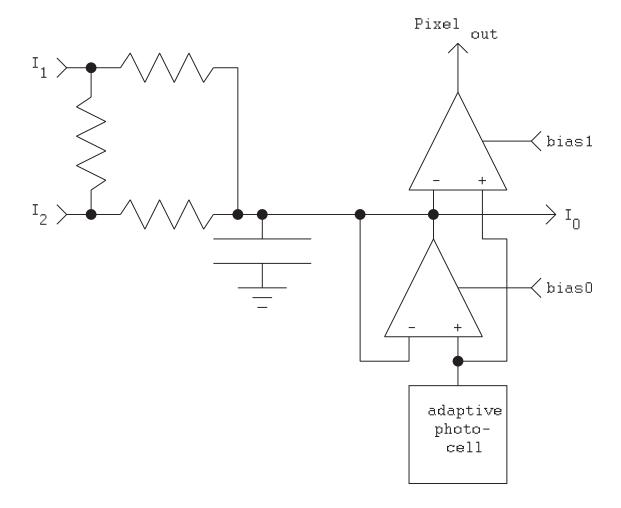

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell                                                                                                                                                                                                                                                                               | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Eyball cross section .  Detailed retinal cells .  Schematic retinal cells .  Photo diode .  Photo diode layout .  PNP photo transistor .  Photo gate .  Amplification by drain resistance .  Logarithmic amplification .  Two transistor inverting amplifier .  Negative feedback .  Active pixel .  CCD .  AER photo pixel .  Adaptive photo cell .  Non linear element .                                                                                                                                                                                                             | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina                                                                                                                                                                                                                                    | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>93<br>94<br>95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

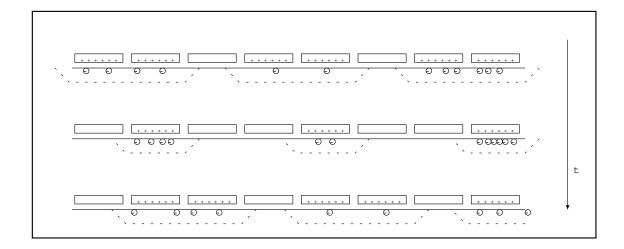

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina Boahen silicon retina                                                                                                                                                                                                              | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>93<br>94<br>95<br>96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

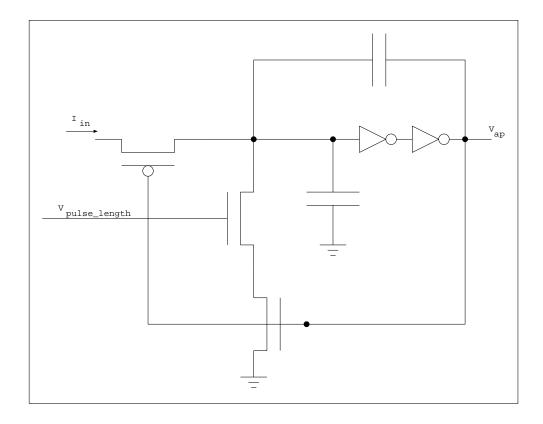

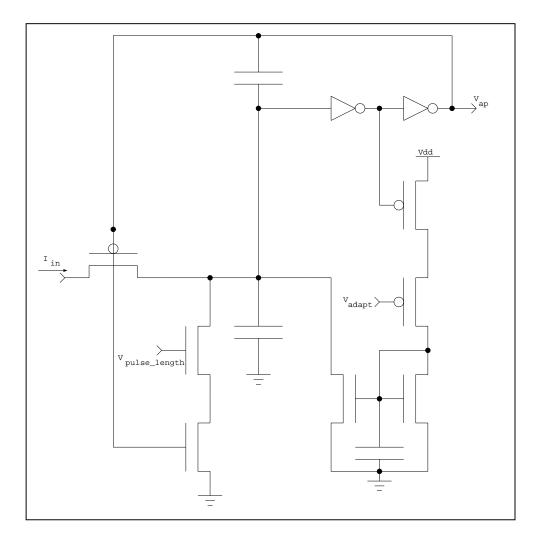

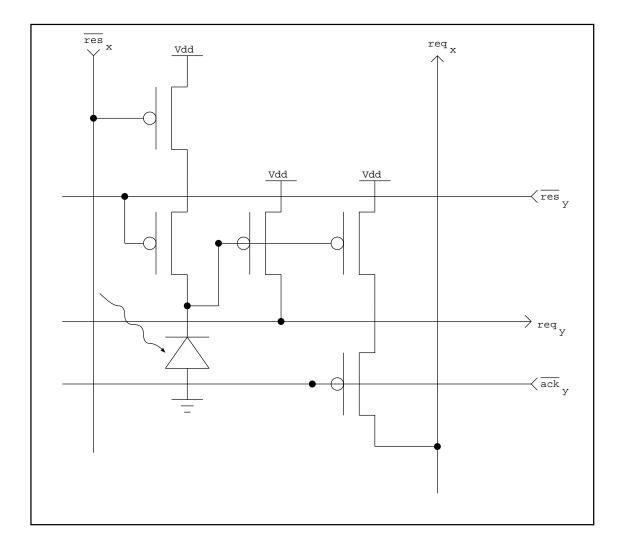

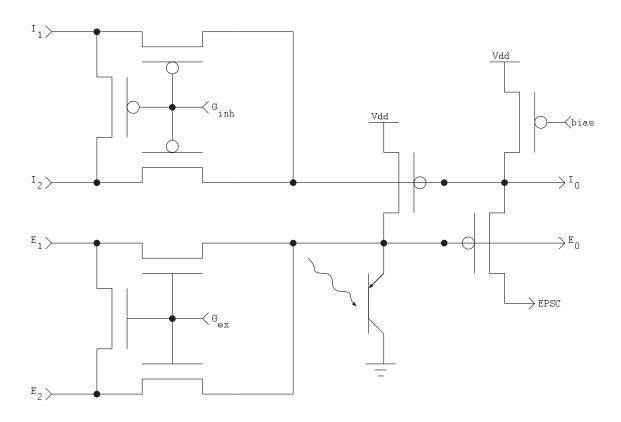

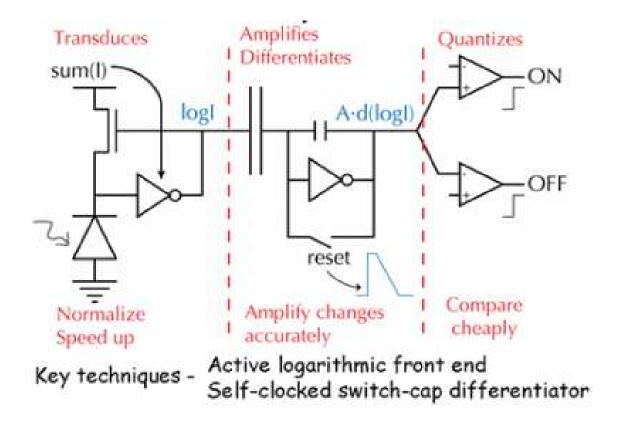

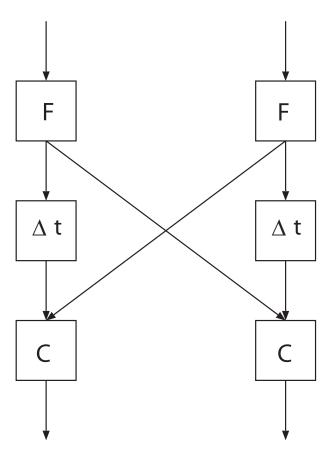

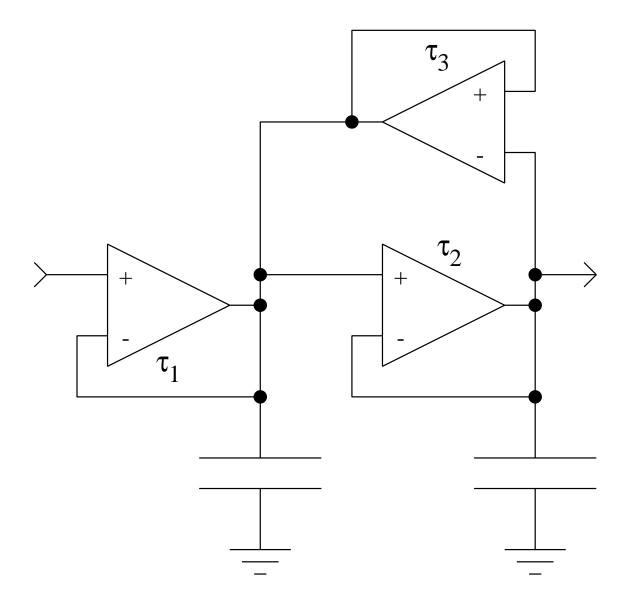

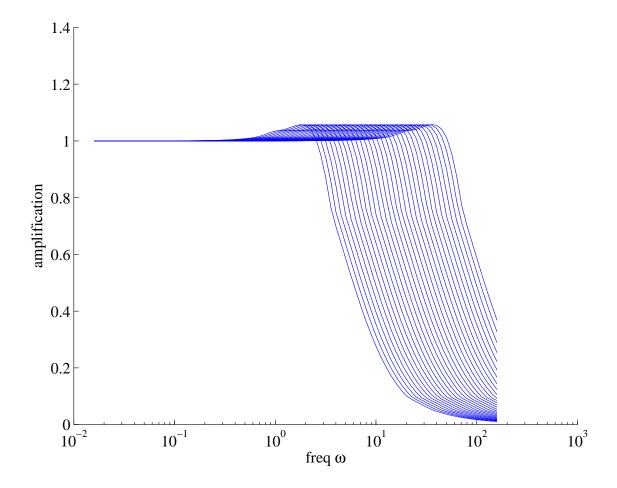

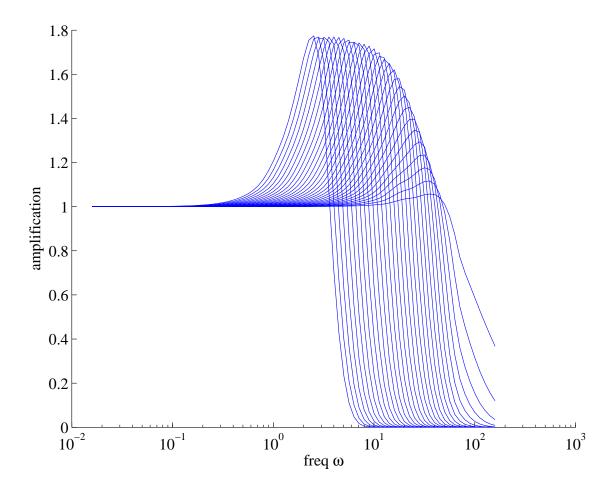

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina Boahen silicon retina Temporal contrast retina diagram                                                                                                                                                                             | 78 79 80 82 83 84 85 86 87 88 89 90 91 93 94 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

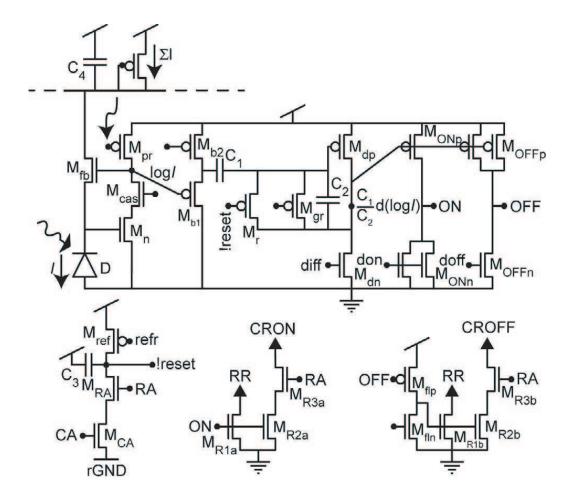

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina Boahen silicon retina Temporal contrast retina diagram Temporal contrast retina transistor level circuit                                                                                                                           | 78 79 80 82 83 84 85 86 87 88 89 90 91 93 94 95 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina Boahen silicon retina Temporal contrast retina diagram Temporal contrast retina transistor level circuit Reichardt detector                                                                                                        | 78 79 80 82 83 84 85 86 87 88 89 91 93 94 95 96 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

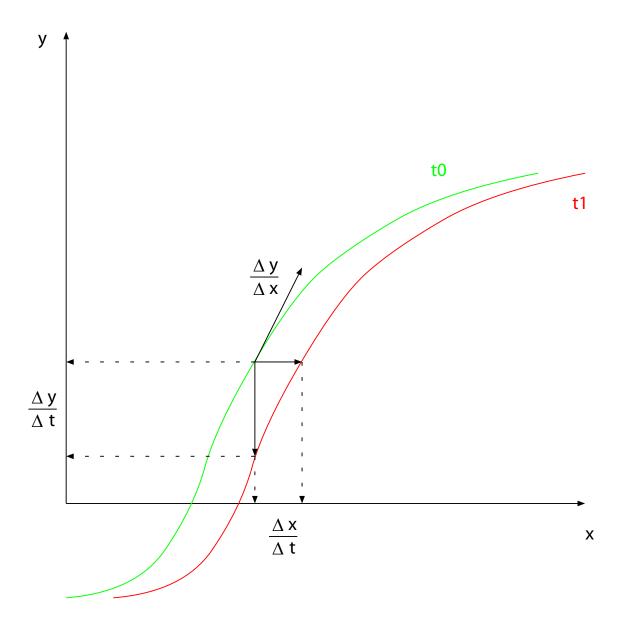

| Eyball cross section Detailed retinal cells Schematic retinal cells Photo diode Photo diode layout PNP photo transistor Photo gate Amplification by drain resistance Logarithmic amplification Two transistor inverting amplifier Negative feedback Active pixel CCD AER photo pixel Adaptive photo cell Non linear element Mahowald silicon retina Boahen silicon retina Temporal contrast retina diagram Temporal contrast retina transistor level circuit Reichardt detector Intensity based motion estimation                                                                      | 78<br>79<br>80<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>93<br>94<br>95<br>96<br>97<br>98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

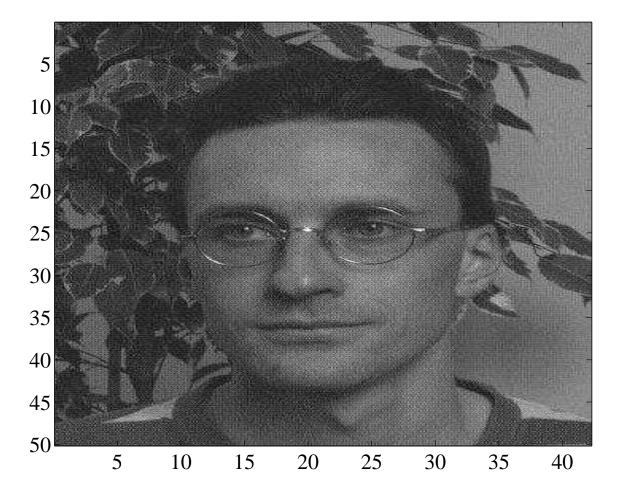

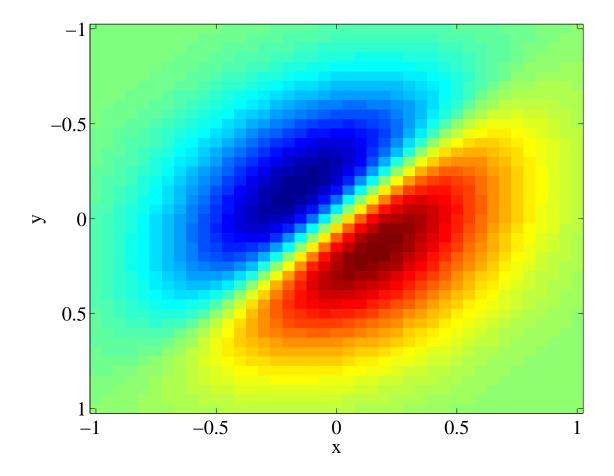

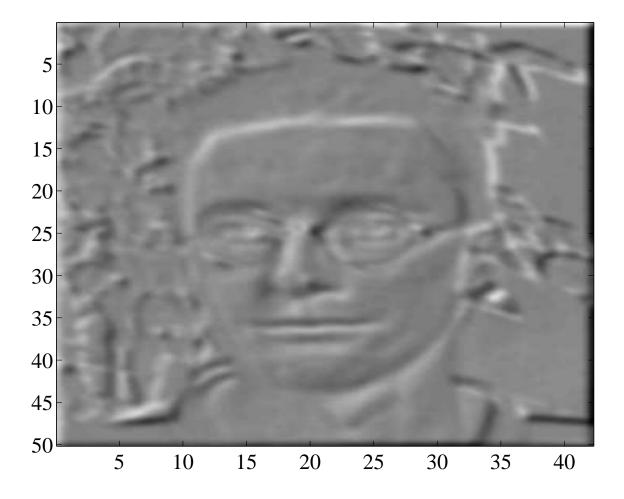

| Eyball cross section . Detailed retinal cells . Schematic retinal cells . Photo diode . Photo diode layout . PNP photo transistor . Photo gate . Amplification by drain resistance . Logarithmic amplification . Two transistor inverting amplifier . Negative feedback . Active pixel . CCD . AER photo pixel . Adaptive photo cell . Non linear element . Mahowald silicon retina . Boahen silicon retina . Temporal contrast retina diagram . Temporal contrast retina transistor level circuit . Reichardt detector . Intensity based motion estimation . Original natural scene . | 78 79 80 82 83 84 85 86 87 88 89 91 93 94 95 96 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |